### **EXPERIMENT 2**

# 2. Familiarizing With the FPGA Board and Tool

## 2.1 Objectives

- 1- Familiarize with FPGA board.

- 2- Familiarize with FPGA design steps & tools.

- 3- Binding inputs and outputs to certain switches and LEDs.

- 4- Derive & verify the  $2^n$ -rows T. table of the function.

### 2.2 Description

- Introduce FPGA (CLB's, Programmable IO Pads, Input Buffers, Output Buffers, Clock Pin, Clock buffer)

- FPGA design steps and tools.

- FPGA board (switches, push buttons, LEDs & power supply pins. 7-Seg, Display, etc.)

- Design tools: schematic capture, functional simulation, download configuration bits

- Given a 4-variable logic diagram of basic gates (which has several similar repeated sub-circuits), students should:

- o Derive/anticipate the truth-table of the output function

- o Draw the schematic diagram and simulate the function.

- o Implement the circuit and verify the truth-table

#### 2.3 Pre-lab

- Introduce FPGA (CLB's, Programmable IO Pads, Input Buffers, Output Buffers, Clock Pin, Clock buffer)

- Read the introductory section to get familiarized with the software.

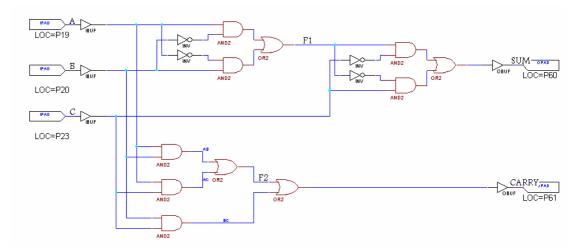

- Find the truth table for the circuit given in Figure 2.1 for the primary outputs and at the wires F1 and F2.

#### 2.4 In-lab

The lab requires you to go through all the stages of the design process using Xilinx and Digilab tools. You will be designing and functionally testing your design in Xilinx CAD software. Then you will verify your design on the board as well.

This being your first lab, the steps of the design are detailed as under. You may like to refer to lab guide for details on how to perform individual steps.

- Start the Xilinx project manager, configure the device and name the project as lab2.

- Create schematic for the lab.

- o Start by selecting a new schematic.

- o Add the symbols for the gates needed for the circuit in Figure 2.1

- o Place three input pads, IPAD, followed by input buffers, IBUF, and constrain them to three input switches (SW8, SW7 and SW6).

- o Place two output pads, OPAD, succeeded by output buffers, OBUF, and constrain them to two LEDs (LD8 and LD7).

- o Name the input and output nets. Your schematic would look like Figure 2.1

- o Perform an integrity test. Check to see if there are any errors or warnings and remove them.

- Design Simulation

- o Start the simulator and add the input/output signals

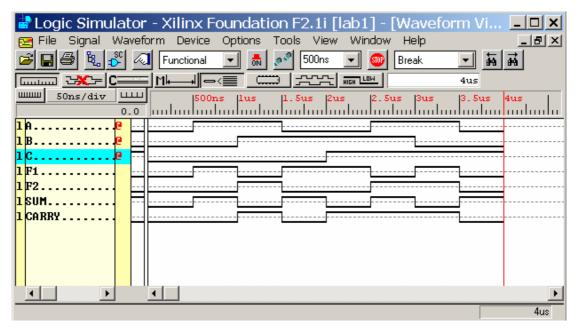

- o Assign counter the eight possible combinations and watch the signal at the primary outputs (SUM and CARRY) and at checkpoints F1, F2.

- o Simulate the design in steps as shown in Figure 2.2

- Verify functionality of the design.

- Implement the design

- o Download the design on Digilab board

- o Verification

Figure 2.1: Schematic Diagram

Figure 2.2: Simulation