#### Page 1 of 10

## King Fahd University of Petroleum and Minerals College of Computer Science and Engineering **Computer Engineering Department**

#### COE 202: Digital Logic Design (3-0-3) Term 171 (Fall 2017) **Final Exam** Monday, January 8<sup>th</sup>, 2018

#### Time: 120 minutes, Total Pages: 10

Name:\_\_\_\_\_ ID:\_\_\_\_\_

Section: \_\_\_\_\_

#### Notes:

Do not open the exam book until instructed

Calculators are not allowed (basic, advanced, cell phones, etc.)

Answer all questions

All steps must be shown

Any assumptions made must be clearly stated

| Question | Maximum Points | Your Points |

|----------|----------------|-------------|

| 1        | 25             |             |

| 2        | 10             |             |

| 3        | 15             |             |

| 4        | 12             |             |

| 5        | 8              |             |

| 6        | 10             |             |

| 7        | 15             |             |

| Total    | 95             |             |

#### Question 1:

- a) For a basic NOR SR latch the input SR = \_00\_\_ keeps the state of the latch unchanged, while the forbidden input is SR = 11\_\_\_\_\_ (2 points).

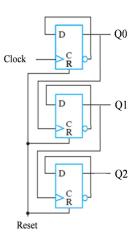

- b) The shown 3-bit binary counter counts upwards/downward (circle one). The counter has a maximum count of \_\_\_\_\_ and a minimum count of \_\_\_\_\_ (3 points).

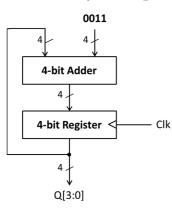

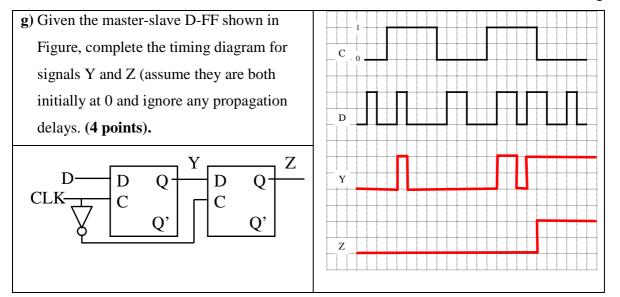

c) Given the following block diagram below:

If the output Q is 1 during the current cycle *t*, shown the output Q at (t+1) after 1 cycle, and at (t+2) after 2 cycles. (2 points)

| Q( <i>t</i> ) | Q( <i>t</i> +1) | Q( <i>t</i> +2) |

|---------------|-----------------|-----------------|

| 0001          | 0100 = 4        | 0111 = 7        |

Describe the function of the above circuit diagram: (1 points)

The above circuit is a counter that increments its output Q by 3 each cycle (modulo 16).

d) The 4-bit shift register shown was initially loaded with ABCD = 0100. List in the table below the contents of the register after receiving each of the clock pulses indicated. (2 points).

| Initial<br>After Clock Pulse 1<br>After Clock Pulse 2 | Register Contents         A B C D (Binary)         0 1 0 0         1 0 0 0         1 1 1 0 |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

|-------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

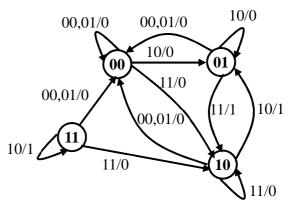

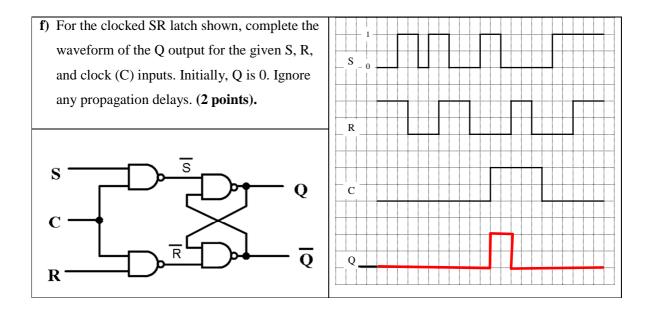

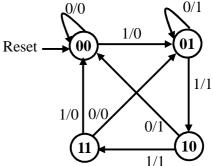

- e) A sequential circuit has two inputs; X and Y, and one output Z and the state diagram below:

- The synchronous reset input is \_X\_\_\_ (X or Y?) The circuit is reset when this input is High/Low (circle one) and the reset state is \_\_\_\_00\_\_\_\_ The unused state is \_\_\_\_11\_\_\_ (4 points)

- For the input sequence 00 then 11 then 11 then 10, the circuit would end up in state \_\_\_01\_\_ (1 point)

- h) Given a synchronous sequential circuit with 13 states, the minimum number of flip flops required to implement the circuit is \_\_\_\_\_\_ flip flops and the number of unused states is \_\_\_\_\_\_ states. (2 points)

- i) For a 5-bit synchronous binary counter with outputs Q4, Q3, Q2, Q1, and Q0 (where Q0 is the least-significant bit), if the clock frequency is 800 MHz then the frequency of Q2 is <u>100</u> MHz and the frequency of Q4 is <u>25</u> MHz. (2 points)

Page 5 of 10

#### [10 points]

# **Question 2.**

Draw the state diagram of a <u>Moore</u> synchronous sequential circuit that receives a serial input y and produces a serial output z. The output z should be 1 when the circuit detects the sequence **01100**. Overlapping sequences **are allowed**. A sample input/output trace after a reset is shown below:

| ſ | y  | 0 | 1 | 1 | 0 | 0 | 1                | 1 | 0 | 0 | 0                | 1 |   |

|---|----|---|---|---|---|---|------------------|---|---|---|------------------|---|---|

|   | Z. | 0 | 0 | 0 | 0 | 0 | $\mathbf{A}_{1}$ | 0 | 0 | 0 | $\mathbf{A}^{1}$ | 0 | 0 |

# **Solution:**

Page 6 of 10

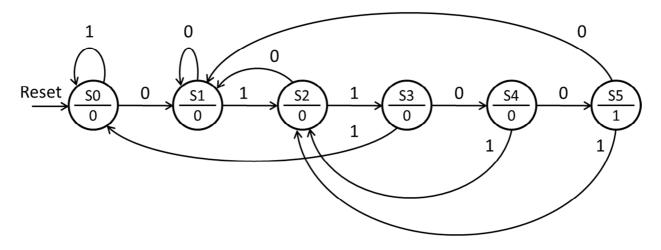

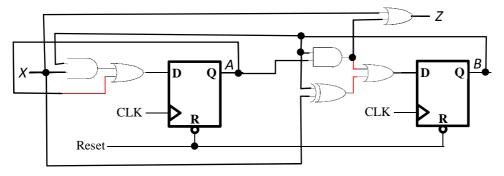

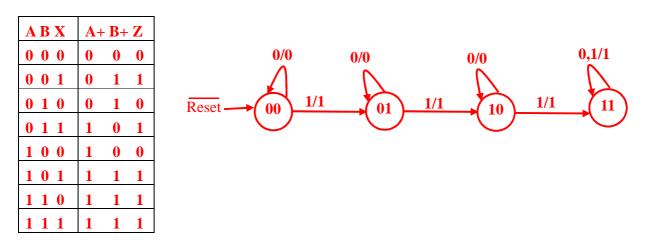

Question 3. A sequential circuit has one input x and one output z. and has the state diagram shown below.

[15 Points]

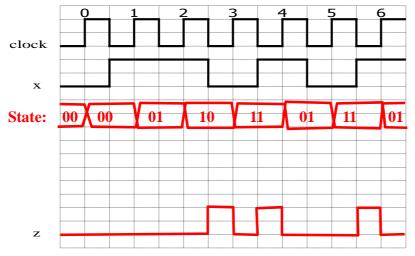

b) Using the timing diagram below, draw the output waveform *z*. Assume the circuit starts at state **00**. (5 points)

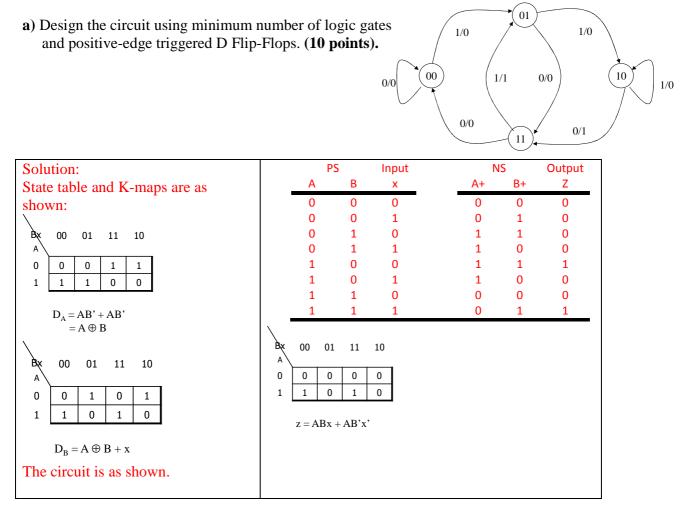

#### **Question 4.**

For the sequential circuit shown below:

1. Specify the <u>inputs</u>, <u>outputs</u>, <u>reset state</u>, and the <u>type</u> (Mealy or Moore). (2 points)

(9 points)

$\mathbf{Z} = \mathbf{X} + \mathbf{AB}$

inputs; X, reset, clk, outputs; Z, Reset state:00, circuit type: Mealy

2. Derive the state diagram of the circuit.

$\mathbf{B} + = \mathbf{B} \mathbf{XOR} \mathbf{X} + \mathbf{AB} \qquad \mathbf{A} + = \mathbf{A} + \mathbf{BX}$

Does this circuit has any unused states? Briefly explain your answer

No – All states can be reached using the circuit's inputs

(1 points)

Page 8 of 10

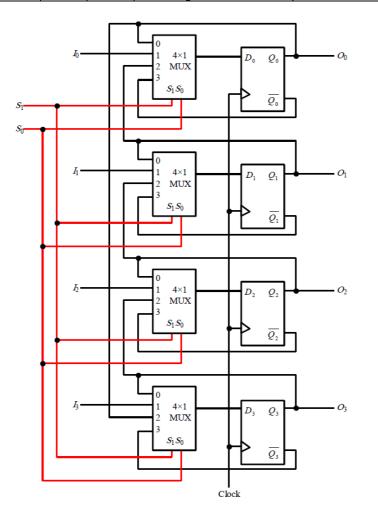

### Question 5. Label all your components, inputs, and outputs

[8 Points]

Using D flip-flop(s) and MUX(s) only (i.e., other components are not allowed), design a 4-bit register with mode selection inputs S1 and S0. The register should operate according to the following table:

| S1 | S0 | Function                                                                                                                                                          |

|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | No change                                                                                                                                                         |

| 0  | 1  | Parallel load (load inputs into register in parallel)                                                                                                             |

| 1  | 0  | Rotate Right (i.e., shift register contents to the right feeding in<br>the shifted bit out from the last bit location as a serial input to the<br>first location) |

| 1  | 1  | Load register with 1's complement of its current content                                                                                                          |

Page 9 of 10

#### [10 Points]

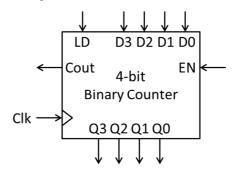

#### **Question 6.**

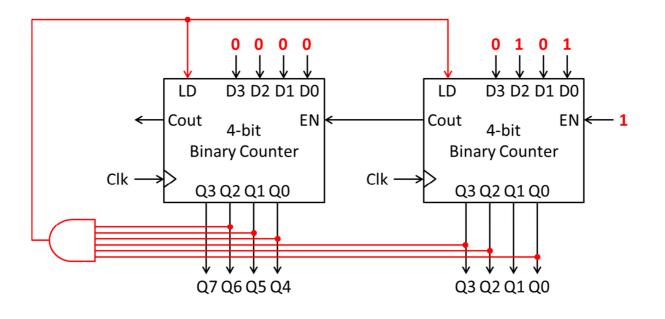

Use as many as you need of the 4-bit binary counter shown below (with the table explaining its operation) and minimal gates to design a counter that counts up from 5 to 125 in binary and then back to 5. Label properly the inputs and outputs of your designed counter.

| LD | EN | Operation of the counter |

|----|----|--------------------------|

| 0  | 0  | Hold count               |

| 0  | 1  | Increment count          |

| 1  | Х  | Parallel load            |

# **Solution:**

# 125 = 8'b0111\_1101

#### Question 7.

The state diagram below is for a sequential circuit that one input X (in addition to the asynchronous Reset) and one output Y. Write a <u>behavioral</u> Verilog description of this circuit. (10 points)

```

module FSM (input x, clk, reset, output y);

reg [1:0] state;

assign y = (state = 2'b01) | (state = 2'b10);

// this could also be simply written as

// assign y = (state==1) | (state==2);

always @(posedge clk, posedge reset)

if (reset) state<=0 ; //or state<= 2'b00

else case (state)

0: if (x) state \leq 1; //could be 2'b00: if (x) state \leq 2'b01;

1: if (x) state \leq 2;

2: if (x) state \leq 2;

else state \leq 0;

3: if (!x) state \leq 1;

else state <= 0:

endcase

endmodule

```

Write a <u>behavioral</u> Verilog description of a universal register that has three control inputs in addition to the clock input; Clr, LD, and Count, <u>and 4-bit input Din and output Q</u>, with the following functionality: <u>(the counter does not have asynchronous inputs)</u> (5 points)

| Clr | LD | Count | Functionality                                             |

|-----|----|-------|-----------------------------------------------------------|

| 0   | 0  | 0     | No change (i.e. Q stay the same)                          |

| 1   | Х  | Х     | Clear register no matter what LD and Count are (i.e. Q=0) |

| 0   | 1  | Х     | Load the register with Din (i.e. Q=Din)                   |

| 0   | 0  | 1     | Count up till Q=9, then go back to 0                      |

module cntr (input clr, LD, count, clk, input [3:0] Din, output reg [3:0] Q); always @(posedge clk) if (clr) Q<=0; //or Q<= 4'b0000 else if (LD) Q<= Din; else if (count) if (Q==9) Q<=0; //or if (Q==4'b1001) Q<= 4'b0000 else Q<=Q+1; endmodule Page 10 of 10

#### [15 Points]