# King Fahd University of Petroleum and Minerals

College of Computer Science and Engineering Computer Engineering Department

> COE 202: Digital Logic Design (3-0-3) Term 161 (Fall 2016) Final Exam Wednesday, December 11, 2017

Time: 120 minutes, Total Pages: 14

| Name:                       | ID:                                           | Section: |

|-----------------------------|-----------------------------------------------|----------|

|                             |                                               |          |

| Notes:                      |                                               |          |

| Do not open the exam book   | until instructed                              |          |

| Calculators are not allowed | <b>d</b> (basic, advanced, cell phones, etc.) |          |

| Answer all questions        | •                                             |          |

| All steps must be shown     |                                               |          |

| Any assumptions made mus    | t be clearly stated                           |          |

| Question | Maximum Points | Your Points |

|----------|----------------|-------------|

| 1        | 16             |             |

| 2        | 7              |             |

| 3        | 6              |             |

| 4        | 15             |             |

| 5        | 9              |             |

| 6        | 6              |             |

| 7        | 6              |             |

| 8        | 15             |             |

| 9        | 10             |             |

| Total | 90 |  |

|-------|----|--|

| Total | 90 |  |

#### **Question 1: Fill in the Spaces: (Show all work needed to obtain your answer)**

(16 points)

- 1. A high value to the two R and S inputs of the NAND-gate latch will No Change (Change/No Change) the state/output of the latch. (1 point)

- 2. Asynchronous reset to a flip flop doesn't depend on the clock input <u>True</u> (True/False). (1 point)

- Given a synchronous sequential circuit with 9 states, the minimum number of flip flops required to implement the circuit is \_\_4\_ flip flops and the number of unused states is \_\_7\_ states.

(2 points)

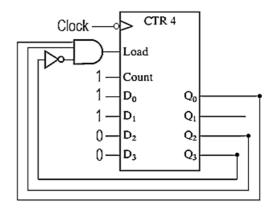

- 4. The following circuit shows a parallel load binary counter, the range of the counter is <u>3</u> to <u>5</u>. (2 points)

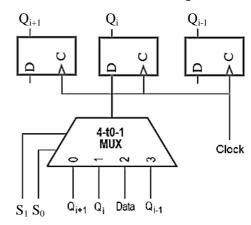

5. The below figure shows connections to the *D* input of stage *i* in a multi-function register of D-type flip flops. Study the circuit and fill in the missing information in the table below (empty slots) only for supported register functions. (2 points)

| S <sub>1</sub> S <sub>0</sub> | Register Function (where applicable) |

|-------------------------------|--------------------------------------|

| <u>00</u>                     | Shift right                          |

| ==                            | Clear register                       |

| <u>01</u>                     | No change in output                  |

| <u>10</u>                     | Load Data input                      |

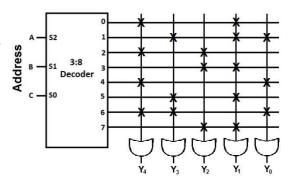

6. In the ROM circuit shown, **X** indicates a connection. At address ABC = 110, the ROM stores the data  $Y_4Y_3Y_2Y_1Y_0 = 11001$ . (1 point)

- 7. For a 4-bit synchronous binary counter (outputs Q<sub>3</sub>, Q<sub>2</sub>, Q<sub>1</sub> and Q<sub>0</sub>), with input clock frequency of 48 MHZ, the frequency of Q<sub>1</sub> is \_\_\_\_\_\_ MHZ and the frequency of Q<sub>3</sub> is \_\_\_\_\_\_ MHZ. (2 points)

- 8. Two RS level sensitive latches and one inverter are used to make an edge triggered flip flop which can be used to store up to two bits \_\_False\_\_ (True/False). (1 point)

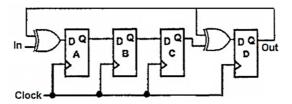

- 9. Consider the below 4-bit register. If the initial register contents (Q outputs) ABCD are 0111 and the serial input is kept at 1, show the contents ABCD = 1001 of the register after two clock pulses. (2 points)

- 10. A state machine with two inputs and three outputs will have \_\_\_\_\_4 (how many) arcs going out from each state to any other states. (1 point)

- 11. For any given problem/requirement, the number of states required by a Mealy machine or a Moore machine is always the same \_\_\_\_False\_\_\_ (True/False). (1 point)

Question 2: (7 points)

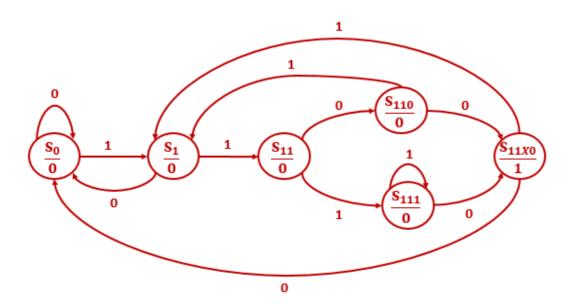

Derive the state diagram of a synchronous  $\underline{Moore}$  sequential circuit that receives a serial input Y and produces a serial output F that is set to  $\mathbf{1}$  when the circuit detects the sequence  $\mathbf{11X0}$ , where  $\mathbf{X}$  represents don't care.

Question 3: (6 points)

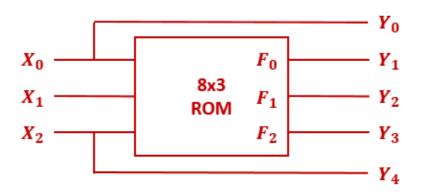

Design a combinational circuit using a ROM. The circuit accepts a 3-bit number  $X = X_2X_1X_0$  and generates an output binary number Y equal to 3X + 4. The ROM should contain a minimum number of columns. Fill the truth table and ROM table below and draw the block diagram.

**Truth Table**

| I              | nput.          | s              |                       | 0                     | utpu           | ts                    |                       |

|----------------|----------------|----------------|-----------------------|-----------------------|----------------|-----------------------|-----------------------|

| X <sub>2</sub> | X <sub>1</sub> | X <sub>0</sub> | <b>Y</b> <sub>4</sub> | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | <b>Y</b> <sub>1</sub> | <b>Y</b> <sub>0</sub> |

| 0              | 0              | 0              | 0                     | 0                     | 1              | 0                     | 0                     |

| 0              | 0              | 1              | 0                     | 0                     | 1              | 1                     | 1                     |

| 0              | 1              | 0              | 0                     | 1                     | 0              | 1                     | 0                     |

| 0              | 1              | 1              | 0                     | 1                     | 1              | 0                     | 1                     |

| 1              | 0              | 0              | 1                     | 0                     | 0              | 0                     | 0                     |

| 1              | 0              | 1              | 1                     | 0                     | 0              | 1                     | 1                     |

| 1              | 1              | 0              | 1                     | 0                     | 1              | 1                     | 0                     |

| 1              | 1              | 1              | 1                     | 1                     | 0              | 0                     | 1                     |

**ROM Table**

| ı              | nputs          | S              | C              | Output         | :s             |

|----------------|----------------|----------------|----------------|----------------|----------------|

| X <sub>2</sub> | X <sub>1</sub> | X <sub>0</sub> | F <sub>2</sub> | F <sub>1</sub> | F <sub>0</sub> |

| 0              | 0              | 0              | 0              | 1              | 0              |

| 0              | 0              | 1              | 0              | 1              | 1              |

| 0              | 1              | 0              | 1              | 0              | 1              |

| 0              | 1              | 1              | 1              | 1              | 0              |

| 1              | 0              | 0              | 0              | 0              | 0              |

| 1              | 0              | 1              | 0              | 0              | 1              |

| 1              | 1              | 0              | 0              | 1              | 1              |

| 1              | 1              | 1              | 1              | 0              | 0              |

**Block Diagram**

Question 4: (15 points)

Given the following state table:

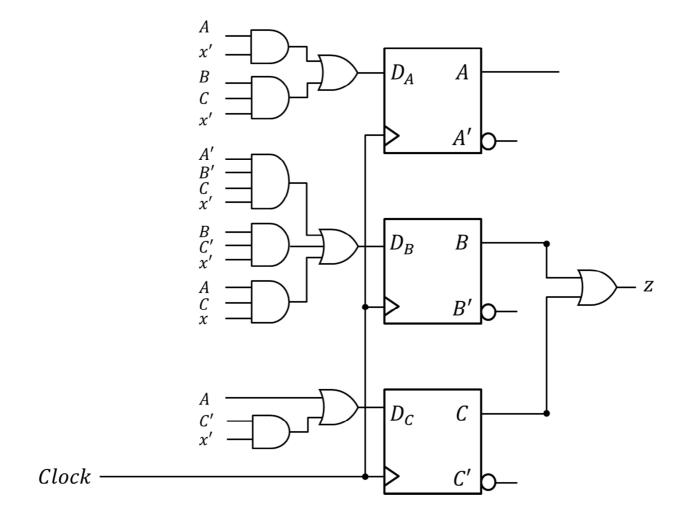

a) Obtain minimal sum-of-products equations for the next state and output. (12 points)

b) Draw the circuit diagram. (3 points)

| Present<br>State | Next  | Next State |   |  |  |  |

|------------------|-------|------------|---|--|--|--|

| АВС              | x = 0 | x = 1      | Z |  |  |  |

| 000              | 001   | 000        | 0 |  |  |  |

| 001              | 010   | 000        | 1 |  |  |  |

| 010              | 0 1 1 | 000        | 1 |  |  |  |

| 0 1 1            | 100   | 000        | 1 |  |  |  |

| 100              | 101   | 001        | 0 |  |  |  |

| 1 0 1            | 1 0 1 | 0 1 1      | 1 |  |  |  |

#### Part a)

## **Solution1: Using Don't Care for the unused states**

|   |   | K-  | -Мар | for | D <sub>A</sub> | K-  | K-Map for D <sub>B</sub> |     |     | K-Map for D <sub>c</sub> |     |     | K-Map | for z |     |

|---|---|-----|------|-----|----------------|-----|--------------------------|-----|-----|--------------------------|-----|-----|-------|-------|-----|

|   |   |     | С    | X   |                |     | Сх                       |     |     | Сх                       |     |     | (     |       |     |

| Α | В | 0 0 | 0 1  | 1 1 | 1 0            | 0 0 | 0 1                      | 1 1 | 1 0 | 0 0                      | 0 1 | 1 1 | 1 0   | C=0   | C=1 |

| 0 | 0 |     |      |     |                |     |                          |     | 1   | 1                        |     |     |       |       | 1   |

| 0 | 1 |     |      |     | 1              | 1   |                          |     |     | 1                        |     |     |       | 1     | 1   |

| 1 | 1 | X   | X    | X   | X              | X   | X                        | X   | X   | X                        | X   | X   | X     | X     | X   |

| 1 | 0 | 1   |      |     | 1              |     |                          | 1   |     | 1                        | 1   | 1   | 1     |       | 1   |

$$D_A = A x' + B C x'$$

$D_B = B C' x' + A C x + A' B' C x'$   $D_C = A + C' x'$   $Z = B + C$

### Solution2: Forcing transition from the unused states to state 000

|   |   | K-  | -Мар | for | D <sub>A</sub> | K-  | K-Map for D <sub>B</sub> |     |     | K.  | $K$ -Map for $D_C$ |     |     | K-Map | for z |

|---|---|-----|------|-----|----------------|-----|--------------------------|-----|-----|-----|--------------------|-----|-----|-------|-------|

|   |   |     | C    | X   |                |     | C x                      |     |     | Сx  |                    |     | (   |       |       |

| Α | В | 0 0 | 0 1  | 1 1 | 1 0            | 0 0 | 0 1                      | 1 1 | 1 0 | 0 0 | 0 1                | 1 1 | 1 0 | C=0   | C=1   |

| 0 | 0 |     |      |     |                |     |                          |     | 1   | 1   |                    |     |     |       | 1     |

| 0 | 1 |     |      |     | 1              | 1   |                          |     |     | 1   |                    |     |     | 1     | 1     |

| 1 | 1 |     |      |     |                |     |                          |     |     |     |                    |     |     | X     | X     |

| 1 | 0 | 1   |      |     | 1              |     |                          | 1   |     | 1   | 1                  | 1   | 1   |       | 1     |

$$D_A = A B' x' + A' B C x'$$

$D_B = A' B C' x' + A B' C x + A' B' C x'$   $D_C = A B' + A' C' x'$   $z = B + C$

## Part b) Circuit Diagram for Solution 1

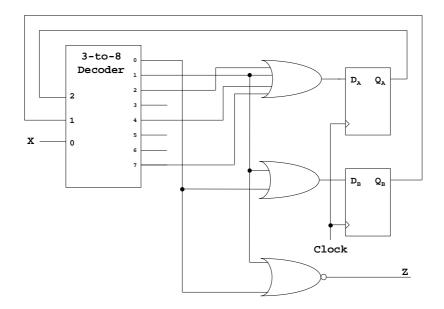

**Question 5:** Consider the following sequential circuit:

a) Provide a state table for the given circuit showing the Present State, the input X, the Next State, and the output Z.

(8 points)

$$D_A = \sum m(1, 2, 4, 7), \quad D_B = \sum m(0, 1), \quad Z = \prod M(0, 1)$$

| $Q_A$ | $Q_B$ | X | $Q_A^+$ | $Q_B^+$ | $\boldsymbol{Z}$ |

|-------|-------|---|---------|---------|------------------|

| 0     | 0     | 0 | 0       | 1       | 0                |

| 0     | 0     | 1 | 1       | 1       | 0                |

| 0     | 1     | 0 | 1       | 0       | 1                |

| 0     | 1     | 1 | 0       | 0       | 1                |

| 1     | 0     | 0 | 1       | 0       | 1                |

| 1     | 0     | 1 | 0       | 0       | 1                |

| 1     | 1     | 0 | 0       | 0       | 1                |

| 1     | 1     | 1 | 1       | 0       | 1                |

**b)** Is the circuit type *Mealy* or *Moore*? Justify your answer.

(1 point)

Moore since  $Z = \Pi M(0,1) = (Q_A + Q_B + X)(Q_A + Q_B + X') = Q_A + Q_B$  which is a function of the present states only. This is also clear from the state table obtained in part (a).

Question 6: (6 points)

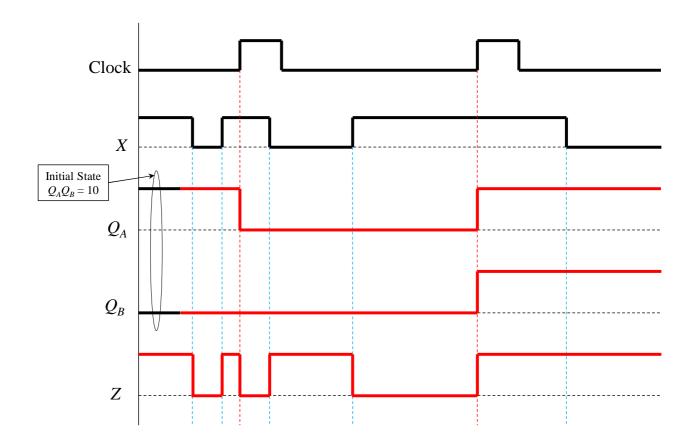

Consider the following state table. Assume that the initial state of the circuit implementation of the given state table is  $(Q_AQ_B = 10)$ . Draw the waveforms of  $Q_A$ ,  $Q_B$ , and Z for the given 2 clock cycles in response to the shown applied input X. Ignore propagation delays, setup times, and hold times. Assume that the circuit uses <u>rising</u> edge-triggered D-FF(s).

| Presen | t State | X | Next  | State | Z |

|--------|---------|---|-------|-------|---|

| $Q_A$  | $Q_B$   | Λ | $D_A$ | $D_B$ | Z |

| 0      | 0       | 0 | 0     | 1     | 1 |

| 0      | 0       | 1 | 1     | 1     | 0 |

| 0      | 1       | 0 | 1     | 0     | 0 |

| 0      | 1       | 1 | 0     | 0     | 0 |

| 1      | 0       | 0 | 1     | 0     | 0 |

| 1      | 0       | 1 | 0     | 0     | 1 |

| 1      | 1       | 0 | 0     | 0     | 1 |

| 1      | 1       | 1 | 1     | 0     | 1 |

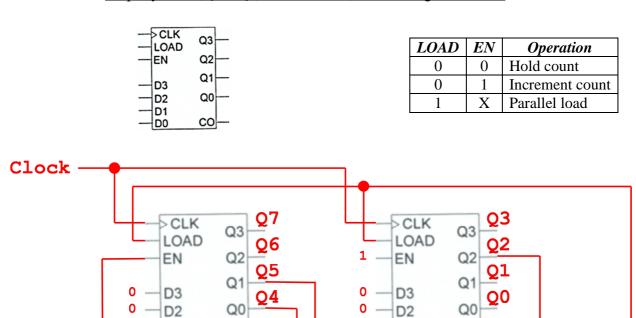

Question 7: (6 points)

Use minimal external gates and as many of the following counter as necessary to design a counter that counts from 1 to 52 and then repeats. Note that the operation of the provided counter is according to the table to the right of the counter. Note also that CO stands for Carry-output which gets set to 1 when the maximum count of 15 is reached. Assume that the counter is initially loaded with the value 1. Properly label (Q0 - Q7) and (D0 - D7) of the designed counter.

D1

D0

CO

0

D1

D0

CO

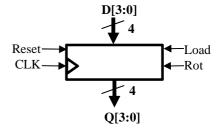

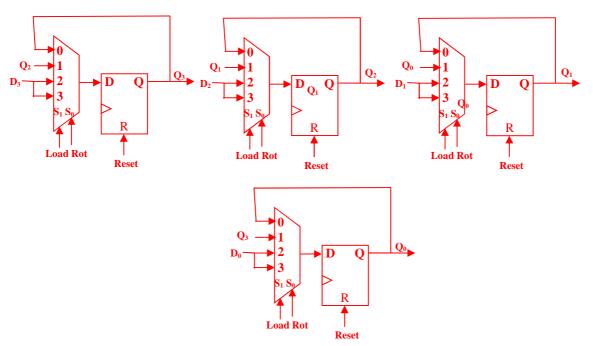

Question 8: (15 points)

Using D-FFs and any other components, design a 4-bit rotator register with direct asynchronous reset that has two control inputs; Load and Rot with the functionality shown in the table below:

| Reset | Load | Rot | Function                               |  |

|-------|------|-----|----------------------------------------|--|

| 0     | 0    | 0   | No Change (Q stay as is)               |  |

| 1     | Х    | Χ   | asynchronous reset: Q = 0              |  |

| 0     | 1    | Χ   | Load: Q = D                            |  |

| 0     | 0    | 1   | Rotate Left: Q3=Q2, Q2=Q1,Q1=Q0, Q0=Q3 |  |

a) Draw the circuit diagram

(5 points)

b) Write a <u>behavioral</u> Verilog description of the above rotator register (6 points) module rotator4 (input [3:0] D, reset, clk, load, rot, output reg [3:0] Q);

```

always @ (posedge clk, posedge reset)

if (reset) Q<= 0 ;

elseif (load) Q<=D ;

else if (rot) Q <= {Q[2:0],Q[3]} ;

endmodule</pre>

```

c) Write a test bench to test the above rotator register. Let the clock cycle = 20 time units. First, reset the register, then load the register with 1010, then do nothing for two clock cycles, then rotate the register 3 times.

(4 points)

```

module tb_rot ();

wire [3:0] Q ;

reg [3:0] D ;

```

```

reg clk, reset, load, rot;

rotator ml (D, reset, clk, load, rot, Q);

initial begin

/reset and clock sequence

reset = 1; clk=0;

#5 reset =0 ; forever #10 clk=~clk;

end

initial begin

D = 4'b1010

//or D=10 .. initialize inputs

load=0 ;

rot=0

(negedge clk) load= 1

//load the register with 1010

(negedge clk) load= 1

//deactivate the load signal - one clock cycle after load - do nothing

(negedge clk)

//another clock cycle after load- do nothing

//I^{st} rotation

(negedge clk) rot=1

(negedge clk)

//2nd rotation, rot signal remains 1

(negedge clk)

//3rd rotation,rot signal remains 1

end

endmodule

```

Question 9: (10 points)

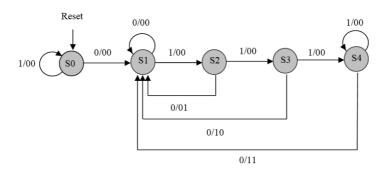

a) Write a <u>behavioral</u> Verilog description of a sequential circuit with the state diagram below. The circuit has an asynchronous **Reset** input, one input X, and two outputs: Y and Z. Use the following state encodings: S0=000, S1=001, S2=010, S3=100, S4=111. If the circuit ever gets into any of the unused states, it will go to state S0 no matter what the input value is. (6 points)

```

module Mealy fsm (output wire y,z, input x, clk, reset );

localparam SO = 2'b000, S1=2'b001, S2=2'b010, S3=2'b011, S4=100;

//symbolic names for state values

reg [2:0] state; //state register

assign y = ((state = s3) | (state = s4))  x : //y = 1 only if we are in state S3 or state S4, and x is 0

assign z = ((state = s2) | (state = s4)) & \sim x ; //y = 1 only if we are in state S2 or state S4, and x is D

always @(posedge clk, posedge reset) //This is only for the state transition

if (reset) state <= $0;

else case (state)

SO: if (!x) state <= S1 ;

//if x=1, state remain at SO

S1: if (x) state <= S2

//if x=0, state remain at SO

S2: if (x) state \leq S3 ; else state \leq S1;

S3: if (x) state \leq S4 ; else state \leq S1;

S4: if (!x) state \le S1 ; else state \le S1;

default: state <= $0

//all non-used states oo to SO

endcase

```

endmodule

b) Write a test bench to test the circuit. Let the clock cycle = 20 time units. First, reset the circuit, then apply the following input sequence to **X**: **0**, **1**, **0**, **1**, **1**, **1**, **0**. (4 points)

```

module tb fsm ();

wire y,z ;

clk, reset,x;

reg

Mealy_fsm ml (y, z, x, clk, reset );

initial begin

/reset and clock sequence

reset = 1; clk=0;

#5 reset =0 ; forever #10 clk=~clk;

initial begin

//1^{st} input bit x=0

x=[]

(negedge clk) x=1

//2nd input bit x=1

\square (negedge clk) x=\square

//3rd input bit x=0

@ (negedge clk) x=1

//4th input bit x=1

(negedge clk)

//5th input bit, x remain 1

(negedge clk)

//6th input bit, x remain 1

\square (negedge clk) x=\square

//7th input bit x=0

end

endmodule

```