## King Fahd University of Petroleum and Minerals

College of Computer Science and Engineering Computer Engineering Department

> COE 202: Digital Logic Design (3-0-3) Term 161 (Fall 2016) Final Exam Wednesday, December 11, 2017

Time: 120 minutes, Total Pages: 14

| Name:                       | ID:                                           | Section: |

|-----------------------------|-----------------------------------------------|----------|

|                             |                                               |          |

| Notes:                      |                                               |          |

| Do not open the exam book   | until instructed                              |          |

| Calculators are not allowed | <b>d</b> (basic, advanced, cell phones, etc.) |          |

| Answer all questions        | •                                             |          |

| All steps must be shown     |                                               |          |

| Any assumptions made mus    | t be clearly stated                           |          |

| Question | Maximum Points | Your Points |

|----------|----------------|-------------|

| 1        | 16             |             |

| 2        | 7              |             |

| 3        | 6              |             |

| 4        | 15             |             |

| 5        | 9              |             |

| 6        | 6              |             |

| 7        | 6              |             |

| 8        | 15             |             |

| 9        | 10             |             |

| Total | 90 |  |

|-------|----|--|

| Total | 90 |  |

## **Question 1: Fill in the Spaces: (Show all work needed to obtain your answer)**

(16 points)

- 1. A high value to the two R and S inputs of the NAND-gate latch will (Change/No Change) the state/output of the latch. (1 point)

- Asynchronous reset to a flip flop doesn't depend on the clock input \_\_\_\_\_\_ (True/False).

(1 point)

- 3. Given a synchronous sequential circuit with 9 states, the minimum number of flip flops required to implement the circuit is \_\_\_\_\_ flip flops and the number of unused states is \_\_\_\_\_ states. (2 points)

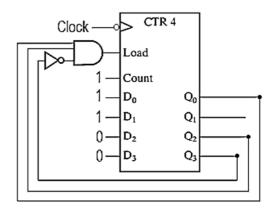

- 4. The following circuit shows a parallel load binary counter, the range of the counter is \_\_\_\_\_ to \_\_\_\_. (2 points)

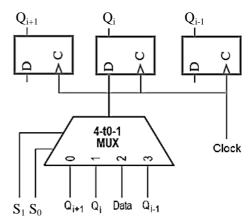

5. The below figure shows connections to the *D* input of stage *i* in a multi-function register of D-type flip flops. Study the circuit and fill in the missing information in the table below (empty slots) only for supported register functions. (2 points)

| S <sub>1</sub> S <sub>0</sub> | Register Function (where applicable) |

|-------------------------------|--------------------------------------|

|                               | Shift right                          |

|                               | Clear register                       |

|                               | No change in output                  |

|                               | Load Data input                      |

- 7. For a 4-bit synchronous binary counter (outputs Q<sub>3</sub>, Q<sub>2</sub>, Q<sub>1</sub> and Q<sub>0</sub>), with input clock frequency of 48 MHZ, the frequency of Q<sub>1</sub> is \_\_\_\_\_\_ MHZ and the frequency of Q<sub>3</sub> is \_\_\_\_\_ MHZ. (2 points)

- 8. Two RS level sensitive latches and one inverter are used to make an edge triggered flip flop which can be used to store up to two bits \_\_\_\_\_ (True/False). (1 point)

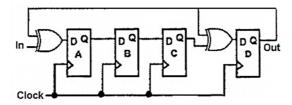

- 9. Consider the below 4-bit register. If the initial register contents (Q outputs) *ABCD* are *0111* and the serial input is kept at 1, show the contents *ABCD* = \_\_\_\_\_ of the register after two clock pulses. (2 points)

- 10. A state machine with two inputs and three outputs will have \_\_\_\_\_ (how many) arcs going out from each state to any other states. (1 point)

- 11. For any given problem/requirement, the number of states required by a Mealy machine or a Moore machine is always the same \_\_\_\_\_ (True/False). (1 point)

Question 2: (7 points)

Derive the state diagram of a synchronous  $\underline{Moore}$  sequential circuit that receives a serial input Y and produces a serial output F that is set to  $\mathbf{1}$  when the circuit detects the sequence  $\mathbf{11X0}$ , where  $\mathbf{X}$  represents don't care.

Question 3: (6 points)

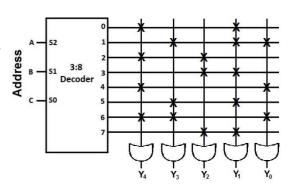

Design a combinational circuit using a ROM. The circuit accepts a 3-bit number  $X = X_2X_1X_0$  and generates an output binary number Y equal to 3X + 4. The ROM should contain a minimum number of columns. Fill the truth table and ROM table below and draw the block diagram.

| Truth Table |  | ROM ' | <b>Table</b> |

|-------------|--|-------|--------------|

|             |  |       |              |

|             |  |       |              |

|             |  |       |              |

|             |  |       |              |

|             |  |       |              |

|             |  |       |              |

|             |  |       |              |

|             |  |       |              |

|             |  |       |              |

|             |  |       |              |

## Question 4: (15 points)

Given the following state table:

a) Obtain minimal sum-of-products equations for the next state and output.

(12 points)

**b)** Draw the circuit diagram.

(3 points)

| Present<br>State | Next  | Output |   |

|------------------|-------|--------|---|

| АВС              | x = 0 | x = 1  | Z |

| 000              | 001   | 000    | 0 |

| 001              | 010   | 000    | 1 |

| 010              | 0 1 1 | 000    | 1 |

| 0 1 1            | 100   | 000    | 1 |

| 100              | 101   | 001    | 0 |

| 1 0 1            | 101   | 0 1 1  | 1 |

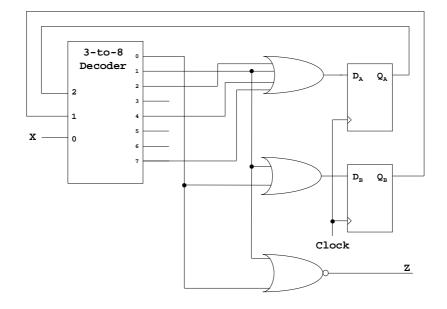

**Question 5:** Consider the following sequential circuit:

| a) | Next State, (8 points) |

|----|------------------------|

|    |                        |

|    |                        |

|    |                        |

| _  |                        |

|    |                        |

|    |                        |

|    |                        |

|    |                        |

|    |                        |

|    |                        |

|    |                        |

|    |                        |

**b)** Is the circuit type *Mealy* or *Moore*? Justify your answer.

(1 point)

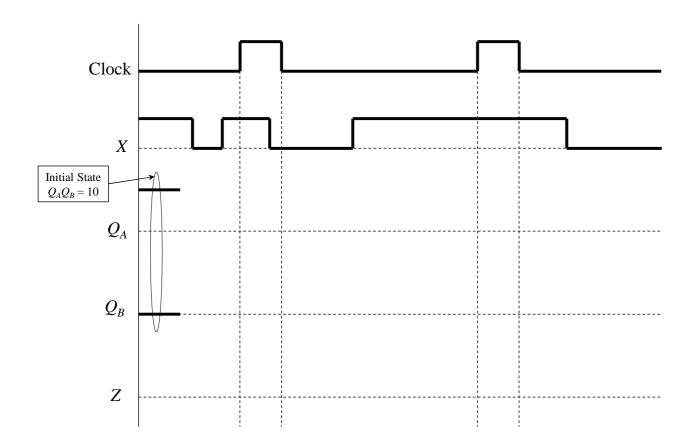

Question 6: (6 points)

Consider the following state table. Assume that the initial state of the circuit implementation of the given state table is  $(Q_AQ_B = 10)$ . Draw the waveforms of  $Q_A$ ,  $Q_B$ , and Z for the given 2 clock cycles in response to the shown applied input X. Ignore propagation delays, setup times, and hold times. Assume that the circuit uses rising edge-triggered D-FF(s).

| Present State |       | X | Next State |       | Z |

|---------------|-------|---|------------|-------|---|

| $Q_A$         | $Q_B$ | Λ | $D_A$      | $D_B$ | L |

| 0             | 0     | 0 | 0          | 1     | 1 |

| 0             | 0     | 1 | 1          | 1     | 0 |

| 0             | 1     | 0 | 1          | 0     | 0 |

| 0             | 1     | 1 | 0          | 0     | 0 |

| 1             | 0     | 0 | 1          | 0     | 0 |

| 1             | 0     | 1 | 0          | 0     | 1 |

| 1             | 1     | 0 | 0          | 0     | 1 |

| 1             | 1     | 1 | 1          | 0     | 1 |

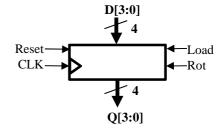

Question 7: (6 points)

Use minimal external gates and as many of the following counter as necessary to design a counter that counts from 1 to 52 and then repeats. Note that the operation of the provided counter is according to the table to the right of the counter. Note also that CO stands for Carry-output which gets set to 1 when the maximum count of 15 is reached. Assume that the counter is initially loaded with the value 1. Properly label (Q0 - Q7) and (D0 - D7) of the designed counter.

| - CLK<br>- LOAD | Q3 — |

|-----------------|------|

| -EN             | Q2   |

| D3              | Q1   |

| -D2             | Q0 - |

| D1<br>D0        | co-  |

| LOAD | EN | Operation       |

|------|----|-----------------|

| 0    | 0  | Hold count      |

| 0    | 1  | Increment count |

| 1    | X  | Parallel load   |

.

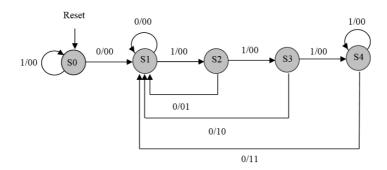

Question 8: (15 points)

Using D-FFs and any other components, design a 4-bit rotator register with direct asynchronous reset that has two control inputs; Load and Rot with the functionality shown in the table below:

| Reset | Load | Rot | Function                               |

|-------|------|-----|----------------------------------------|

| 0     | 0    | 0   | No Change (Q stay as is)               |

| 1     | Х    | Χ   | asynchronous reset: Q = 0              |

| 0     | 1    | Χ   | Load: Q = D                            |

| 0     | 0    | 1   | Rotate Left: Q3=Q2, Q2=Q1,Q1=Q0, Q0=Q3 |

a) Draw the circuit diagram

(5 points)

b) Write a **behavioral** Verilog description of the above rotator register

(6 points)

c) Write a test bench to test the above rotator register. Let the clock cycle = 20 time units. First, reset the register, then load the register with **1010**, then do nothing for two clock cycles, then rotate the register **3** times. (**4 points**)

Question 9: (10 points)

a) Write a <u>behavioral</u> Verilog description of a sequential circuit with the state diagram below. The circuit has an asynchronous **Reset** input, one input X, and two outputs: Y and Z. Use the following state encodings: S0=000, S1=001, S2=010, S3=100, S4=111. If the circuit ever gets into any of the unused states, it will go to state S0 no matter what the input value is. (6 points)

b) Write a test bench to test the circuit. Let the clock cycle = 20 time units. First, reset the circuit, then apply the following input sequence to **X**: **0**, **1**, **0**, **1**, **1**, **1**, **0**. (4 points)