# King Fahd University of Petroleum and Minerals

College of Computer Science and Engineering Computer Engineering Department

> COE 202: Digital Logic Design (3-0-3) Term 161 (Fall 2016) Major Exam 2 Saturday, Dec. 3rd, 2016

Time: 120 minutes, Total Pages: 11

| Name:                                | ID:                             | Section:     |

|--------------------------------------|---------------------------------|--------------|

|                                      |                                 |              |

| Notes:                               |                                 |              |

| Do not open the exam book until inst | ructed                          |              |

| Calculators are not allowed (be      | asic, advanced, cell phones, et | <i>cc.</i> ) |

| Answer all questions                 | •                               |              |

| All steps must be shown              |                                 |              |

| Any assumptions made must be clear   | ly stated                       |              |

| Question | Maximum Points | Your Points |

|----------|----------------|-------------|

| 1        | 14             |             |

| 2        | 16             |             |

| 3        | 20             |             |

| 4        | 6              |             |

| 5        | 14             |             |

| 6        | 20             |             |

| 7        | 20             |             |

| Total    | 110            |             |

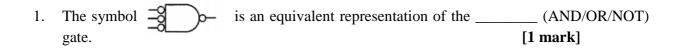

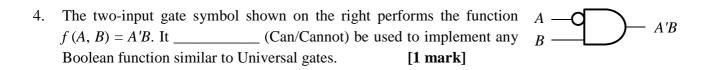

#### **Question 1: Fill in the Spaces: (Show all work needed to obtain your answer)**

[14 marks]

6. Using 6-bit 2's complement representation, the largest number that can be added to +5 without causing an overflow is \_\_\_\_\_ (in decimal). [1 mark]

| 8. | For the func | tion F(X, | Y, Z) re | presented | d in the follow | ing K-  | -map, | F has |

|----|--------------|-----------|----------|-----------|-----------------|---------|-------|-------|

|    |              | (How      | many)    | prime     | implicants,     | and     | of    | these |

|    |              |           | (How m   | any) are  | essential primo | e impli | cants | of F. |

|    | [2 marks]    |           |          |           |                 |         |       |       |

| X 0 | 0 01 | 11 | 10 |

|-----|------|----|----|

| 0   |      | 1  | 1  |

| 1   | 1    | 1  | Г  |

| 9. | The largest   | decoder | we can | build | using  | five | 2-to-4 | decoders | with    | Enable | without | any |

|----|---------------|---------|--------|-------|--------|------|--------|----------|---------|--------|---------|-----|

|    | additional co | to      | )      | _ dec | coder. |      |        |          | [1 mark | ]      |         |     |

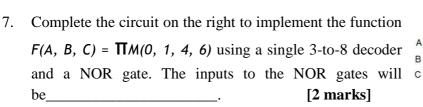

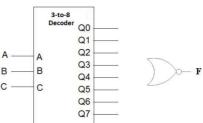

- 10. In the priority encoder shown below with  $\underline{\mathbf{D_0}}$  having highest priority and  $\underline{\mathbf{D_7}}$  the lowest priority, the output  $Y_2Y_1Y_0 = 101$  when the status at inputs  $D_0$ - $D_7$  is as described in \_\_\_\_\_\_ (select one of I, II, III, or IV) with all other inputs being in a don't care condition. [2 marks]

- I.  $D_0 = 1$  and  $D_2 = 1$ .

- II.  $D_1 = 1$  and  $D_2 = 1$ .

- III.  $D_3 = 1$  and  $D_5 = 1$ .

- IV.  $D_6 = 1$  and  $D_5 = 1$ .

### Question 2.

1) Consider the Boolean function  $F(W, X, Y, Z) = \prod M(1, 4, 6, 9) + \sum d(0, 3, 5, 7, 11, 12, 14)$ . Identify **all** the *prime implicants* and the *essential prime implicants* of **F.** [6 marks]

2) Simplify the Boolean function **F**(**w**,**x**,**y**,**z**) shown in the K-map below together with its don't care conditions, into *minimal* <u>sum-of-products</u> expression. [4 marks]

| wx∖yz | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    | 1  | 0  | 0  | 1  |

| 01    | 0  | 0  | 1  | 1  |

| 11    | X  | X  | X  | X  |

| 10    | 1  | 0  | X  | X  |

3) Implement the following function using minimum number of *NAND* gates. <u>Assume that all inputs are available in true and complement forms.</u> [2 marks]

$$F = A'B + B'C + AC'$$

4) Implement the function in part (3) above using minimum number of <u>NOR</u> gates only.

<u>Assume that all input are available in true and complement forms.</u> [4 marks]

Question 3: [20 marks]

a) Show the **8-bit binary representation** of the following decimal numbers. [4 marks]

| Decimal<br>Number | <b>8-bit</b> Sign-Magnitude representation | 8-bit 2's complement representation |

|-------------------|--------------------------------------------|-------------------------------------|

| +35               |                                            |                                     |

| -76               |                                            |                                     |

b) Given the following 8-bit binary value, show the equivalent decimal value when the binary number is interpreted as unsigned, as a sign-magnitude number, as a 1's complement, or as a 2's complement signed number. [4 marks]

| 8-bit     | Decir              | mal Value when the               | binary number is inter           | rpreted as:                      |

|-----------|--------------------|----------------------------------|----------------------------------|----------------------------------|

| Binary    | Unsigned<br>Number | Sign-Magnitude<br>Decimal Number | 1's complement<br>Decimal Number | 2's complement<br>Decimal Number |

| 1011 1010 |                    |                                  |                                  |                                  |

c) Show the addition / subtraction of the following 8-bit signed numbers represented in 2's complement. Indicate whether there is an overflow (Yes / No). [6 marks]

|      | 0 1<br>1 1 |    |  |  | - |  |    | _   |     |     |  | 0 0 |  | - |

|------|------------|----|--|--|---|--|----|-----|-----|-----|--|-----|--|---|

| 0ver | flow       | 1? |  |  |   |  | Ov | erf | 101 | v ? |  |     |  |   |

| Qu    | Question 4:                                                                                                                         |                                 |  |  |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|--|

| It is | required to design a circuit to multiply two 2-bit unsigned binary numbers; $A_1A_0$ are                                            | ad $\mathbf{B_1}\mathbf{B_0}$ . |  |  |  |  |  |  |  |

| a)    | Obtain the truth table for this circuit.                                                                                            | [4 marks]                       |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

| b)    | Using the Karnaugh map, find a minimal sum-of-product expression for the output weight 2 (i.e. 2 <sup>nd</sup> bit from the right). | bit with [2 marks]              |  |  |  |  |  |  |  |

|       |                                                                                                                                     |                                 |  |  |  |  |  |  |  |

## Question 5: For this question, <u>Properly label all components</u>, their inputs and outputs.

Given the function  $F(A, B, C) = A \overline{C} + \overline{B} C$

[14 marks]

a) Implement F using the smallest size MUX. Do not use any additional gates.

[6 marks]

b) Implement F using a single 3-to-8 decoder, and a single OR gate.

[4 marks]

c) Implement F using two 2-to-4 decoders with enable, one inverter, and one NOR gate. [4 marks]

#### Question 6: For this question, properly label all components, their inputs and outputs.

Using a <u>minimal</u> number of standard components (such as **decoders**, **encoders**, **multiplexers**, **adders**, **magnitude comparators**) and any other necessary logic gates, design a circuit that:

- Takes three 4-bit unsigned binary numbers  $A = A_3A_2A_1A_0$ ,  $B = B_3B_2B_1B_0$ , and  $C = C_3C_2C_1C_0$ .

- And produces two 4-bit outputs  $X = X_3X_2X_1X_0$ , and  $Y = Y_3Y_2Y_1Y_0$  such that X equals the <u>smallest number</u> among A, B, and C (i.e.  $X = \min(A,B,C)$ ), while Y corresponds to the <u>largest number</u> among A, B, and C (i.e.  $Y = \max(A,B,C)$ ). [20 marks]

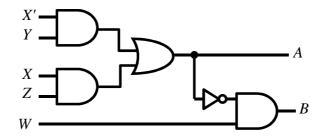

**Question 7:** Consider the combinational circuit shown below with inputs X, Y, Z, and W, and outputs A and B: [20 marks]

a) Write a Verilog module (call it **CC**) describing this circuit, *as is*, using primitive gates. Assume the following gate delays; inverter's delay= 1 (time unit), AND's delay= 2, OR's delay=3. **[5 marks]**

b) Write a test bench to test the above circuit for the following input combinations (add 10ns delay between the application of each input set):

XYZW=0000, then 0110, then 0010

[5 marks]

|      | Vrite another Verilog module (Call it CC_2) describing the same circuit but using t ssignment (i.e. assign statement). The output delays should also be modeled in |                            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|      |                                                                                                                                                                    |                            |

|      |                                                                                                                                                                    |                            |

|      |                                                                                                                                                                    |                            |

|      |                                                                                                                                                                    |                            |

|      | What do we need to change in the test bench of part (b) to simulate the 2 <sup>nd</sup> module ( <b>0</b>                                                          | CC 2) (b) 9                |

| u) v | vitat do we need to change in the test bench of part (b) to simulate the 2 module (c                                                                               | [2 marks]                  |

|      |                                                                                                                                                                    |                            |

|      |                                                                                                                                                                    |                            |

| e) A | dso, if we modify the test bench to try all possible 16 input combinations, would the produce exactly the same simulation results? Briefly explain why             | e two modules<br>[3 marks] |

|      |                                                                                                                                                                    |                            |