## King Fahd University of Petroleum and Minerals College of Computer Science and Engineering Computer Engineering Department

### COE 202: Digital Logic Design (3-0-3) Term 191 (Fall 2019) Major Exam 2 Saturday Nov. 16, 2019

# Time: 120 minutes, Total Pages: 12

| Name: | _ID: | Section: |

|-------|------|----------|

|       |      |          |

| Dr. Aiman El-Maleh    | Dr. Muhamed Mudawar    |

|-----------------------|------------------------|

| 🛛 Dr. Ali Al-Suwaiyan | 🗆 Dr. AbdulAziz Tabakh |

#### Notes:

- Do not open the exam book until instructed

- **No Calculators are allowed** (basic, advanced, cell phones, etc.)

- Answer all questions

- All steps must be shown

- Any assumptions made must be clearly stated

| Question | Maximum Points | Your Points |

|----------|----------------|-------------|

| Q1       | 12             |             |

| Q2       | 10             |             |

| Q3       | 19             |             |

| Q4       | 14             |             |

| Q5       | 15             |             |

| Q6       | 5              |             |

| Total    | 75             |             |

#### **Question 1:**

#### (12 marks)

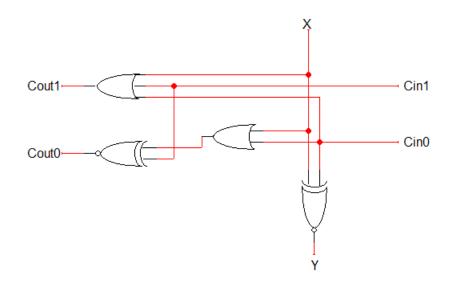

Consider the combinational circuit given below modeling a 1-bit cell for computing the equation Y=X-3, which has three inputs X, Cin1 and Cin0 and three outputs Y, Cout1, and Cout0:

- a) (4 points) Write a Verilog module to model the combinational circuit by modeling Cout0 using assign statement while modeling Y and Cout1 using primitive gates. Add gate delay to your model assuming that the delay of a 2-input XNOR gates is 3 units, the delay of a 2-input OR is 2 units and the delay of a 3-input OR gate is 3 units.

- b) (4 points) Write a Verilog module for modeling a 3-bit circuit for computing the equation Y=X-3 by instantiating three copies of this cell and making necessary connections. Note that the carry in signals for the first cell should be all connected to 0. Use the following module interface:

module DXM3 (output Cout1, Cout0, output [2:0] Y, input [2:0] X);

c) (4 points) Write a test bench that tests the 3-bit circuit modeled in (b) that applies the following input patterns to your circuit  $X=\{3'b011, 3'b100, 3'b111\}$  with a delay of 30 time units between each input combination.

## Question 2.

## (10 points)

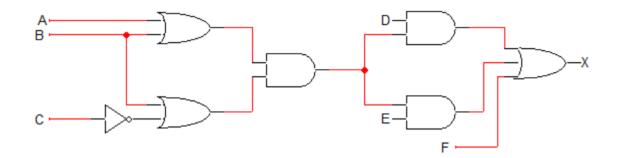

a) (4 points) Given the following circuit diagram with AND/OR/NOT gates:

Redraw the above circuit diagram **using only NAND gates** and a <u>minimum</u> number of inverters (NOT gates). You may insert inverters only when necessary.

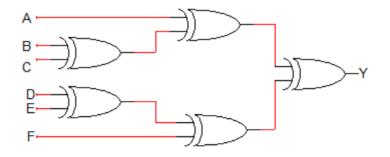

**b)** (3 points) Given the following circuit diagram with 2-input XOR gates:

Redraw the above circuit using **only 2-input XNOR gates**. <u>Minimize</u> the number of 2-input XNOR gates used.

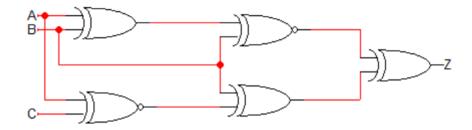

c) (3 points) Reimplement the circuit given below using <u>minimum</u> number of 2-input XOR gates:

## **Question 3**

### (19 points)

**I)** (5 points) Show the 8-bit binary representation of the following decimal numbers using the specified representations in the table below:

| Decimal<br>Number | 8-bit Sign-Magnitude<br>representation | 8-bit 1's complement representation | 8-bit 2's complement representation |

|-------------------|----------------------------------------|-------------------------------------|-------------------------------------|

| +21               |                                        |                                     |                                     |

| -74               |                                        |                                     |                                     |

**II)** (5 points) Given that A and B are 8-bit signed integers that use the 2's complement representation:

A = 11100110 B = 01010101

a) (2 points) What are the decimal values of A and B?

b) (3 points) Compute A – B in binary by converting subtraction into addition to the 2's complement of

B. Indicate whether there is overflow or not.

- (9 points) It is required to design a circuit that computes: S = 2\*X Y + 1. The inputs X[3:0] and Y[3:0] are

4-bit signed integers that use the 2's complement representation.

- a) (2 points) What is the minimum negative value of X? What is the maximum positive value?

**b)** (**3 points**) What is the minimum negative value of S? What is the maximum positive value? How many bits are needed to represent S without overflow?

**c)** (**4 points**) Using Full-Adders and inverters, draw a circuit that computes: S = 2\*X – Y + 1. Hint: 2\*X is computed by left-shifting X.

#### **Question 4.**

In this question, clearly label all components, their inputs, and outputs.

**a)** (4 points) Consider the following truth table, in which  $X_2$ ,  $X_1$ , and  $X_0$  are the inputs and  $Y_2$ ,  $Y_1$ , and  $Y_0$  are the outputs.

| <b>X</b> <sub>2</sub> | <b>X</b> <sub>1</sub> | X <sub>0</sub> | <b>Y</b> 2 | <b>Y</b> <sub>1</sub> | Y <sub>0</sub> |

|-----------------------|-----------------------|----------------|------------|-----------------------|----------------|

| 0                     | 0                     | 0              | 0          | 1                     | 0              |

| 0                     | 0                     | 1              | 0          | 1                     | 0              |

| 0                     | 1                     | 0              | 0          | 0                     | 1              |

| 0                     | 1                     | 1              | 0          | 0                     | 1              |

| 1                     | 0                     | 0              | 1          | 0                     | 1              |

| 1                     | 0                     | 1              | 1          | 0                     | 1              |

| 1                     | 1                     | 0              | 1          | 0                     | 1              |

| 1                     | 1                     | 1              | 1          | 0                     | 1              |

Using a minimum-size decoder and a minimum number of additional gates, show how to implement  $Y_2$ ,  $Y_1$ , and  $Y_0$ . Your additional logic gates must use the smallest possible number of inputs.

**b)** (3 points) Consider the function  $F(a, b, c) = \sum m(1, 2, 4, 5)$ . Assuming the availability of true and complemented values of a, b, and c, show an implementation of output F using a single 4-1 MUX.

#### (14 points)

c) (3 points) Show how to implement an 8-1 MUX using two 4-1 MUXes and a 2-1 MUX.

**d)** (4 points) Show how to implement a 1-8 demultiplexer using the minimum number of 2-4 and 1-2 decoders with enable inputs and nothing else.

# Question 5.

# (15 points)

- **I)** (7 points) You are required to design a combinational circuit that computes the equation Z = 3 |X|Where X[3:0] and Z[3:0] are 4-bit signed binary number in 2's complement representation.

- a) (4 points) Fill in the following table with the values of Z for each input value of X.

| X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | $Z_3Z_2Z_1Z_0$ |

|-------------------------------------------------------------|----------------|

| 0000                                                        |                |

| 0001                                                        |                |

| 0010                                                        |                |

| 0011                                                        |                |

| 0100                                                        |                |

| 0101                                                        |                |

| 0110                                                        |                |

| 0111                                                        |                |

| 1000                                                        |                |

| 1001                                                        |                |

| 1010                                                        |                |

| 1011                                                        |                |

| 1100                                                        |                |

| 1101                                                        |                |

| 1110                                                        |                |

| 1111                                                        |                |

**b)** (**3 points**) Use K-map to find the minimal SOP of the most significant bit of Z (z<sub>3</sub>).

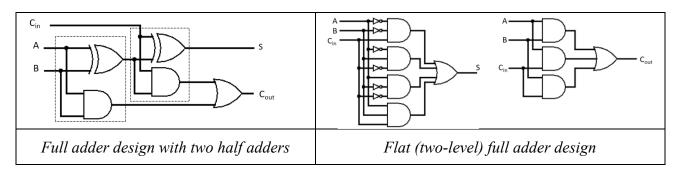

**II)** (8 points) Assume two different full adder implementations: one with two half adders and the other is flat (Two-Level) as shown below.

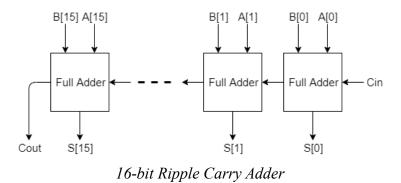

A 16-bit ripple carry adder is to be built using full adders as shown below. Based on gate delays given below, calculate the propagation delay of the output carry (Cout) and the most significant bit of the sum (S<sub>15</sub>) for both designs of full adders.

| Gate           | Delay |

|----------------|-------|

| 2-input XOR    | 3ns   |

| Inverter       | 1ns   |

| 2-input AND/OR | 2 ns  |

| 3-input AND/OR | 3ns   |

| 4-input OR     | 4ns   |

| Implementation               | Delay of C <sub>out</sub> | Delay of S <sub>15</sub> |

|------------------------------|---------------------------|--------------------------|

| 16-bit RCA with full adder   |                           |                          |

| implemented with two half    |                           |                          |

| adders                       |                           |                          |

| 16-bit RCA with full adder   |                           |                          |

| implemented using flat (two- |                           |                          |

| level) full adder            |                           |                          |

## **Question 6:**

#### (5 points)

Design a combinational circuit that receives three 4-bit **unsigned** numbers (A, B, C) and calculates the absolute value of the difference between the largest and the smallest (i.e., D = MAX(A,B,C) - MIN(A,B,C)). You may use only inverters and MSI components (adders, comparators, multiplexers, decoders, encoders and demultiplexers) of minimum size. Please note that you are not allowed to use subtractors as components. If you need a subtractor, show its design using an adder. Mark your inputs and outputs of each component clearly. (For example: A = 7, B = 3,  $C = 5 \rightarrow D = A - B = 4$ ).