### King Fahd University of Petroleum and Minerals Department of Computer Engineering

## DIGITAL LOGIC DESIGN COE 202

Exam 2, December 27, 2008

| Problems | Grading |

|----------|---------|

| 1        |         |

| 2        |         |

| 3        |         |

| TOTAL    |         |

Student Name:.....

Student ID:.....

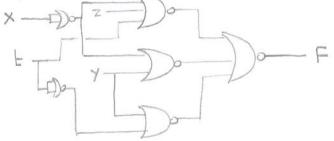

#### Problem-1: Optimizing combinational logic functions and their implementation

Consider the combinational logic function  $F(x, y, z, t) = \Sigma$  (0, 2, 4, 6, 7, 13, 14, 15) which is expressed as a sum of minterms. Answer each of the following questions:

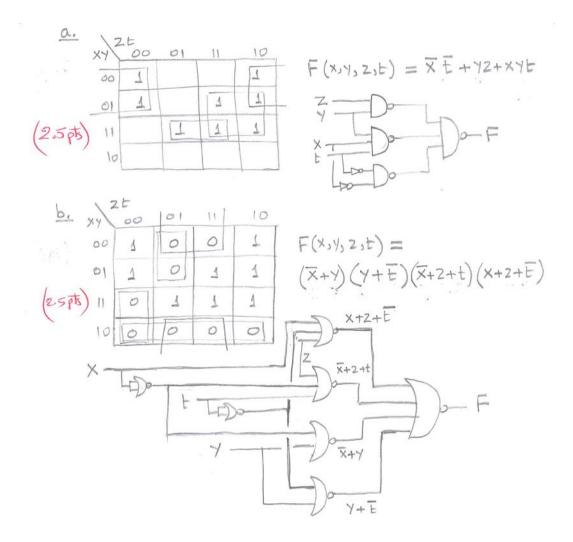

- a. Express F(x, y, z, t) as a minimal sum of products (SOP) and implement it using only NAND gates.

- b. Express F(x, y, z, t) as a minimal product of sums (POS) and implement it using only NOR gates.

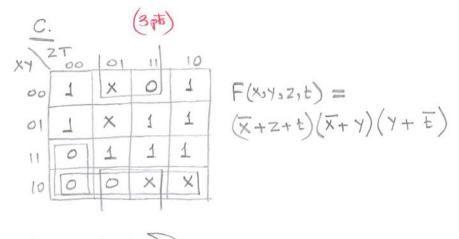

- c. Suppose that combinations (x, y, z, t) = 1, 5, 10, and 11 cannot occur and can be considered as don't care conditions. Express the above function F(x, y, z, t) as a minimal product of sums (POS) and implement it using only NOR gates.

#### Problem-2: Implementing combinational logic functions using multiplexers.

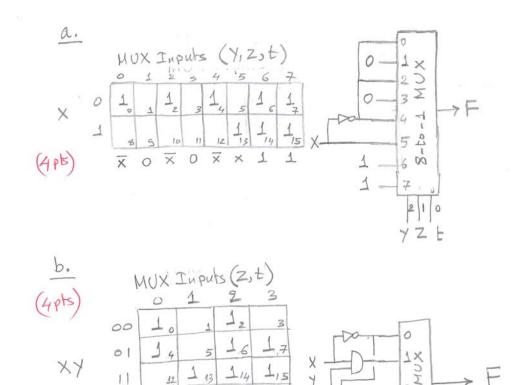

Consider the combinational logic function  $F(x, y, z, t) = \Sigma (0, 2, 4, 6, 7, 13, 14, 15)$  which is expressed as a sum of minterms. We assume 8-to-1 Multiplexers each has (1) three control lines X, Y, and Z, (2) eight inputs labelled a<sub>0</sub>, a<sub>1</sub>, a<sub>2</sub>, a<sub>3</sub>, a<sub>4</sub>, a<sub>5</sub>, a<sub>6</sub>, and a<sub>7</sub>, and (3) one output B. Answer each of the following questions:

- a. Implement function F(x, y, z, t) using ONLY an 8-to-1 Multiplexer and some additional logic.

- **b.** Implement function F(x, y, z, t) using **ONLY** a 4-to-1 Multiplexer and some additional logic.

4

11

10

X+Y

9 1-07

3

1 0

F Z

#### Problem-3: Design of a 12-bit parallel adder using Carry-Look-Ahead adders

13

9

XY

12

X

11

ID

It is desired to design a fast 12-bit parallel binary adder based on the use of the half-adder (HA) and Full-Adder (FA). The basic designs of HA and FA are as follows:

- The HA has inputs A and B and output S = A xor B and C = A.B

- The FA has inputs A, B, and  $C_{in}$  and output S = A xor B xor  $C_{in}$  and  $C_{out}$  = AB + (A xor B)  $C_{in}$

It is assumed that each logic gate incurs a fixed delay of T seconds.

# For each of the following questions you are requested to show your steps and provide your justification for each result:

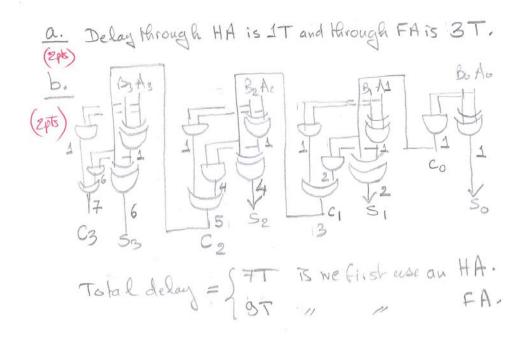

- **a.** Determine the total delay through the above HA and FA.

- **b.** Determine the total delay through a 4-bit Carry-Ripple Adder designed using the above HA and FA.

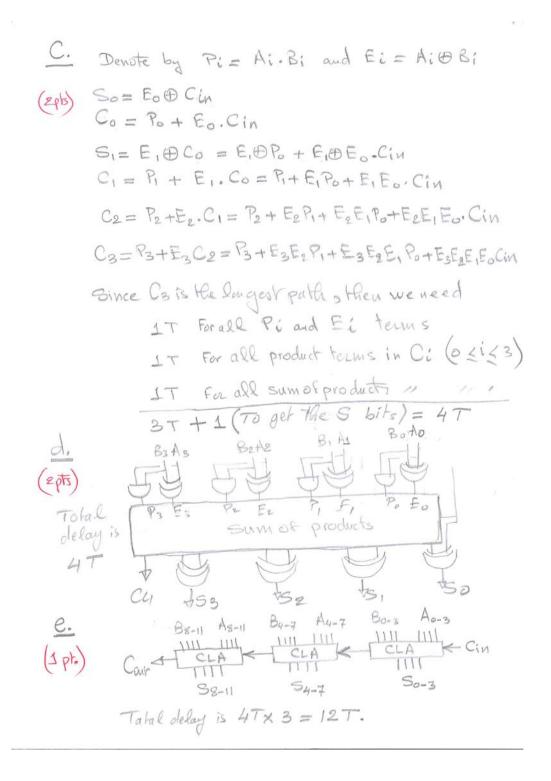

- **c.** How to modify the 4-bit Carry-Ripple Adder made using the above HA and FA to a 4-bit Carry-look-ahead adder!

- d. Design a 4-bit Carry-look-ahead Adder and determine its total delay.

- **e.** Design a 12-bit parallel adder using the previously designed 4-bit bit Carry-lookahead Adder and determine its total delay.