## King Fahd University of Petroleum and Minerals College of Computer Science and Engineering Computer Engineering Department

COE 202: Digital Logic Design (3-0-3) Term 102 (Spring 2011) Major Exam II Thursday April 28, 2011

Time: 120 minutes, Total Pages: 9

| Name: | ID: | Section: |

|-------|-----|----------|

|       |     |          |

|       |     |          |

## **Notes:**

- Do not open the exam book until instructed

- Calculators are not allowed (basic, advanced, cell phones, etc.)

- Answer all questions

- All steps must be shown

- Any assumptions made must be clearly stated

| Question | <b>Maximum Points</b> | Your Points |

|----------|-----------------------|-------------|

| 1        | 26                    |             |

| 2        | 16                    |             |

| 3        | 12                    |             |

| 4        | 26                    |             |

| 5        | 20                    |             |

| Total    | 100                   |             |

Question 1. (26 points)

(A). For the following Boolean function  $F(A, B, C, D)=\Sigma m(0, 1, 2, 5, 6, 7, 8, 9, 10, 12, 13)$

| CI<br>AB | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       | 1  | 1  | 0  | 1  |

| 01       | 0  | 1  | 1  | 1  |

| 11       | 1  | 1  | 0  | 0  |

| 10       | 1  | 1  | 0  | 1  |

- (i) Identify all the *prime implicants* and the *essential prime implicants* of F. (7+2=9 points)

- (ii) Simplify the Boolean function F into a minimal sum-of-products expression. (5 points)

(B) Consider the following Boolean function F together with the don't care conditions d

$F(A, B, C, D)=\Sigma m(0, 2, 5, 8, 10), d(A, B, C, D)=\Sigma m(1, 4, 7, 9, 11, 12, 14, 15)$

| CI<br>AB | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       | 1  | X  | 0  | 1  |

| 01       | X  | 1  | X  | 0  |

| 11       | X  | 0  | X  | X  |

| 10       | 1  | X  | X  | 1  |

- (i) Simplify the Boolean function **F** together with the don't care conditions **d**, into <u>minimal</u> <u>sum-of-products</u> expression. (4 points)

- (ii) Starting with the sum-of-products expression, implement the function using only **NAND** gates and **Inverters**. (4 points)

- (iii) Starting with the sum-of-products expression, implement the function using only **NOR** gates and **Inverters**. (4 points)

Question 2. (16 Points)

Design a 3-bit decrementer using only basic gates (AND, OR, and NOT). The circuit takes a 3-bit unsigned number  $I=I_2I_1I_0$  as input and generates a 3-bit output number  $Z=Z_2Z_1Z_0$  and a Valid output V. Whenever I>0 the output Z=I-1 and V=1. If I=0, the output is invalid which is indicated by an output V=0. Derive the simplified Boolean expressions of all outputs.

Question 3. (12 Points)

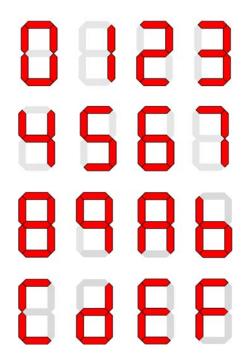

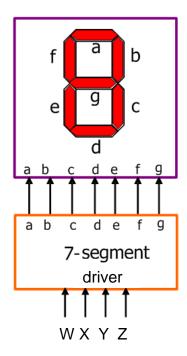

It is required to design a 7-segment display **driver** whose input is a Hexadecimal digit such that the resulting 7-seg display is as shown above (**Note that** HEX digits larger than 9 are displayed as  $A \rightarrow A$ ,  $B \rightarrow b$ ,  $C \rightarrow C$ ,  $D \rightarrow d$ ,  $E \rightarrow E$ ,  $F \rightarrow F$ ). The driver circuit should generate the 7-segment control signals (**a** to **g**).

If a single **decoder** and number of **OR** gates are used to build this driver circuit;

- a. What is the minimum size of the decoder? (3 points)

- b. What is the minimum a number of OR gates required to build the 7-segment display driver circuit (3 points)

- c. Draw the block diagram of the circuit showing in details how the control signals **g** and **c** are generated. (6 points)

Question 4. (26 Points)

**(A)**

i. Determine the decimal value of the 7-bit binary number (1011010) when interpreted as:

| An unsigned number |  |  | A signed-2's complement number |  |

|--------------------|--|--|--------------------------------|--|

|                    |  |  |                                |  |

ii. Represent the decimal value (- 21) in binary <u>using a total of 7 bits</u> in the following notations:

| A signed-magnitude number | A signed-1's complement number | A signed-2's complement number |  |  |

|---------------------------|--------------------------------|--------------------------------|--|--|

|                           |                                |                                |  |  |

iii. Perform the following signed-2's complement arithmetic operations in binary using 5 bits. All numbers given are represented in the signed-2's complement notation. Indicate clearly the <u>carry values</u> <u>from the last two stages</u>. For each of the three operations, check and indicate whether overflow occurred or not.

|                    | a. 01101<br>+10110 | b. 01010<br>- 11001 | c. 11010<br>- 00100 |

|--------------------|--------------------|---------------------|---------------------|

|                    |                    |                     |                     |

|                    |                    |                     |                     |

|                    |                    |                     |                     |

|                    |                    |                     |                     |

| Overflow Occurred? |                    |                     |                     |

| (Yes/No)           |                    |                     |                     |

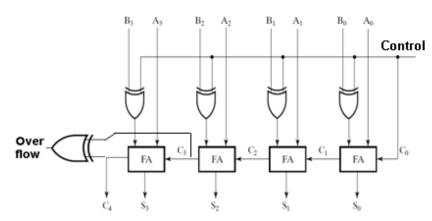

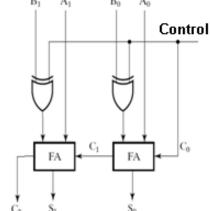

**(B)** Consider the 2's complement 4-bit adder/subtractor hardware shown (**FA** = full adder).

i. Fill in the spaces in the table below.

|      | Inputs |         |            | Out   | puts           |          |

|------|--------|---------|------------|-------|----------------|----------|

| A    | В      | Control | S (binary) | $C_4$ | C <sub>3</sub> | Overflow |

| 0111 | 0101   | 0       |            |       |                |          |

| 1010 | 1101   | 1       |            |       |                |          |

ii. What type of 4-bit adder is used in this design? (Circle the correct answer):

- Carry-ripple adder

- Carry-look-ahead adder

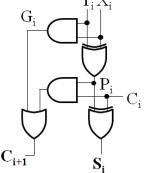

(C) Consider a 2-bit version of the hardware above which is shown below. Shown also is full adder used. Given that each basic gate (i.e. AND, OR, NOT) has a delay of  $\tau$  ns and the XOR gate has a delay of  $3\tau$ :

i. Express, as a function of  $\tau$ , the longest time interval needed for the hardware to perform an operation on the two 2-bit numbers.

ii. If such an operation must be performed in no longer than 33 ns, calculate the maximum basic gate delay allowed.

| Question 5.                                                                                                                    | (20 Points)           |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| (A) Given the function                                                                                                         |                       |

| $F(A,B,C) = \Pi M(0,2,4,5,6)$                                                                                                  |                       |

| i. Implement F using one (1) 3-to-8 decoder, and one (1) $\underline{NOR}$ gate. Properly label lines.                         | all input and output  |

|                                                                                                                                |                       |

|                                                                                                                                |                       |

|                                                                                                                                |                       |

|                                                                                                                                |                       |

|                                                                                                                                |                       |

|                                                                                                                                |                       |

|                                                                                                                                |                       |

|                                                                                                                                |                       |

|                                                                                                                                |                       |

| ii. Implement F using two (2) 2-to-4 decoders with enable, one (1) inverter, and on Properly label all input and output lines. | e (1) <b>OR</b> gate. |

|                                                                                                                                |                       |

|                                                                                                                                |                       |

| ( | <b>(B)</b> | Given | the | fur | ection |

|---|------------|-------|-----|-----|--------|

|   |            |       |     |     |        |

$$F(A,B,C) = \Sigma m (1,3,7)$$

i. Implement F using an 8-to-1 MUX. Properly label all input and output lines.

ii. Implement F using a 4-to-1 MUX. Show how you obtained your solution, and properly label all input and output lines.