# King Fahd University of Petroleum and Minerals College of Computer Science and Engineering Computer Engineering Department

## COE 202: Digital Logic Design (3-0-3) Term 092 (Spring 2010) Major Exam 2 Thursday May 15, 2010

## Time: 120 minutes, Total Pages: 6

Name:\_\_\_\_\_\_

ID:\_\_\_\_\_\_

Section: \_\_\_\_\_\_

## Notes:

- Do not open the exam book until instructed

- Calculators are not allowed (basic, advanced, cell phones, etc.)

- Answer all questions

- All steps must be shown

- Any assumptions made must be clearly stated

| Question | Maximum Points | Your Points |

|----------|----------------|-------------|

| 1        |                |             |

| 2        |                |             |

| 3        |                |             |

| 4        |                |             |

| Total    |                |             |

#### (xx points) **Question 1.** YΖ 1. Fill in the Spaces: (Show all work done to reach your answer) х 00 01 11 10 0 a. Using the K-map opposite, the function $F(X, Y, Z) = \overline{XZ} + XY\overline{Z} + X\overline{YZ}$ Х simplifies to \_\_\_\_\_ (1 literal). Show your work on the map. Ζ 0 b. The symbol is an equivalent representation of a \_\_\_\_\_ gate. c. $F(X, Y, Z) = \overline{X \oplus Y \oplus Z}$ is \_\_\_\_\_(0/1) for XYZ = 110. This function can be used to generate and detect \_\_\_\_\_\_ even/odd parity in digital communications. 2-to-4 Decoder D D1 A d. The 2-to-4 decoder with Enable shown opposite can be used as a \_\_\_\_\_-to-\_\_\_\_ A1 D2 demultiplexer, with the data to be demultiplexed applied to the \_\_\_\_\_ input. D-Enable YΖ Y x 00 01 11 10 e. On the K-map opposite, mark the 1s of the following function: 0 $F(X, Y, Z) = (\overline{X} + \overline{Z}).(Y + Z).(X + Y + \overline{Z})$ Х Ζ f. For the code converter shown opposite, fill in the spaces in the following table: Input Code Output Code 2 (wxyz) (ABCD) 3 0110 4 5 1101 1 6 16-to-4 7 Binary 2 16-to-4 3 в Encoder 4 g. In the ripple carry adder, a carry generated from a given stage always c 5 9 Encoder D 10 6

leads to a carry from the next stage: \_\_\_\_\_(True/False).

h. Carry-look ahead adders perform addition faster than ripple carry adders: \_\_\_\_\_(True/False)

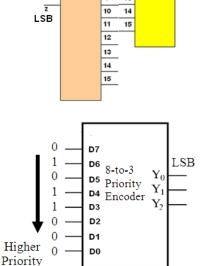

i. With the indicated input, the priority encoder shown opposite produces the binary output  $Y_2Y_1Y_0 =$ \_\_\_\_\_.

7 11

8 12

9 13

x

y

4-to-16 Decode LSB

### Question 2.

- 2.1We would like to design a combinational circuit that takes as input a 3-bit unsigned binary number X and produces an output Y where  $Y = X^2$ .

- a. How many bits are needed to represent the circuit output?

- b. Provide the truth table for the circuit, showing the bits of the inputs and outputs, with the MSB on the left in each case.

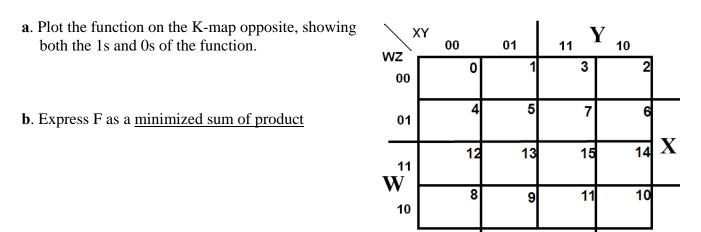

**2.2** Given the function  $F(W, X, Y, Z) = \sum m(1,3,5,6,7,9,11,14)$

Ζ

c. Express F as a minimized product of sums

**d**. Draw the logic diagram for a 2-level implementation of the result in (b) above using only one type of universal gates. Assume that both true and complemented forms of each variable are available.

### Question 3.

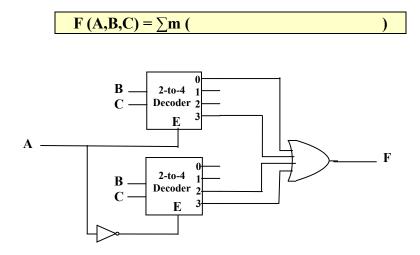

**a.** Analyze the circuit shown below and express F as a sum of minterms:

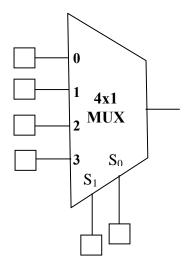

**b.** The truth table of a combinational function F is shown below. Implement F using a 4x1 MUX (*Use A, B as selection lines*). Clearly label every input of the multiplexer.

| А | В | C | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

4

⇒

Z=

$|\mathbf{A}|$

### (xx Points)

A 🚅

| • | In this question, you may ONLY use any number of the following parts:                                                           |       |

|---|---------------------------------------------------------------------------------------------------------------------------------|-------|

|   | Inverters, 4-bit Binary Parallel Adders, Decoders, Encoders, Multiplexers, Magnitude Comparators, Half Adders, and Full Adders. | 4-bit |

|   | You must CLEARLY LABEL the MSI part used together with ALL INPUTS & OUTPUTS                                                     | s.    |

a. Given a 4-bit signed 2's complement number A, design a circuit which outputs a 4-bit unsigned number Z which is equal to the magnitude of A, i.e. Z= |A|

Question 4.

- i. If S = W + X + Y + Z, what is the size of S (in bits)

- ii. Design a circuit that computes S, using <u>only any of the above listed parts</u>.

Page **6** of **6**