Ref: Online course on EE-390, KFUPM

#### Handout 15

#### by Dr Sheikh Sharif Iqbal

## Memory Interface of 8088 and 8086 processors

# Objective:

- To introduce the read and write bus cycles of the 8088 and 8086 processors.

- To discuss timing states associated with read/write bus cycles

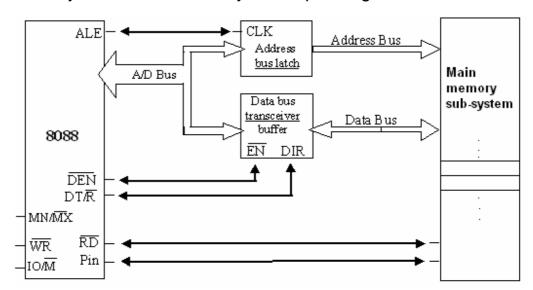

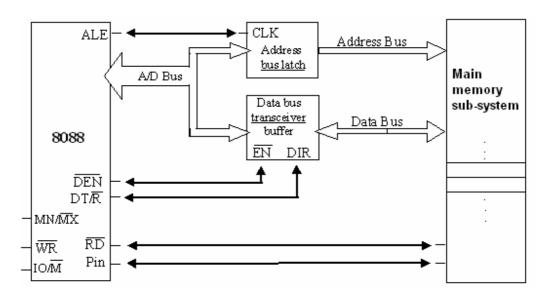

## Slide 1: Memory interface of a Minimum-mode 8088 system:

The block diagram below represents a memory interface circuitry of an 8088 based system, operating in minimum mode.

- Note: Note that aside from the CPU (8088) and the memory-subsystem, the main components of this diagram are "Address bus latch", "Data bus transceiver buffer" and address and data buses.

- The address bus carries the physical address generated by the CPU and selects the memory location to be accessed. The control signals (ale, read, write ....) are also shown in the diagram.

- The data bus transfers data between the CPU registers and the selected memory location

#### Slide 2: Timing Status of Minimum-mode 8088 memory interface:

- Since a memory read or write should be complete within one bus-cycle (4-CLK pulses, T<sub>1</sub>-T<sub>4</sub>), related timing states as follows:

- T<sub>1</sub> (<u>speech only</u>: or the 1<sup>st</sup> clock pulse)- starts the bus cycle. Actions include setting control signals to give the required logic values for IO/M, ALE, DT/R and a valid address onto the address bus.

- T<sub>2</sub> the RD or WR control signals are issued, DEN is asserted and in the case of a write, data is put onto the data bus. The DEN turns on the data bus buffers to connect the CPU to the external data bus. The READY input to the CPU is sampled at the end of T<sub>2</sub> and if READY is low, wait state (T<sub>W</sub>) is inserted before T<sub>3</sub> begins.

- $\circ$  T<sub>3</sub> this clock period is provided to allow memory to access the data. If the bus cycle is a read cycle, the data bus is sampled at the end of T<sub>3</sub> or the 3<sup>rd</sup> clock pulse of the bus-cycle.

- T<sub>4</sub> all bus signals are deactivated in preparation for the next clock cycle. The 8088 also finishes sampling the data (in a read cycle) in this period. For the write cycle, the trailing edge of the WR signal transfers data to the memory.

#### Slide 3: Minimum-mode Memory-Read bus-cycle of 8088 system:

- To complete the minimum-mode memory-read bus-cycle, the required control signals with appropriate active logic levels are :

- o IO/M = 'logic 0', to select memory interface

- O MN/MX = 'logic 1', to select minimum-mode of operation

- O DT/R = 'logic 0', to activate the data-receive mode of 'Data-bus-buffer'

- O Valid Physical-address of memory-location via address-bus (A<sub>19</sub> to A<sub>0</sub>)

- o ALE-pulse, to latch the valid Physical-address. ( )

- o RD = 'logic 0', to initiate reading data into CPU. Note, WR = 'logic 1'

- $\overline{\text{DEN}} = 0$ , enables the 'Data-Bus-transceiver-buffer' to let data pass

- O Reset RD=DEN='logic1', to END the read-bus-cycle.

- Memory interface block diagram related to above steps are shown in slide 1

**Note:** Next slide illustrates the timing diagram of these control signals

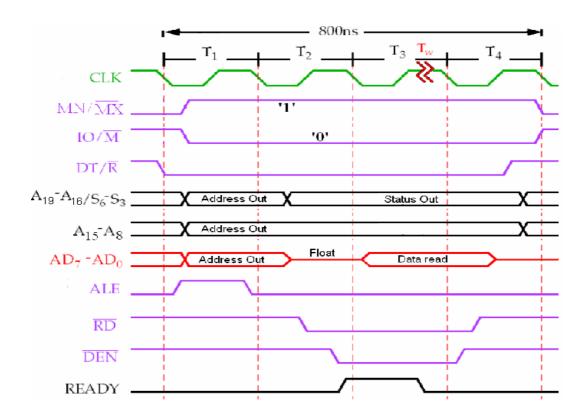

## Slide 4: Minimum-mode Memory-Read cycle of 8088 (Cont'd):

- The timing diagram for 8088 minimum mode memory read operation is shown below using logic '0' and '1' waveforms.

<u>Note:</u> Note that during  $T_1$  or the 1<sup>st</sup> clock pulse, the read bus cycle startes and valid address is latched together with setting minimum and maximum mode, input output or memory interface, data transmit and receive mode of buffer IC.

During  $T_2$ , the Read control signals are issued and data enable signal is asserted. Note that during this state the READY signal is also checked to insert wait status, if needed

During  $T_3$ , the data from the memory is read by sampling the data bus at the end of  $T_3$

During  $T_4$ , all bus signals are deactivated in preparation for the next clock cycle.

## Slide 5: Minimum-mode Memory-Write bus-cycle of 8088 system:

- To complete the minimum-mode memory-write bus-cycle, the required control signals with appropriate active logic levels are :

- O  $IO/\overline{M}$  = 'logic 0', to select memory interface

- O  $MN/\overline{MX}$  = 'logic 1', to select minimum-mode of operation

- O  $DT/\overline{R}$  = 'logic 1', to activate the data-transmit mode of 'Data-bus-buffer'

- O Valid Physical-address of memory-location via address-bus  $(A_{19} \text{ to } A_0)$

- O ALE-pulse, to latch the valid Physical-address. ( \( \subseteq \subseteq \)

- $\circ$   $\overline{WR}$  = 'logic 0', to initiate memory data writing. Note,  $\overline{RD}$  = 'logic 1'

- $\circ$   $\overline{DEN}$  = '0', enables the 'Data-Bus-transceiver-buffer' to let data pass

- O Reset WR=DEN='logic1', to END the write-bus-cycle.

- Memory interface block diagram related to above steps are shown in slide 1

<u>Note:</u> In the next slide, the timing diagram of these control signals are explained

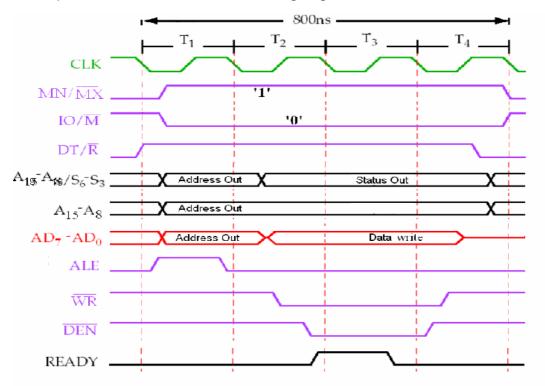

## Slide 6: Minimum-mode Memory-Write cycle of 8088 (Cont'd):

- The timing diagram for 8088 minimum mode memory write operation is shown below using logic '0' and '1' waveforms.

**Note:** Note that the control signal logic levels and timing diagram are similar to that of read operation, except for data transmit or receive mode, read and write signals.

The response of the ready signal is not shown here, as it behaves in the same way as data read process.

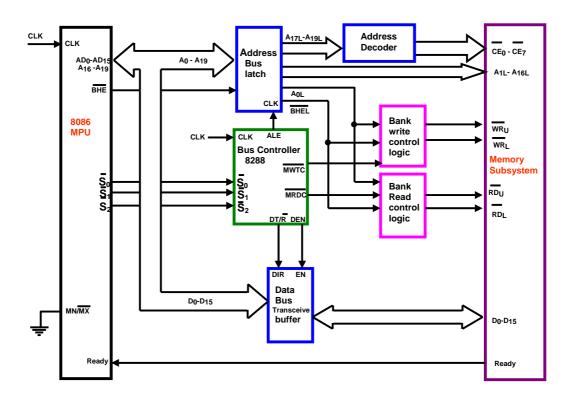

## Slide 7: Memory interface of a Maximum-mode 8086 system:

The block diagram below shows the memory interface circuit of an 8086 based system operating in maximum mode.

**Note:** The Bus controller is introduced here due to the support of multiprocessor environment of Maximum mode. The decoder is used to select desired memory chips. The remaining components of this circuit are similar to 8088 minimum mode circuit, as shown in <u>slide 1</u>.

Note that the bank high enable signal is used to control the access of even or odd memory banks of 8086 system. Also, the difference in the required logic level for data enable signal in maximum and minimum mode is visible by comparing this figure with the figure of slide 1

#### Slide 8: 8288 Bus-controller for 8088/8086 Maximum-mode:

- The status codes  $(\overline{S}_0, \overline{S}_1, \overline{S}_2)$  of the CPU is used by the buscontroller to activate maximum mode memory control signals:

| Status Inputs    |    |                | CPU Cycle             | 8288 Command |

|------------------|----|----------------|-----------------------|--------------|

| $\overline{S}_2$ | Sı | S <sub>0</sub> |                       |              |

| 0                | 0  | 0              | Interrupt Acknowledge | ĪNTĀ         |

| 0                | 0  | 1              | Read I/O Port         | ĪORC         |

| 0                | 1  | 0              | Write I/O Port        | IOWC, AIOWC  |

| 0                | 1  | 1              | Halt                  | None         |

| 1                | 0  | 0              | Instruction Fetch     | MRDC         |

| 1                | 0  | 1              | Read Memory           | MRDC         |

| 1                | 1  | 0              | Write Memory          | MWTC, AMWC   |

| 1                | 1  | 1              | Passive               | None         |

- These codes are important for multiprocessor environment, supported by Maximum mode.

## Slide 9: Maximum-mode Memory-Read bus-cycle of 8086 system:

- To complete the minimum-mode memory-read bus-cycle, the required control signals with appropriate active logic levels are:

- O  $IO/\overline{M}$  = 'logic 0', to select memory interface

- O  $MN/\overline{MX}$  = 'logic 0', to select maximum-mode of operation

- O  $DT/\overline{R}$  = 'logic 0', to activate the data-receive mode of 'Data-bus-buffer'

- O Valid Physical-address (A<sub>0</sub> to A<sub>19</sub>) and BHE signal is generated by CPU

- O ALE-pulse, to latch the valid Physical-address. ( $\square$

- O Proper status code  $\overline{S_0}$  to  $\overline{S_2}$  (as shown in table of slide 8) is generated by CPU to initiate data reading (MRDC) from the desired memory bank

- O DEN = '1', enables the 'Data-Bus-transceiver-buffer' to let data pass

- $\circ$  Reset  $\overline{MRDC}$  and DEN signals to END the read-bus-cycle.

- Memory interface block diagram relating to these signals are shown in slide 7

Note: In the next slide, the timing diagram related to these control signals are illustrated

\_\_\_\_\_

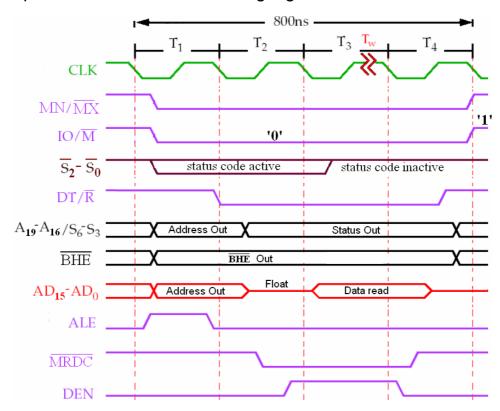

# Slide 10: Maximum-mode Memory-Read cycle of 8086 (Cont'd):

- The timing diagram for 8086 maximum mode memory read operation is shown below using logic '0' and '1' waveforms.

<u>Note:</u> Note that in maximum mode status codes needs to be active to generate control signals from bus controller.

The logic level required for BHE signal to access even and odd banks are discussed in earlier lecture.

## Slide11: Maximum-mode Memory-Write bus-cycle of 8086 system

- To complete the maximum-mode memory-write bus-cycle, the required control signals with appropriate active logic levels are:

- $\circ$  IO/M = 'logic 0', to select memory interface

- O MN/MX = 'logic 0', to select maximum-mode of operation

- O DT/R = 'logic 1', to activate the data-transmit mode of 'Data-bus-buffer'

- O Valid Physical-address (A<sub>0</sub> to A<sub>19</sub>) and BHE signal is generated by CPU

- O ALE-pulse, to latch the valid Physical-address. ( )

- O Proper status code  $\overline{S_0}$  to  $\overline{S_2}$  (as shown in table of slide 8) is generated by CPU to initiate data writing (MRTC) from the desired memory bank

- O DEN = '1', enables the 'Data-Bus-transceiver-buffer' to let data pass

- o Reset MRTC and DEN signals to END the read-bus-cycle

- Memory interface block diagram relating to these signals are shown in slide 7.

**Note:** In the next slide, the timing diagram relating to these control signals are explained

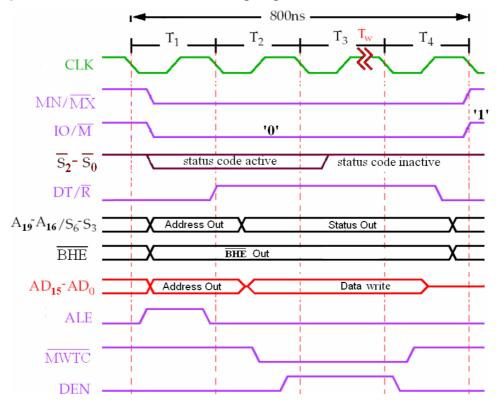

## Slide 12: Maximum-mode Memory-Write cycle of 8086 (Cont'd):

- The timing diagram for 8086 maximum mode memory write operation is shown below using logic '0' and '1' waveforms.

**Note:** Note that the control signal logic levels and timing diagram are similar to that of read operation, except for data transmit and receive, memory read and write signals.

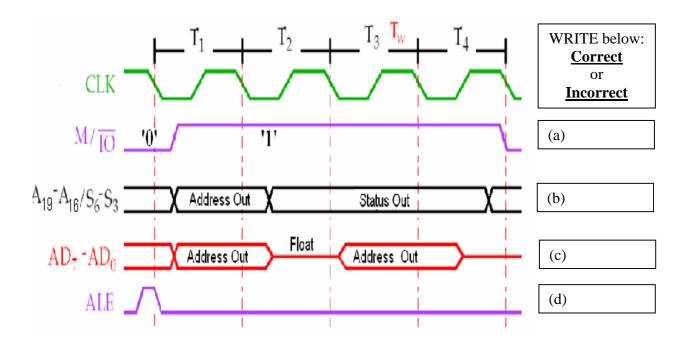

#### Slide 13: Example 1:

For the given timing diagram of a **8088 memory read bus-cycle**, <u>find the errors</u> in the diagram and indicate them in the given boxes (T1 - T4 are clock pulses that constitute one bus-cycle)

Solution: (a) Incorrect, as 8088 processors IO/M signals, and require logic '0', for the duration of the bus-cycle, to activate the memory (read) interface.

- (b) Correct, as these multiplex pins (A<sub>19</sub>-A<sub>16</sub>/S<sub>6</sub>-S<sub>3</sub>) of 8088 processor has to generate valid physical address during the 1<sup>st</sup> part of the bus-cycle and then produce proper status codes during the remaining of the bus-cycle.

- (c) Incorrect, as these multiplex pins (AD<sub>7</sub>-AD<sub>0</sub>) 8088 processors needs to access the data, to be read, during the 2<sup>nd</sup> half of the bus-cycle.

- (d) Incorrect, as the falling-edge of the ALE pulse should occur when all the address pins (A<sub>19</sub>-A<sub>0</sub>) carry valid physical address. (note that although the response of (A<sub>15</sub>-A<sub>8</sub>) are not shown, it is assumed that it will carry valid P.A. during 1<sup>st</sup> part of the bus-cycle)

#### Slide 14: Example 2:

For the given figure below, if 8088 is performing a minimum mode memory write bus cycle, which logic levels must be applied to DEN, DT/R and RD pins.

#### **Solution:**

- (1)  $\overline{DT/R}$ ='1' is send to activate transmit mode of "Data bus transceiver buffer IC"

- (2)  $\overline{RD}$  = '1' is send to de-activate data read process.

- (3)  $\overline{DEN} = '0'$  is send to enable the "Data bus transceiver buffer IC"

Slide 15: Exercise:

If the instruction "PUSH AX" is executed,

- (a) what status-code ( $\overline{S_0}$  to  $\overline{S_2}$ ) is outputted by 8086 in Maximum mode

- (b) what are logic levels of  $A_0$  and  $\overline{BHE}$ ?

- (c) what read/write control signals are produced by bus-controller?

Sol: (a)  $\overline{S}_2$ ='1',  $\overline{S}_1$ ='1',  $\overline{S}_0$ ='0'; (b)  $A_2$ ='0';  $\overline{BHE}$ ='0'; (c)  $\overline{AMWC}$  and  $\overline{MWTC}$