Extra Handout No 3 By Dr Sheikh Sharif Iqbal Ref: 'Online course on EE-390', KFUPM

# Software model of 8086 and 8086 systems

Objective:

- To present the software model of 80x86 microprocessor

- To introduce the Main-memory and input-output address spaces supported by 8086/8088 system

- To discuss the internal registers of 8086/8088 microprocessor

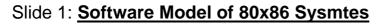

- Intel's recent microprocessors are fundamentally based on 80x86. So, the software model of 8086/8088 system is shown here to demonstrate its behavior from a software/programming point of view. - It is clear from the figure that in this model, we have access to 14 16-bit CPU registers, 1 Mega or million of byte-wide main memory storages and 64 thousand byte wide input output address spaces for peripheral devices.

- Thus, this model focuses more on the control-signals and registers of the microprocessor that can be accessed by the programmer from software prospective. This allows the programmer to know; how external memory and input/output peripherals are organized, how information is arranged in registers, and how CPU registers interacts with memory and input/output devices.

#### Slide 2: Main-memory of 80x86 systems (Software model)

- Computer system has several forms of memory storage, each with individual purposes.

- Detail discussion on all types of storage media are presented in later modules. This section will only discuss the organization of Main memory.

- Main memory (RAM) stores instructions/data related to the program, which is being executed.

- 8086 and 8088 systems can support 1-MByte of main-memory spaces (for temporary storage) and 64 KByte of input-output spaces.

- Since, 1 Mega =  $1048575_{D}$  = FFFFF<sub>H</sub>, converting the hex number into binary reaffirms the need for a 20-bit address bus (in binary).

- Thus, the physical address, pointing to the byte-wide storage locations in the main memory, ranges from  $00000_{H}$  to FFFF<sub>H</sub>.

### Slide 3: Software Organization of the 80x86 Main-memory

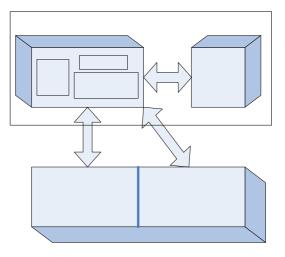

- The Main memory of 1 Mega bytewide storage locations of an 80x86 computer system are shown here.

Note, PA=00001<sub>H</sub> stores a data <u>Byte</u> of "5A<sub>H</sub>" and <u>Word</u> of "625A<sub>H</sub>", where 5A<sub>H</sub>→L.S.Byte & 62<sub>H</sub>→M.S.Byte and the <u>Double-word</u> of "A7FF625A<sub>H</sub>"

Note for a stored word data at physical address of 00001, the lower addressed byte is the Lease Significant byte of the word and the higher addressed byte is the most significant byte of the word. Similar rule also applies for the stored double-word

To permit efficient use of memory,

word data's are stored in 'even' and

'odd' physical address (PA) boundaries.

- Words stored at even PA's ( $0_H$ ,  $2_H$ ....FFFFE<sub>H</sub>) are called aligned words and odd PA's ( $1_H$ ,  $3_H$  .... FFFFF<sub>H</sub>), are called misaligned words. Note that the aligned word of "5A49<sub>H</sub>" is stored in PA=00000<sub>H</sub> *or* 0<sub>H</sub>

- Note that two aligned words are shown in figure with even physical address of  $00000_{\rm H}$  and FFFFE<sub>H</sub>. Also two misaligned words shown in the figure are stored at odd physical address of  $00003_{\rm H}$  and FFFFC<sub>H</sub>.

### Slide 4: Mapping of 80x86 systems Main-memory

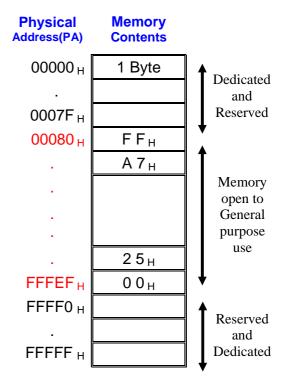

The 1 MByte main-memory of an 80x86 systems is divided into three parts: (a) General-use, (b) Dedicated and (c) Reserved storage locations

- The general-use part ranges from P.A. of  $80_{H}$  to FFFEF<sub>H</sub> and is open to the user for storing programs.

- Dedicated memories ranges from P.A. of " $0_H$  to  $13_H$ "and "FFFF $0_H$  to FFFFB<sub>H</sub>" and are used to process system interrupts, reset-functions and exceptions.

- Reserved memories ranges from P.A. of " $14_H$  to  $7F_H$ " and "FFFFB<sub>H</sub> to FFFFF<sub>H</sub>" and are used to process user defined interrupts for future hardware and software products.

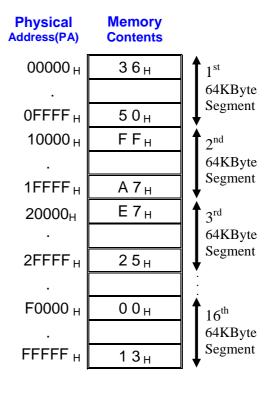

#### Slide 5: Segmentation of 80x86 systems Main-memory

- Although 80x86 supported a large general-use memory, the absence of addressing mechanism required it to be divided into 16<sub>D</sub>, 64KB segments

- Only four of these 64KB segments remain active at a time and can be accessed by the 80x86 processor.

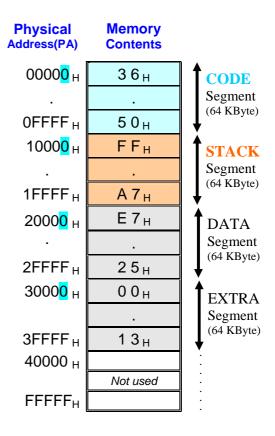

These active segments are named:

(a)Code Segment: Stores instruction codes

(b)Stack Segment: Temporary information

(c) Data Segment: Stores program data

(4) Extra Segment: Also for data storage

- Thus, Four segment give a maximum of 256 Kilo-Byte of active memory storage, of which 64 Kilo-Byte are for storing program instruction codes, 64 Kilo-Byte are for stack storage and 128 Kilo-Byte are for storing program data.

# Slide 6: Segmentation of 80x86 systems Main-memory (cont'd)

- The 64 KByte ( $65535_{H}$ =FFFF<sub>H</sub>) segments are allowed to be contiguous, adjacent, disjointed and partially or totally overlapping to each other.

- This point of overlapping segments will be clear in the lecture about DEBUG or Turbo Debugger.

The only restriction in allocating segments are to have a <sup>(0</sup><sub>H</sub>' number as the least-significant hex-digit of the <u>Base address (the P.A pointing</u> to the beginning of any segment)

Thus, <u>Base address</u> are the starting address of any 64 KByte segment.

- Physical address are also expressed interims of its segment base part (that is left most 4 hex digits of base address) and offset part (*that is displacement between the base address and the pointed memory location*)

Thus, a data segment memory location with  $PA=22356_H$  can also be written as  $2000_H:2356_H$ , where segment base= $2000_H$  & offset is  $2356_H$

### Slide 7: Input-output Ports of 80x86' system:

- The 8086/8088 processors supports 64 Kbyte (65535<sub>H</sub>=FFF<sub>H</sub>) byte-wide input/output (I/O) ports, accessed by dedicated instructions.

- In the software model of 80x86 systems, input-output ports are considered to be byte address spaces, either as part of the main memory or as an isolated device.

- The storage/retrieval techniques of byte and word data's are similar to that of main-memory of 80x86 processor

| Physical<br>Address(PA) | I/O<br>Contents                |  |  |

|-------------------------|--------------------------------|--|--|

| 0000 <sub>Н</sub>       | 1 Byte                         |  |  |

| 0001 <sub>Н</sub>       | А7 <sub>Н</sub>                |  |  |

| 0002 <sub>Н</sub>       | 50 <sub>н</sub>                |  |  |

| 0003 <sub>Н</sub>       | FFH                            |  |  |

|                         | 64 K Byte<br>address<br>spaces |  |  |

| FFFE <sub>H</sub>       | 25 <sub>н</sub>                |  |  |

| FFFF <sub>H</sub>       | 00н                            |  |  |

- More information on the operation and classes of input output address spaces are given in later modules of this course.

### Slide 9: Software Model of the CPU in an 80x86 system:

- The software model of CPU consists of a number of 16-bit registers for dedicated operation.

- These internal registers are shown in the figure. Note that they are grouped according to their functions as will be explained later.

- The 2<sup>nd</sup> group of four registers is called Data-registers (AX ... DX) and stores intermediate results, to be acted upon by next instruction.

- The 1<sup>st</sup> group of registers (DS ..) is called segment registers, which combines with 'IP' or the 3<sup>rd</sup> group of registers (SP... DI) to generate physical addresses (PA's) of main memory storage locations.

- The programmer should know

the purpose, functions, operations and limitation of these registers.

- The detail definitions of these registers are given in the next section.

### Slide 10: Software Model: Definition of CPU registers:

- Code Segment Register (CS) stores the leftmost sixteen-bits (4-hex digits) of the base address related to the 64-KByte Code segment memory locations. Remember that the base addresses of any segments are restricted to have a " $0_{\rm H}$ " as the rightmost hex-digit.

- In Slide 5, it is already shown that the base address consist of the four left-most hex digits with a " $0_H$ " as the Least significant (or rightmost)hex digit

- Instruction Pointer register (IP) is a 16-bit register that stores the offset part of the physical address, which when combined with the CS register values, generates the physical address that points to memory locations within the 64-KByte Code Segment area.

- The method used to combine the values of IP and CS to generate the PA will be illustrated in next lecture of this module..

- Data Segment Register (DS) stores the leftmost sixteen-bits of the base address related to the 64KByte Data segment memory locations

### Slide 11: Software Model: Definition of CPU registers (cont'd)

- Extra Segment register (ES) stores the leftmost sixteen-bits (4-hex digits) of the base address related to the 64-KByte Extra segment memory locations. (as the rightmost hex-digit of this PA is " $\mathbf{0}_{H}$ ")

- Source Index register (SI) stores the offset address part of the physical address, which when combined with either DS or ES register contents, points to the <u>source data</u> stored within the 64-KByte Data or Extra Segment memory locations, respectively.

- Destination Index register (DI) stores the offset address part of the physical address, which when combined with either DS or ES register contents, points to the <u>destination data</u> stored within the 64-KByte Data or Extra Segment memory locations, respectively.

# Slide 12: Software Model: Definition of CPU registers (cont'd)

- Stack Segment register (SS) stores the leftmost sixteen-bits (or 4-hex digits) of the base address related to the 64-KByte Stack segment memory locations. (as rightmost hex-digit of this PA is " $\mathbf{0}_{\text{H}}$ ")

- Stack Pointer Register (SP) and Base Pointer Register (BP) stores the offset part of the physical address, which when combined with the values of SS-register, generates the physical address that points to memory locations within the 64-KByte Stack Segment area. - The difference between SP and BP will become clear in the lecture discussing Addressing modes.

- Data register (AX, BX, CX, DX) are 16-bit general purpose registers used for arithmetic calculations, temporary data storage, data transfer and special instructions.

- Further detail of data registers are presented in next slide.

### Slide 13: Software Model: Definition of CPU registers (cont'd)

- The names of these data registers come from their functions:

- AX is called Accumulator register and is the most commonly used register. This is also use for special instructions like MUL, DIV, CBW, LAHF, IN, OUT etc.

- BX is called Base register and used by several addressing modes and special instruction like XLAT.

- CX is called the counter register and used by special instructions like LOOP, SHIFT etc.

- DX is called the Data register are used by special instructions like MUL, DIV, IN etc.

- The purpose and functions of these assembly language instructions will be introduced in module 2.

- All of these four 16-bit registers can be accessed as a whole for word-data operation or as two 8-bit registers for byte-data operation.

Such as;  $(AX)_{word} = (AH)_{byte} (AL)_{byte}$ ;  $(BX)_{word} = (BH)_{byte} (BL)_{byte}$ ;  $(CX)_{word} = (CH)_{byte} (CL)_{byte}$ ;  $(DX)_{word} = (DH)_{byte} (DL)_{byte}$ ; - Thus, if  $AX = 23F5_H$ , this means  $AH = 23_H$  and  $AL = F5_H$

The Least-Significant-Byte of AX is stores in **AL** register AND Most-Significant-Byte of AX is stores in **AH** register

### Slide 14: Software Model: Definition of CPU registers (cont'd)

- Status Register (SR), also called flags register, reports the status of the flags after the execution of every instruction.

- Often SR register values determine the result of the executed instruction. Such as carry/borrow information for arithmetic instruction

- In 80x86 model, the 16-bit status or flag register is defined as:

| Bit 15 | TF DF | <i>IF</i> OF | SF ZF | AF | PF ( | CF |

|--------|-------|--------------|-------|----|------|----|

|--------|-------|--------------|-------|----|------|----|

- (a) Carry Flag (CF): If Carry or Borrow occurred from the MSB of resulted DATA, then CF=CY=1 (set) otherwise CF=NC=0 (reset) Example:  $10001111_B + 11110000_B = 01111111_B$  and CF  $\rightarrow$  CY

- (b) Parity FLAG (PF): If the number of binary '1's' in the resulted DATA is even then PF=PE=1 (set) otherwise PF=PO=0 (reset). Example:  $10001111_B + 11110000_B = 01111111_B$  and PF  $\rightarrow$  PO

#### Slide 15: Software Model: Definition of CPU registers (cont'd)

- (c) Auxiliary FLAG (AF): If Carry or Borrow occurred from the M.S.Nibble of resulted DATA then AF=AC=1(set) else AF=NA=0 Example:  $10001111_B + 01001000_B = 11010_111_B$  and AF  $\rightarrow$  AC

- (d)Zero FLAG (ZF): If the execution of previous instruction results in a DATA=0, then ZF=ZR=1 (set), otherwise ZF=NZ=0 (reset). Example:  $0000001_B - 0000001_B = 0_B$  and ZF  $\rightarrow$  ZR

- (e)Sign FLAG (SF): If the MSB of resulted signed DATA is "1<sub>B</sub>", then SF=NG=1 (negative data) otherwise SF=PL=0 ( $\approx$ positive). Example: 10000001<sub>B</sub>+00000001<sub>B</sub> = <u>1</u>0000010<sub>B</sub> <u>and</u> SF  $\rightarrow$  NG

- (f) Overflow FLAG (OF): Indicates that Signed data is out of range.

- (g)Direction FLAG (DF): Auto-decrement or Auto Increment in address after execution of string operation; DN=1 (set) or UP=0

- (h) Trap FLAG (TF) decides operating mode (single-step or continues)

- The advantages of these flags will become clear during executing arithmetic and shift instructions, covered in later modules.

### Slide 17: Reminder:

$(PA)_{in \text{ Code-Segment memory}} = \underline{CS} * 10 + IP; \quad (PA)_{in \text{ Data-Segment}} = DS * 10 + SI = DS * 10 + DI;$  $(PA)_{in \text{ Extra-Segment memory}} = \underline{ES} * 10 + SI = \underline{ES} * 10 + DI; \quad (PA)_{in \text{ Stack-Segment}} = \underline{SS} * 10 + SP;$

20 Bit Physical Address pointing to Memory = Related Segment Register value \*10 + Offset Register value

20-bit **Physical address =** 10\*16-bit segment **base address** + 16-bit **offset or effective address**. Note that the **lowest nibble** (or lowest hex digit) of the **base address** (*lowest*-

-physical address of a segment) should be " $\mathbf{0}_{\mathrm{H}}$ "  $\rightarrow$  (PA)<sub>Seg Base</sub> = 1234 $\mathbf{0}_{\mathrm{H}}$