# Handout 4

# **MOSFET**

# **Sheikh Sharif Iqbal**

# (Ref: Text book and KFUPM Online course of EE-203)

(Remember to solve all the related examples, exercises problems as given in the Syllabus)

# **<u>Chapter 4</u> – MOS Field-Effect Transistors (MOSFETs)**

Text book: "Microelectronic Circuits by Sedra and Smith

- Metal-Oxide semiconductor Field-Effect Transistors (MOSFETs):

- MOSFET has been extremely popular since the late 1970s. Like transistors, the current flow between two terminals (Drain to source) in MOSFET are controlled by the third terminal (gate)

# - Why MOS Transistors?

- Takes smaller silicone area on the IC

- Simple to manufacture

- No need for biasing resistors.

- Used in VLSI (very-large-scale integration)

- Comparison between MOSFET & BJT??

- Can be made smaller /higher integration scale

- Easier to fabricate /lower manufacturing cost

- Simpler circuitry for digital logic and memory

- Inferior analog circuit performance (lower gain)

- Most digital ICs use MOS technology.

- Also recently more

and more analog

circuits are

implemented in MOS

technology for lower

cost integration with

digital circuits in the

same chip (IC)

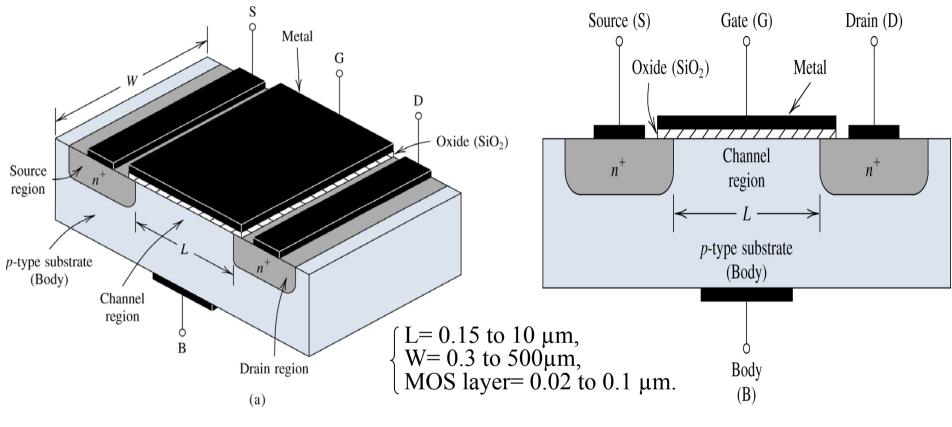

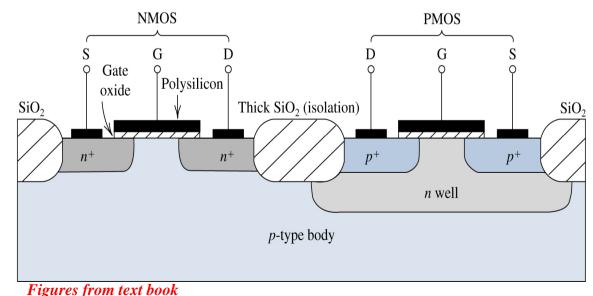

**4.1:Device Structure of MOSFET:** The name of MOS is apparent from figures

• Four Terminals are Gate, Drain, Source & Body

Figures from text book

(b)

- Unlike BJT, MOSFET is normally constructed as a symmetrical device (DS)

- Minimum achievable value of L in a particular MOS technology is often referred as the **feature size**. Intel Pentium-4 uses 0.13  $\mu$ m technology.

- Lately poly-silicon with high conductivity is used instead of metal to form gates

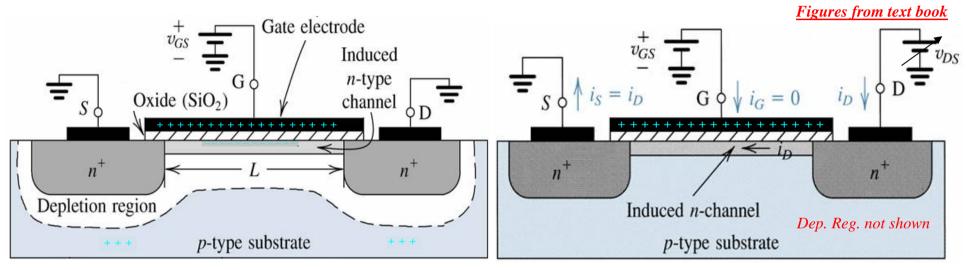

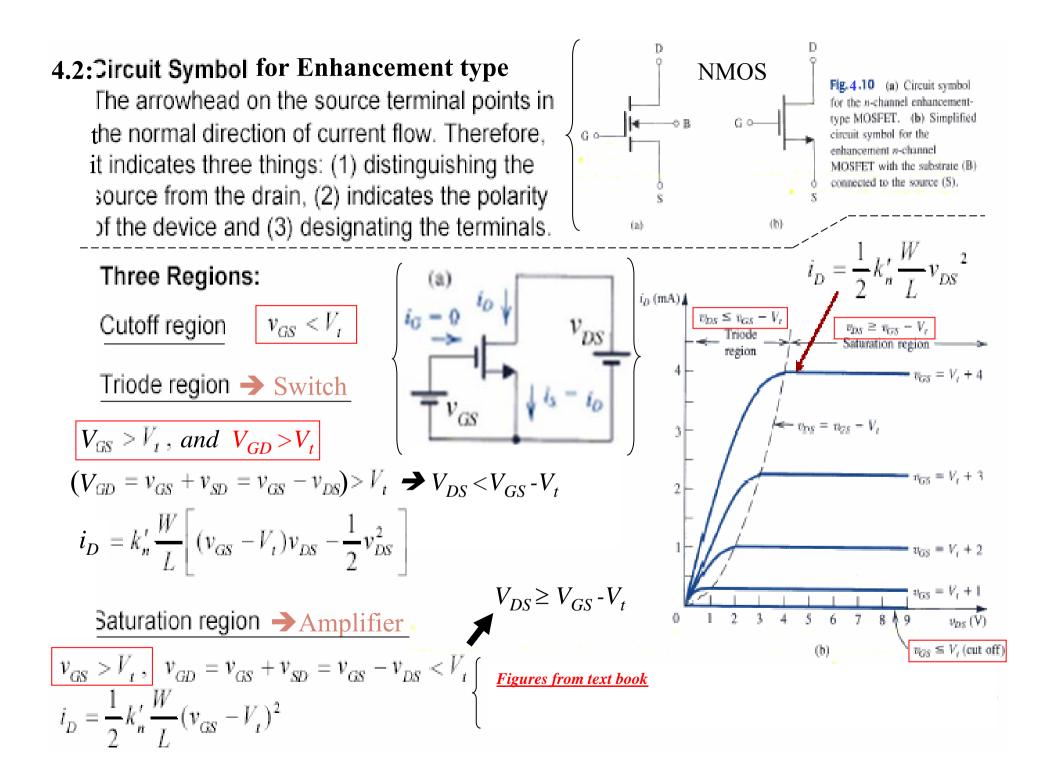

#### **BASIC OPERATIONAL THEORY OF NMOS:** *N-channel MOSFET considered*

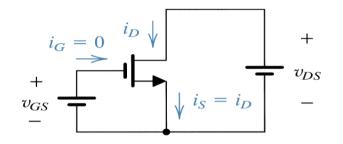

- The current controlled mechanism (*for drain current*) is based on electric field established by the voltage ' $V_{GS}$ ' applied to control terminal (*gate*).

- Current  $(i_D)$  is conducted by only one type of carrier "electrons (*for NMOS or N-channel MOSFET*) or holes (*for PMOS*)". So FET is also called unipolar transistors

**Physical Operation with No**  $v_{GS}$ : With no bias voltage is applied to gate, two back-toback diodes between drain & source prevent the flow of  $i_D$  as  $v_{DS}$  is applied. ( $R_{DS} \approx 10^{12} \Omega$ )

**Creating a Channel for**  $i_D$  **flow:** If 'S' & 'D' are GNDed and a '+ $v_{GS}$ ' is applied to 'G' holes are repelled from the channel region, leaving behind a carrier-depletion region.

Further increasing  $V_{GS}$  attracts minority carrier (e<sup>-1</sup>'s) from P-substrate into the channel region. When sufficient amount of e<sup>-1</sup>'s accumulate near the surface of the substrate under the gate, an *N* region (*N*-channel) is created-called as the **inversion layer**.

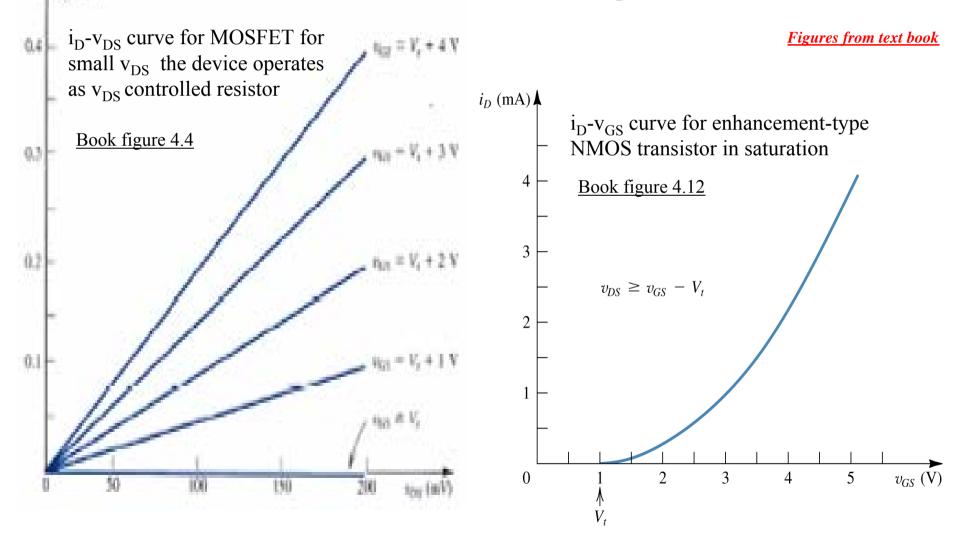

**Applying a Small**  $\mathbf{v}_{DS}$  or if  $\mathbf{v}_{DS} \approx (0.1 \text{ or } 0.2 \text{ V})$  causes a current  $i_D$  to flow through the induced *N*-channel from D to S. The magnitude of  $i_D$  depends on the density of electrons in the channel, which in turn depends on  $\mathbf{v}_{GS}$ . For  $\mathbf{v}_{GS} = \mathbf{V}_t$  (*threshold voltage*), the channel is just induced and the conducted current is still negligibly small. As,  $\mathbf{v}_{GS} > \mathbf{V}_t$ , depth of the channel increases,  $i_D$  will be proportional to ( $\mathbf{v}_{GS} - \mathbf{V}_t$ ), known as **effective voltage**. Increasing  $\mathbf{v}_{GS}$  above  $\mathbf{V}_t$  enhances the channel, hence it is called **enhancement type MOSFET**. Note that  $i_G = 0$ , due to M.O. layer

-Now since the  $v_{DS}$  drops across the channel length, this voltages decreases from vDS to 0 volt, as we travel along the channel from drain to source. Thus the voltage between the gate and the points along the channel becomes:  $v_{GS}$ -0 at source end and  $v_{GS}$ - $v_{DS}$  at the drain end. This shows that the channel don't have even depth, as the depth depends on voltage. Now increasing  $v_{DS}$  beyond  $v_{GS}$  value causes channel to pinchoff

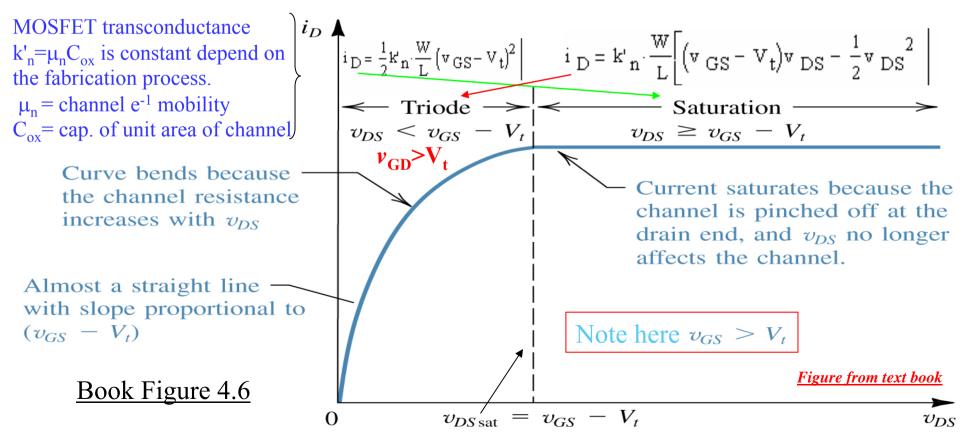

- THUS,  $(v_{GS} - v_{DS}) > V_t$ , or  $v_{DS} < (v_{GS} - V_t)$  or  $v_{GD} > V_t$  produce continues channel depth at drain end and results the MOSFET to operate in Triode region. Otherwise the MOSFET operates in Saturation region with pincoff channel and  $i_D \not \otimes v_{DS}$  **Channel length Modulation:** If  $v_{DS}$  is further increased from pinched-off channel  $(v_{DSsat})$ , the channel length is reduced (by moving from drain end). This phenomena is known as "channel length modulation" & its affect on  $i_D$  is incorporated by " $\lambda$ "

Note: Most of the problems here will assume  $\lambda=0$

# **Physical Operation of Enhancement NMOS:** For increasing $v_{DS}$ . Thus, $v_{DS}$ appears as a voltage drop across the channel. Voltage across the oxide decreases from $v_{GS}$ at 'S' to $(v_{GS} - V_t)$ at 'D'. The channel depth will be tapered and become more tapered as $v_{DS}$ is further increased.

Eventually, when  $(v_{GS} - v_{DS}) = V_t$ , the channel will be **pinched off (see** figures 4.5 & 4.7) Increasing  $v_{DS}$  beyond this value has no effect as  $i_D$  saturates. Thus, MOSFET is now operating in the **saturation region**. Thus,  $v_{DSsat} = v_{GS} - V_t$

**Example:** Use triode expression of  $i_D$ , given in eq 4.5(a), to calculate  $r_{DS}$

For Triode Region

$$\mathbf{i}_{\mathrm{D}} = \mathbf{k}_{\mathrm{n}} \cdot \frac{\mathbf{W}}{\mathbf{L}} \left[ \left( \left( \mathbf{v}_{\mathrm{GS}} - \mathbf{V}_{\mathrm{t}} \right) \right) \cdot \mathbf{v}_{\mathrm{DS}} - \frac{1}{2} \cdot \mathbf{v}_{\mathrm{DS}}^{2} \right]$$

However for small  $v_{DS}$ , then  $\frac{1}{2} \cdot v_{DS}^{2}$  approaches zero. The resulting equation then is

$$\mathbf{i}_{\mathrm{D}} = \mathbf{k}_{\mathrm{n}} \cdot \frac{\mathbf{W}}{\mathbf{L}} \Big[ \big( \big( \mathbf{v}_{\mathrm{GS}} - \mathbf{V}_{\mathrm{t}} \big) \big) \cdot \mathbf{v}_{\mathrm{DS}} \Big]$$

To find the drain-to-source resistance

$\mathbf{r}_{\mathrm{DS}} = \frac{\mathbf{v}_{\mathrm{DS}}}{\mathbf{i}_{\mathrm{D}}} \quad \left\{ \begin{array}{c} \text{if other parameter are given} \\ \text{We can solve this } \mathbf{r}_{\mathrm{DS}} \end{array} \right.$

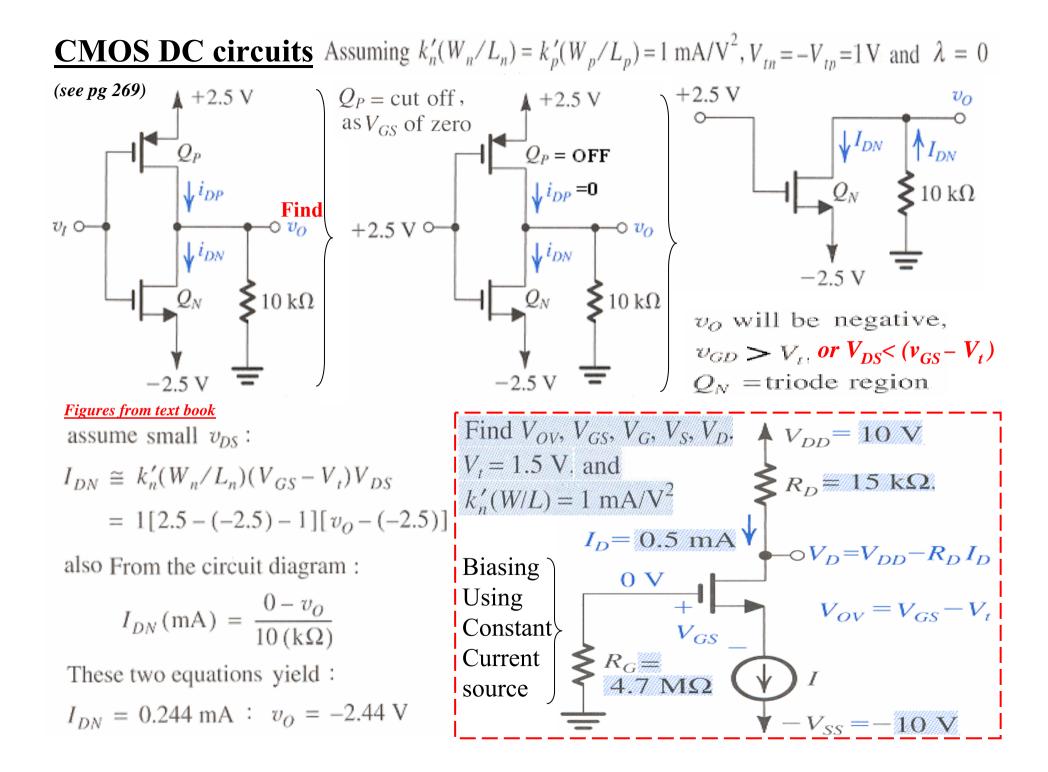

**<u>CMOS</u>**: Cross section of a complementary MOS integrated circuit. Note that the PMOS transistor is formed in a separate *n*type region, known as an *n* well. Another arrangement is also possible in which an *n*-type body is used and the *n* device is formed in a *p* well.

**Exercise 1**: For Enhancement type NMOS with  $V_t$ = 1V and  $k'_n(W/L) = 0.5 \text{ mA/V}^2$ , find  $i_D$  and whether the circuit below is operating as a *switch* or an *amplifier*.

(a) if

$$V_{GS} = 4v$$

and  $V_{DS} = 2v$

(b) if  $V_{GS} = 4v$  and  $V_{DS} = 6v$

- Remember for symbol and similar circuit for PMOS, read book pg 256 and 258

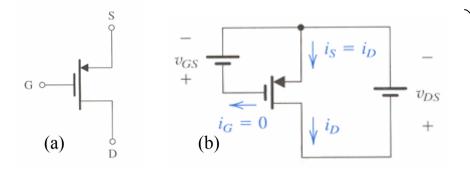

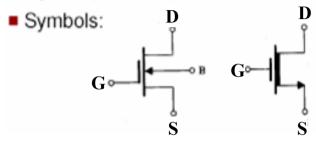

### **Physical Operation of Enhancement PMOS**: P-channel MOSFET.

(a) Simplified PMOS circuit symbol with connected source & body. (b) PMOS circuit. Note that  $v_{GS}$  and  $v_{DS}$  are negative and  $i_D$  flows out of drain Since in PMOS,  $V_t$  is negative, So  $v_{GS} \le V_t$  is used to induces a channel. Thus,  $v_{SG} \ge |V_t|$

#### To operate in **Triode region**:

$v_{DS} \ge v_{GS} - V_t \quad \text{(Continuous channel)}$  $i_D = k_p' \frac{W}{L} \left[ (v_{GS} - V_t) v_{DS} - \frac{1}{2} v_{DS}^2 \right]$

where  $v_{GS}$ ,  $V_t$ , and  $v_{DS}$  are negative and  $k'_p = \mu_p C_{ox}$

To operate in **Saturation region**:

$v_{DS} \le v_{GS} - V_t$  (Pinched-off channel) or  $v_{GD} > V_t$   $i_D = \frac{1}{2} k_p' \frac{W}{L} (v_{GS} - V_t)^2 (1 + \lambda v_{DS})$ Neglecting  $\lambda$ ,  $i_D = \frac{1}{2} k_p' \frac{W}{L} (v_{GS} - V_t)^2$

Thus to recap PMOS operation, the gate voltage has to be made lower than that of the source by at least  $|V_t|$ . To operate in Triode region, the drain voltage has to exceed the gate voltage by at least  $|V_t|$ , other wise the PMOS operates in Saturation region.

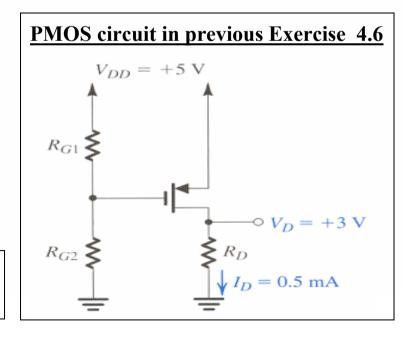

**Exa 4.6:** Design the circuit of Fig. 4.24 so that the transistor operates in saturation with  $I_D = 0.5$  mA and  $V_D = +3$  V. Let the enhancement-type PMOS transistor have  $V_t = -1$  V and  $k'_p(W/L) = 1$  mA/V<sup>2</sup>. Assume  $\lambda = 0$ . What is the largest value that  $R_D$  can have while maintaining saturation region operation?

#### The figure is given in next page:

**Sol:**  $V_{GS} = -2 \text{ V}$ :  $R_{G1} = 2 \text{ M}\Omega$  and  $R_{G2} = 3 \text{ M}\Omega$ .  $R_D = 8 \text{ k}\Omega$

Saturation until  $V_D + |V_t| > V_G$ See book pg 268 for solution

## **4.2.5 & 4.2.6: some Practical Considerations of Enhancement MOS**

#### The Body Effect

In ICs, the substrates of all NMOS are usually common and connected to the most negative power supply. If a source is not at this voltage level, the reverse-bias voltage  $V_{SB}$  between S and B will widen the depletion region and in turn reduces the channel depth. The result is an increase of  $V_t$ :

$$V_t = V_{t0} + \gamma \left( \sqrt{2\phi_f + V_{SB}} - \sqrt{2\phi_f} \right)$$

where  $V_t = V_{t0}$  with  $V_{SB} = 0$ ,

$\phi_f$  is a physical parameter with  $2\phi_f$  typically 0.6V, and  $\gamma$  is a fabrication - process parameter.

It follows that the body voltage controls i<sub>D</sub>; This is an undesired phenomenon know as the **body** effect.

#### Same situation exists in PMOS.

Body effect can cause considerable degradation in circuit performance (as shown in chapter 6 of book)

#### Temperature Effects

Both V<sub>t</sub> and k' are temperature sensitive. The magnitude of V<sub>t</sub> decrease by about 2mV for every 1°C rise in temperature. This decrease in  $|V_t|$  gives rise to a corresponding increase in drain current as temperature is increase. However, because k' decreases with temperature and its effect is a dominant one, <u>the</u> overall observed effect of a temperature increase is a decrease in drain current.

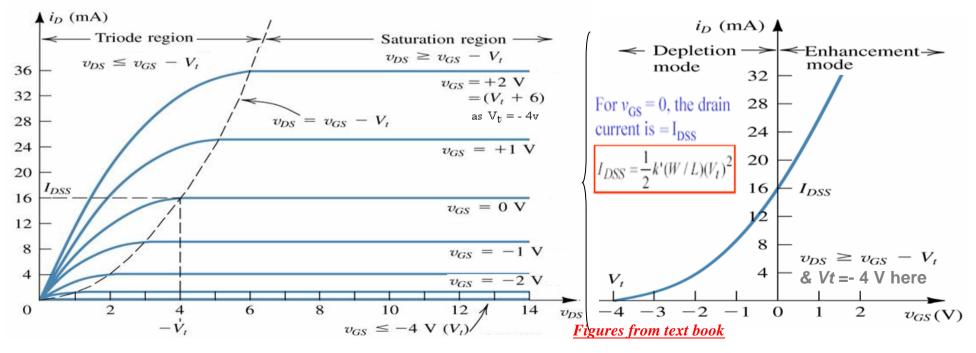

# **4.11: Depletion Type NMOS** or n-channel MOSFET's:

The depletion type MOSFET has similar structure to that of *enhancement* type but with a <u>physically</u> <u>implanted</u> channel (*instead of an induced channel*). Thus an n-channel depletion-type MOSFET always has an

n-type silicone region connecting the source and drain (both +n) at the top of the type substrate. Thus, for any

- Normally-ON device

- A thin n-channel layer is implanted

- V<sub>t</sub> is negative for NMOS

$v_{\rm DS}$  applied between the drain and source,  $i_{\rm D}$  flows even if  $v_{\rm GS} = 0$ . Thus, the channel depth and hence its conductivity is controlled by  $v_{\rm GS}$ . Applying a '+  $v_{\rm GS}$ ' enhances the channel by attracting more e<sup>-1</sup>'s. Applying '-  $v_{\rm GS}$ ' is said to deplete/reduce the channel.

#### **4.3: MOSFET circuits at DC:**

**EXAMPLE** Design the circuit of Fig. 4.20, so that the transistor operates at  $I_D = 0.4$  mA  $V_D = 1$  V. The NMOS transistor has  $V_f = 2$  V,  $\mu_n C_{ox} = 20 \ \mu A/V^2$ ,  $L = 10 \ \mu m$ , and  $W = 400 \ \mu m$ . Neglect the channel-length modulation effect (i.e., assume that  $\lambda = 0$ ).

Since  $V_D = 1$  V means operation in the saturation region, we use the saturation-region expression of  $i_D$  to determine the required value of  $v_{GS}$ ,  $a_{S} v_{CD} < V_{t}$

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_l)^2 \implies 0.4 = \frac{1}{2} \times 20 \times 10^{-3} \times \frac{400}{10} (V_{GS} - 2)^2$$

This equation yields two values for  $V_{GS}$ , 1 V and 3 V. The first value does not make physical sense since it is lower than  $V_r$ . Thus  $V_{GS} = 3$  V. Referring to Fig. 4.20, we note that the gate is at ground potential; thus the source must be at -3 V, and the required value of  $R_S$  can be determined from

A  $V_{DD} = 5 V$   $I_D \downarrow R_D$   $I_D \downarrow R_D$   $I_D \downarrow R_S$  $V_{SS} = -5 V$

$R_{S} = \frac{V_{S} - V_{SS}}{I_{D}} = \frac{-3 - (-5)}{0.4} \begin{cases} \text{To establish a dc voltage of } +1 \text{ V at the drain, we must select } R_{D} \text{ as } \\ R_{D} = \frac{V_{DD} - V_{D}}{I_{D}} = \frac{5 - 1}{0.4} = 10 \text{ k}\Omega \end{cases}$

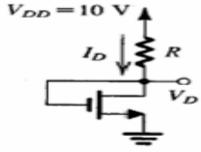

**EXAMPLE** Design the circuit to obtain a current  $I_D$  of 0.4 mA. Find the value required for R and find the dc voltage  $V_D$ . Let the NMOS transistor have  $V_t = 2 V$ ,  $\mu_n C_{ox} = 20 \ \mu \text{A/V}^2$ ,  $L = 10 \ \mu \text{m}$ , and  $W = 100 \ \mu \text{m}$ . Neglect the channel-length modulation effect (that is, assume  $\lambda = 0$ ).

**SOLUTION** Because  $V_{DG} = 0$ , the FET is operating in the saturation region. Thus  $I_{\rm D} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_l)^2$  $0.4 = \frac{1}{2} (20)(10^{-3})(100/10)(V_{GS} - 2)^2$

which yields two values for  $V_{GS}$ , namely 4 and 0. The second value obviously does not make physical sense since it is lower than  $V_t$ .

Thus  $V_{GS} = 4 \text{ V}$ , and the drain voltage will be  $V_D = +4 \text{ V}$

The required value for R can be found as follows:

vs:  $R = \frac{V_{DD} - V_D}{I_D} = \frac{10 - 4}{0.4} = 15 \text{ k}\Omega$

# **4.3: MOSFET circuits at DC:**

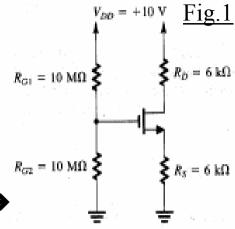

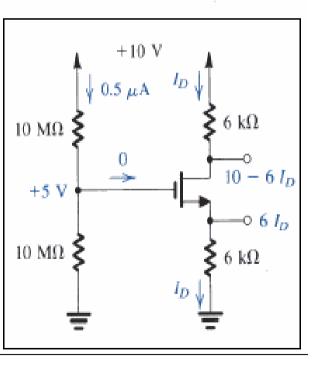

**EXAMPLE** Analyze the circuit shown to determine the voltages at all nodes and the currents through all branches. Let  $V_t = 1$  V and  $k'_n(W/L) = 1$  mA/V<sup>2</sup>. Neglect the channel-length modulation effect (i.e., assume  $\lambda = 0$ ).

**SOLUTION** Since the gate current is zero, the voltage at the gate is simply determined by the voltage divider formed by the two 10-M $\Omega$  resistors,

$$V_G = 10 \times \frac{10}{10 + 10} = +5 \text{ V} \implies V_{GS} = 5 - 6I_D \Rightarrow \text{Assume Saturated} \Rightarrow$$

Thus  $I_D = \frac{1}{2}k_n \frac{W}{L}(V_{GS} - V_t)^2 = \frac{1}{2} \times 1 \times (5 - 6I_D - 1)^2$

which results in the quadratic equation :  $18I_D^2 - 25I_D + 8 = 0$

This equation yields two values for  $I_D$ : 0.89 mA and 0.5 mA. The first value results in a source voltage of 6 × 0.89 = 5.34, which is greater than the gate voltage and does not make physical sense. Thus  $as \quad \{v_{GS} = (v_G - v_S)\} > V_t$

$$I_D = 0.5 \text{mA}$$

$$V_S = 0.5 \times 6 = +3\text{V}$$

$$V_{GS} = 5 - 3 = 2\text{V}$$

$$V_D = 10 - 6 \times 0.5 = +7\text{V}$$

Since  $V_D > V_G - V_t$ , the transistor is operating in saturation, as initially assumed.

**Exercise-2**: Solve the above problem in Fig.1, after replacing NMOS with PMOS (*Pchannel MOSFET*) with  $V_{t(PMOS)} = -1v$ . *Hint: see example 4.5 (NMOS) & 4.6 (PMOS) solutions*

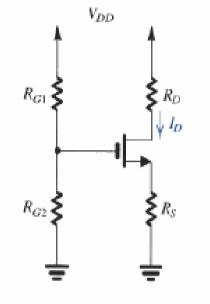

# Summary of DC biasing a MOS amplifier in discrete circuits:

$V_{DD}$

$R_{D}$

$\sum R_{s}$

- Single power suppler

Since I<sub>G</sub>=0, R<sub>G1</sub> and

R<sub>G2</sub> can be very large, allowing large R<sub>in</sub>

- R<sub>s</sub> provides negative feedback

- R<sub>D</sub> should be large for high gain and should be small for large signal swing.

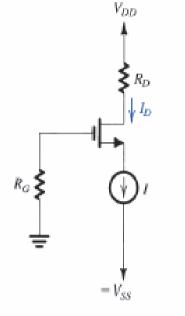

- Two power suppliers

- Simpler bias arrangement.

**₹** R<sub>G</sub>

R<sub>G</sub> establishes a dc ground and presents a high input resistance to a signal that may be capaci-tively coupled to the gate.

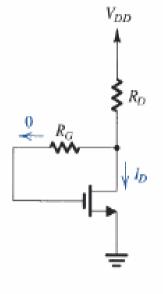

- Even simpler and more direct bias.

- A constant-current source I feeds the source terminal.

- Large resistor R<sub>G</sub> forces the V<sub>G</sub> to be equal to V<sub>D</sub>.

The output signal

- swing should be limited in the negative direction to |V<sub>t</sub>|.

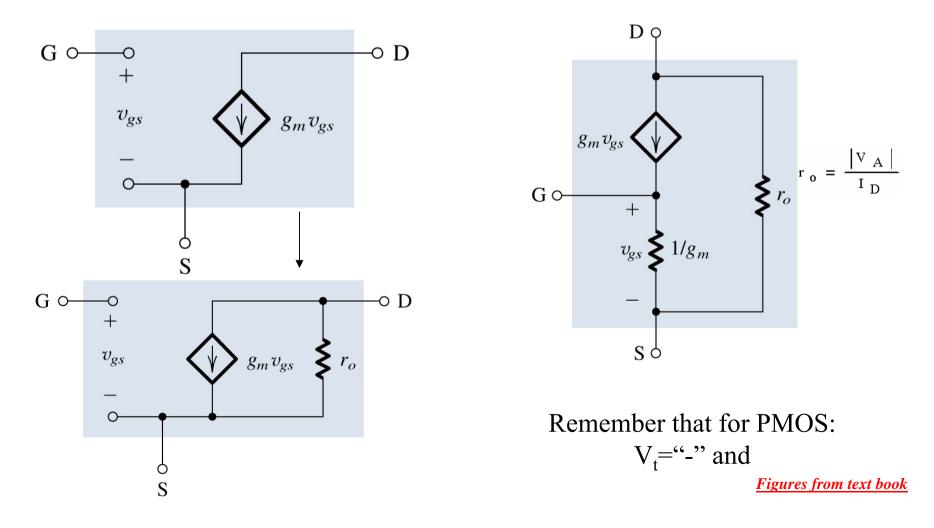

# **4.6: Small signal models for MOSFET amplifier:**

- (a) neglecting the dependence of  $i_D$  on  $v_{DS}$  in saturation region of operation (channel-length modulation effect);

- (b) including the effect of channel-length modulation modeled by output resistor  $(r_o)$

- (c) T-model with output resistance,  $r_o = /V_A / / I_D = 1 / (\lambda . I_D)$

MOSFET transconductance

Formula 1:  $g_m = k'_n \frac{W}{L} (V_{GS} - V_t)$ It indicates that  $g_m$  is proportional to the k', W/L ratio and  $(V_{GS} - V_t)$ However, a large V<sub>GS</sub> reduces the allowable signal swing at the drain.

Formula 2:

$$g_m = \sqrt{2k'_n} \sqrt{\frac{W}{L}} \sqrt{I_D}$$

It shows:

- for a given MOSFET, g<sub>m</sub> ∞ the square root of the dc bias current.

- (2) At a given bias current, g<sub>m</sub> ∞ W / L

In contrast, the  $g_m$  of BJT  $\infty$  the biasing current  $I_c$  and is independent of the geometry.

Remember for PMOS, the calculation of  $g_m$ ,  $r_o$  and  $K'_n$  is calculated using  $|(V_{gs}-V_t)|$ ,  $|V_A|$  or  $|\lambda|$  and replacing  $\mu_n$  with  $\mu_p$ , respectively. See book page 297

*Here for NMOS*  $\rightarrow K'_n = \mu_n C_{ox}$

📫 Formula 3:

$$g_m = \frac{I_D}{\left(V_{GS} - V_t\right)/2}$$

As compared with that of BJT, for which  $g_m = \frac{I_C}{V_T}$

The transconductance value for MOSFET is much small than that of BJT in light of the fact that the values of (V<sub>GS</sub>-V<sub>t</sub>)/2 are at least 0.1 V or so.

In spite of their low g<sub>m</sub>, MOSFETs have many other advantages, such as high R<sub>in</sub>, small size, low power dissipation and ease of fabrication.

#### **MOSFET As An Amplifier – Small-Signal Analysis:**

Example 4.10

Figure 4.38 (a) shows a discrete enhancement MOSFET amplifier in which the input signal  $v_i$  is coupled to the gate via a large capacitor, and the output signal at the drain is coupled to the load resistance  $R_L$  via another large capacitor. We wish to analyze this amplifier circuit to determine its small-signal voltage gain and its input resistance. The transistor has  $V_t = 1.5 \text{ V}, k'_n(W/L) = 0.25 \text{ mA/V}^2$ , and  $V_A = 50 \text{ V}$ . Assume the coupling capacitors to be sufficiently large so as to act as short circuits at the signal frequencies of interest.

+15 V

#### Solution

We first evaluate the dc operating point as follows.  $R_D = 10 \text{ k}\Omega$ As  $I_G=0$ ,  $V_{R_G}=V_{10M}=0$ , Thus  $V_G=V_D$ . Since  $V_S=0$ ;  $V_{GS}=V_{DS}$ transistor must operate in saturation region as  $V_{DS} > (V_{GS} - V_t)$ = 10 MΩ **\$**  $R_L = 10 \text{ k}\Omega$  $I_D = \frac{1}{2} \times 0.25 (V_{CS} - 1.5)^2$  $v_i$  $I_D = \frac{1}{2} \times 0.25 (V_D - 1.5)^2$ DC  $V_{\rm D} = 15 - R_{\rm D}I_{\rm D} = 15 - 10I_{\rm D}$ Rin D Two solutions: I<sub>D1</sub> = 1.0589 mA and V<sub>D</sub> = 4.4 V  $I_{D2} = 1.721 \text{ mA and } V_{D} < 0$ ₹r.  $\{ R_D \}$ which is not physically meaningful Sm Ver ! So,  $V_D = (15 - i_D * 10K) = 4.4 \text{ v} \rightarrow V_{DS} \rightarrow V_{GS}$ s R:...

The value of  $g_m$  is given by  $g_m = k'_n \frac{W}{L} (V_{GS} - V_t)$ = 0.25(4.4 - 1.5) = 0.725 mA/V

$$r_o = \frac{V_A}{I_D} = \frac{50}{1.06} = 47 \, k\Omega$$

Since  $v_{gs} = v_i$ , the voltage gain is

$\frac{v_o}{v_i} = -g_m (R_D //R_L //r_o)$ = -0.725(10//10//47) = -3.3 V/V

To evaluate the input resistance  $R_{in}$ , we note that the input current  $i_i$

Since R<sub>G</sub> is very large (10MΩ), the current through it can be neglected

$$v_o \approx -g_m v_{gs} (R_D // R_L // r_o)$$

Thus,

$i_{i} = (v_{i} - v_{o})/R_{G}$ =  $\frac{v_{i}}{R_{G}} \left(1 - \frac{v_{o}}{v_{i}}\right)$ =  $\frac{v_{i}}{R_{G}} [1 - (-3.3)] = \frac{4.3 v_{i}}{R_{G}}$

$$R_{\rm in} = \frac{v_l}{i_l} = \frac{R_G}{4.3} = \frac{10}{4.3} = 2.33 \,\mathrm{M}\Omega$$

- Remember channel length modulation is neglected in this solution.

- Solve exercise 4.24, 4.28 and hand-in next class.

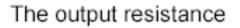

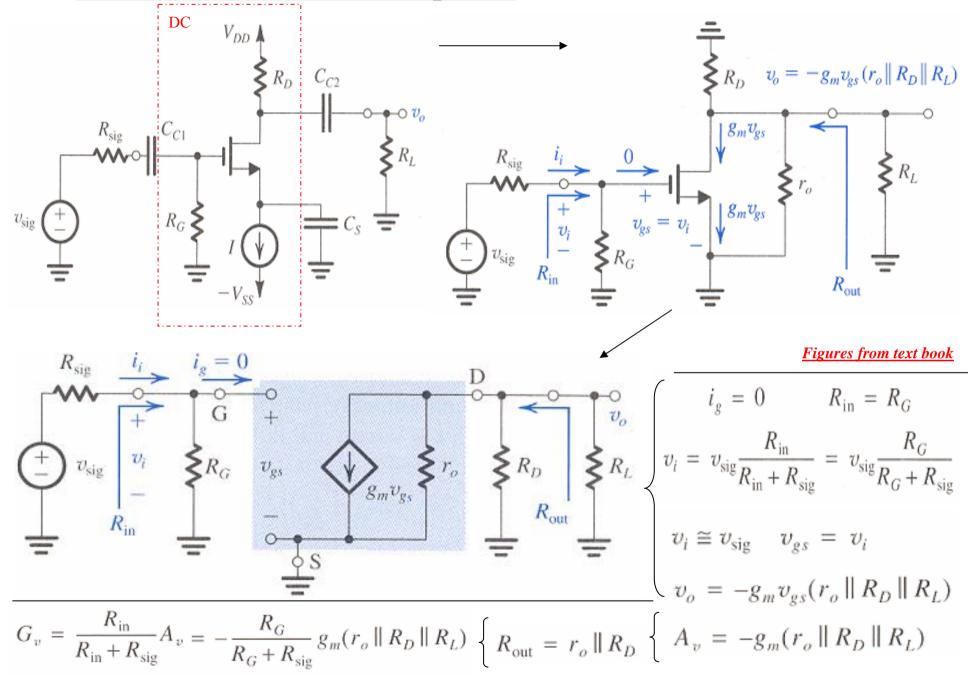

4.7: Common Source (CS) Amplifier: Single stage MOS Analysis

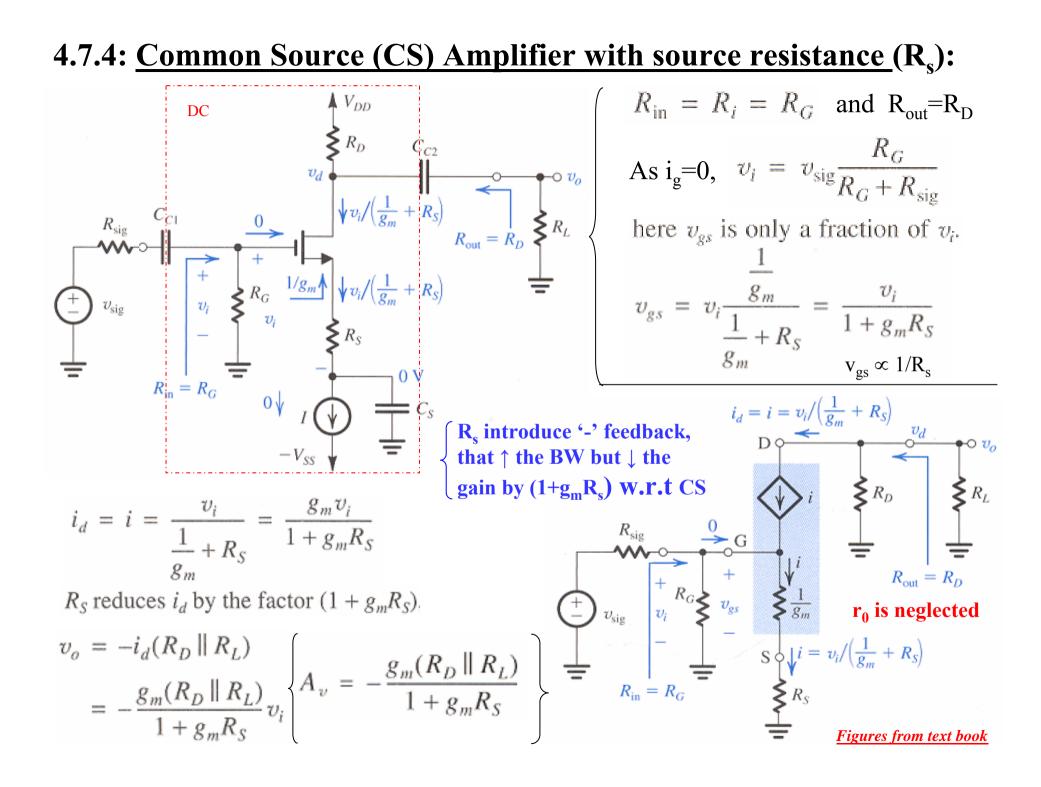

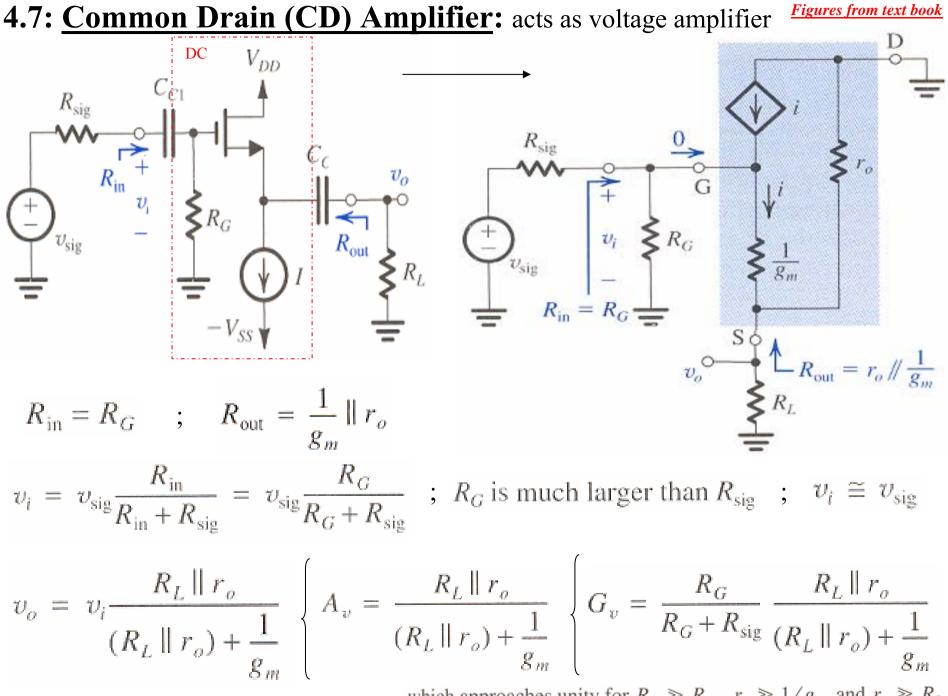

4.7: Common Gate (CG) Amplifier: acts as Unity gain current amplifier

which approaches unity for  $R_G \ge R_{sig}$ ,  $r_o \ge 1/g_m$ , and  $r_o \ge R_L$ .

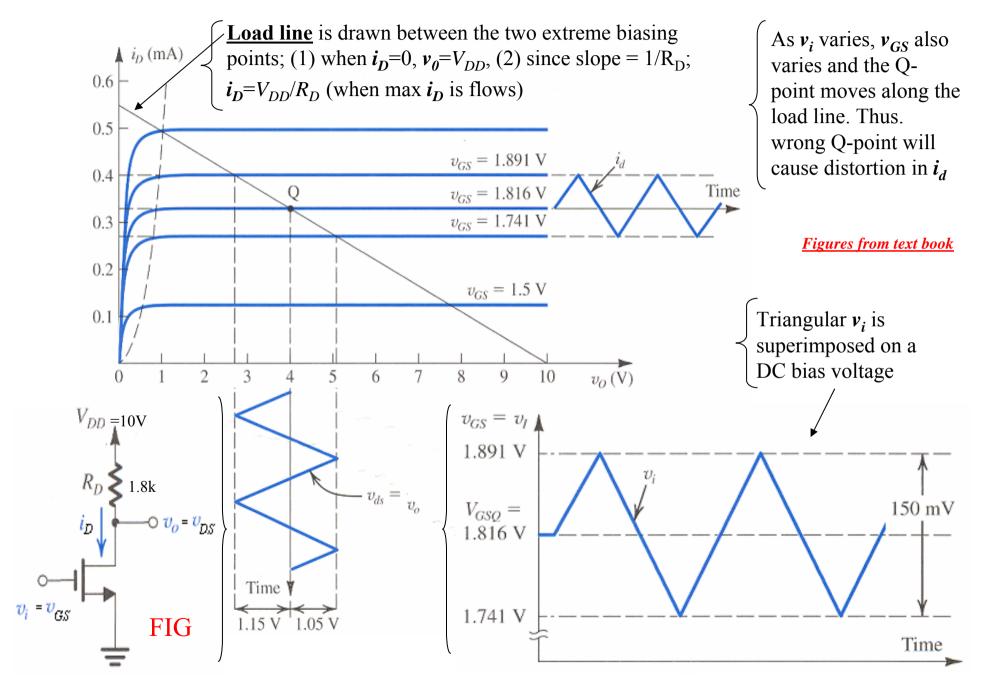

#### 4.4.4: Operation as a linear Amplifier: see page 279 of book for more explanation