|       |                           | ails of th       |              |                 |                 | ubb              |                  |      |

|-------|---------------------------|------------------|--------------|-----------------|-----------------|------------------|------------------|------|

| Instr | uction                    | Meaning          |              |                 | Fo              | rmat             |                  |      |

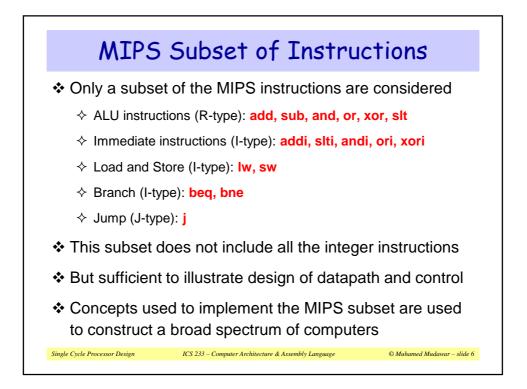

| add   | rd, rs, rt                | addition         | $0p^{6} = 0$ | rs <sup>5</sup> | rt <sup>5</sup> | rd <sup>5</sup>  | 0                | 0x20 |

| sub   | rd, rs, rt                | subtraction      | $0p^{6} = 0$ | rs <sup>5</sup> | rt <sup>5</sup> | rd <sup>5</sup>  | 0                | 0x22 |

| and   | rd, rs, rt                | bitwise and      | $0p^{6} = 0$ | rs <sup>5</sup> | rt <sup>5</sup> | rd <sup>5</sup>  | 0                | 0x24 |

| or    | rd, rs, rt                | bitwise or       | $0p^{6} = 0$ | rs⁵             | rt <sup>5</sup> | rd <sup>5</sup>  | 0                | 0x25 |

| xor   | rd, rs, rt                | exclusive or     | $0p^{6} = 0$ | rs <sup>5</sup> | rt <sup>5</sup> | rd <sup>5</sup>  | 0                | 0x26 |

| slt   | rd, rs, rt                | set on less than | $0p^{6} = 0$ | rs⁵             | rt <sup>5</sup> | rd <sup>5</sup>  | 0                | 0x2a |

| addi  | rt, rs, im <sup>16</sup>  | add immediate    | 0x08         | rs⁵             | rt <sup>5</sup> | im <sup>16</sup> |                  |      |

| slti  | rt, rs, im <sup>16</sup>  | slt immediate    | 0x0a         | rs⁵             | rt <sup>5</sup> | im <sup>16</sup> |                  |      |

| andi  | rt, rs, im <sup>16</sup>  | and immediate    | 0x0c         | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup> |                  |      |

| ori   | rt, rs, im <sup>16</sup>  | or immediate     | 0x0d         | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup> |                  |      |

| xori  | rt, im <sup>16</sup>      | xor immediate    | 0x0e         | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup> |                  |      |

| lw    | rt, im <sup>16</sup> (rs) | load word        | 0x23         | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup> |                  |      |

| SW    | rt, im <sup>16</sup> (rs) | store word       | 0x2b         | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup> |                  |      |

| beq   | rs, rt, im <sup>16</sup>  | branch if equal  | 0x04         | rs <sup>5</sup> | rt <sup>5</sup> |                  | im <sup>16</sup> |      |

| bne   | rs, rt, im <sup>16</sup>  | branch not equal | 0x05         | rs <sup>5</sup> | rt <sup>5</sup> |                  | im <sup>16</sup> |      |

| i     | im <sup>26</sup>          | jump             | 0x02         |                 |                 | im <sup>2</sup>  | 6                |      |

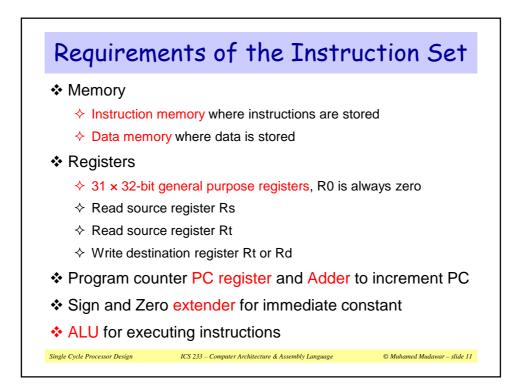

| Regi                             | ister Transfer Level (R                                                                                                                                                                      | TL)                       |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| ✤ RTL is a d                     | description of data flow between regi                                                                                                                                                        | sters                     |

| ✤ RTL gives                      | a meaning to the instructions                                                                                                                                                                |                           |

| <ul> <li>All instruct</li> </ul> | tions are fetched from memory at ac                                                                                                                                                          | ldress PC                 |

| Instruction                      | RTL Description                                                                                                                                                                              |                           |

| ADD                              | $\text{Reg}(\text{Rd}) \leftarrow \text{Reg}(\text{Rs}) + \text{Reg}(\text{Rt});$                                                                                                            | $PC \gets PC + 4$         |

| SUB                              | $Reg(Rd) \leftarrow Reg(Rs) - Reg(Rt);$                                                                                                                                                      | $PC \gets PC + 4$         |

| ORI                              | $Reg(Rt) \leftarrow Reg(Rs)   zero_ext(Im16);$                                                                                                                                               | $PC \gets PC + 4$         |

| LW                               | $Reg(Rt) \leftarrow MEM[Reg(Rs) + sign_ext(Im16)];$                                                                                                                                          | $PC \leftarrow PC + 4$    |

| SW                               | $MEM[Reg(Rs) + sign\_ext(Im16)] \leftarrow Reg(Rt);$                                                                                                                                         | $PC \leftarrow PC + 4$    |

| BEQ                              | if $(\text{Reg}(\text{Rs}) == \text{Reg}(\text{Rt}))$<br>$\text{PC} \leftarrow \text{PC} + 4 + 4 \times \text{sign} \text{extend}(\text{Im16})$<br>else $\text{PC} \leftarrow \text{PC} + 4$ |                           |

| Single Cycle Processor Design    | ICS 233 – Computer Architecture & Assembly Language ©                                                                                                                                        | Muhamed Mudawar – slide 8 |

|             |      |                                                                                                      | re Executed in Steps                                                                                                                                                                                                                                                                                                |

|-------------|------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

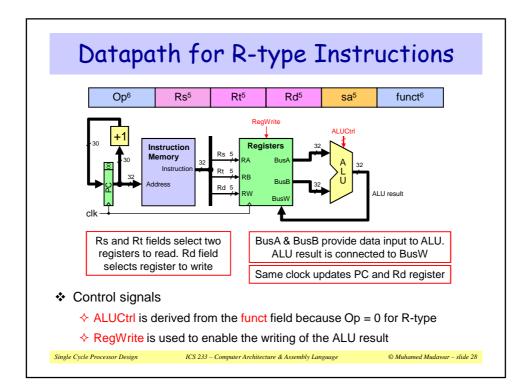

| <b>∻</b> R- | type | Fetch instruction:<br>Fetch operands:<br>Execute operation:<br>Write ALU result:<br>Next PC address: | $\begin{array}{l} \text{Instruction} \leftarrow \text{MEM[PC]} \\ \text{data1} \leftarrow \text{Reg(Rs)},  \text{data2} \leftarrow \text{Reg(Rt)} \\ \text{ALU\_result} \leftarrow \text{func(data1, data2)} \\ \text{Reg(Rd)} \leftarrow \text{ALU\_result} \\ \text{PC} \leftarrow \text{PC} + 4 \end{array}$     |

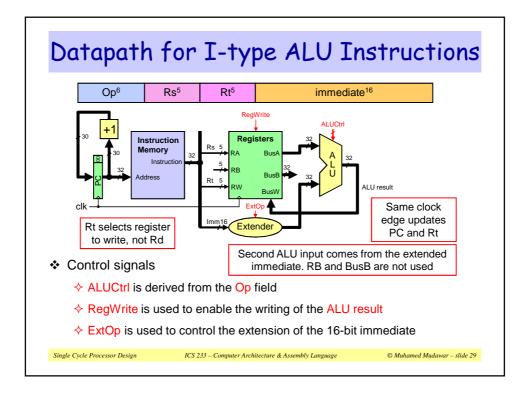

| ✤ I-tỳ      | ype  | Fetch instruction:<br>Fetch operands:<br>Execute operation:<br>Write ALU result:<br>Next PC address: | $\begin{array}{l} \text{Instruction} \leftarrow \text{MEM[PC]} \\ \text{data1} \leftarrow \text{Reg(Rs)},  \text{data2} \leftarrow \text{Extend(imm16)} \\ \text{ALU\_result} \leftarrow \text{op(data1, data2)} \\ \text{Reg(Rt)} \leftarrow \text{ALU\_result} \\ \text{PC} \leftarrow \text{PC} + 4 \end{array}$ |

| ♦ BE        | EQ   | Fetch instruction:<br>Fetch operands:<br>Equality:<br>Branch:                                        | Instruction $\leftarrow$ MEM[PC]<br>data1 $\leftarrow$ Reg(Rs), data2 $\leftarrow$ Reg(Rt)<br>zero $\leftarrow$ subtract(data1, data2)<br>if (zero) PC $\leftarrow$ PC + 4 + 4xsign_ext(imm16)<br>else PC $\leftarrow$ PC + 4                                                                                       |

| ✤ LW   | Fetch instruction:<br>Fetch base register:<br>Calculate address: | Instruction ← MEM[PC]<br>base ← Reg(Rs)                    |

|--------|------------------------------------------------------------------|------------------------------------------------------------|

|        | Read memory:                                                     | address ← base + sign_extend(imm16)<br>data ← MEM[address] |

|        | Write register Rt:                                               | $\text{Reg}(\text{Rt}) \leftarrow \text{data}$             |

|        | Next PC address:                                                 | $PC \leftarrow PC + 4$                                     |

| ✤ SW   | Fetch instruction:                                               | Instruction ← MEM[PC]                                      |

|        | Fetch registers:                                                 | base $\leftarrow$ Reg(Rs), data $\leftarrow$ Reg(Rt)       |

|        | Calculate address:                                               | address ← base + sign_extend(imm16)                        |

|        | Write memory:                                                    | MEM[address] ← data                                        |

|        | Next PC address:                                                 | $PC \leftarrow PC + 4$                                     |

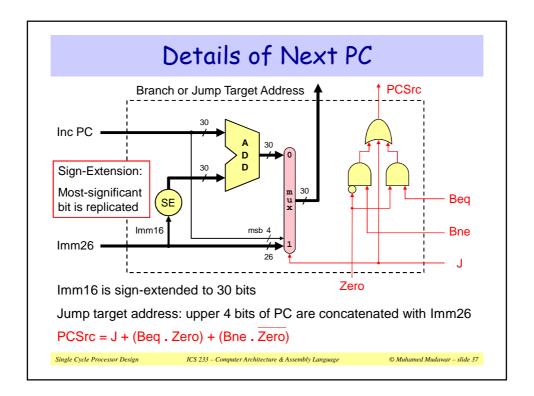

|        |                                                                  | concatenation                                              |

| 💠 Jump | Fetch instruction:                                               | Instruction $\leftarrow$ MEM[PC] /                         |

|        | Target PC address:                                               | target ← PC[31:28]    Imm26    '00'                        |

|        | Jump:                                                            | PC ← target                                                |

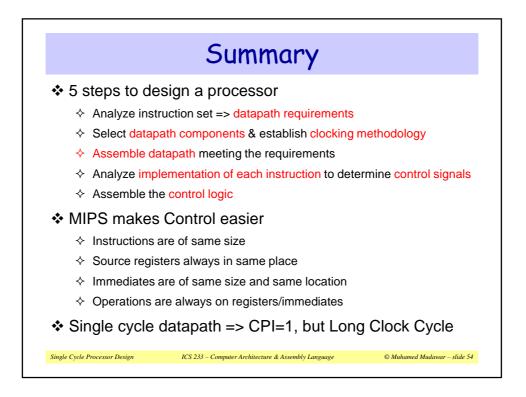

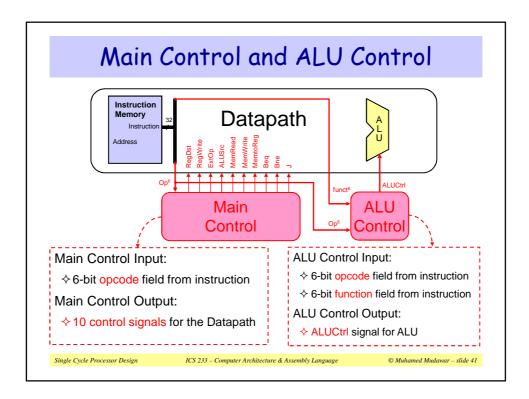

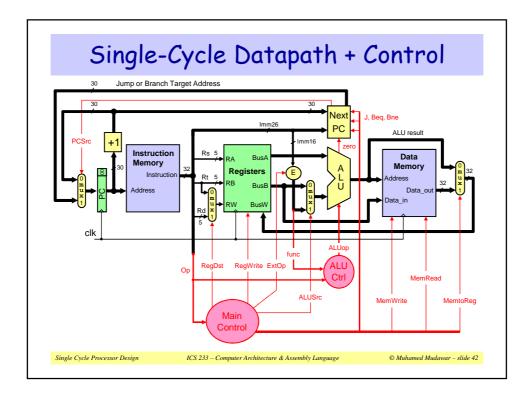

| Main Control Signals |                                                                      |                                                             |  |  |  |  |  |

|----------------------|----------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|

| Signal               | Effect when '0'                                                      | Effect when '1'                                             |  |  |  |  |  |

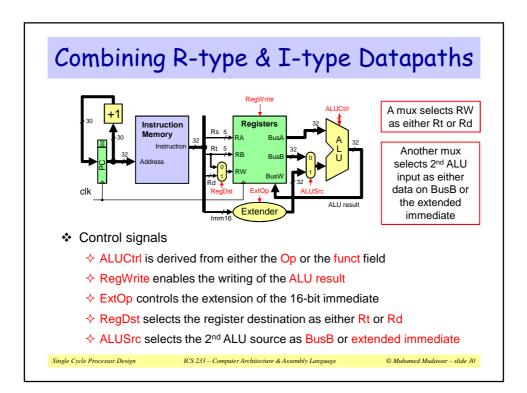

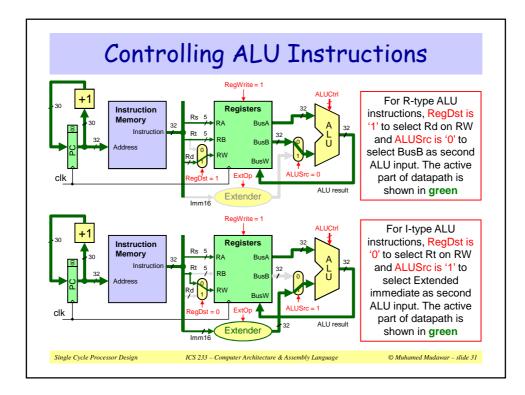

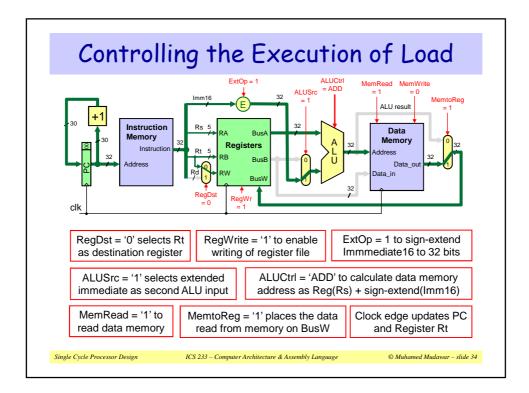

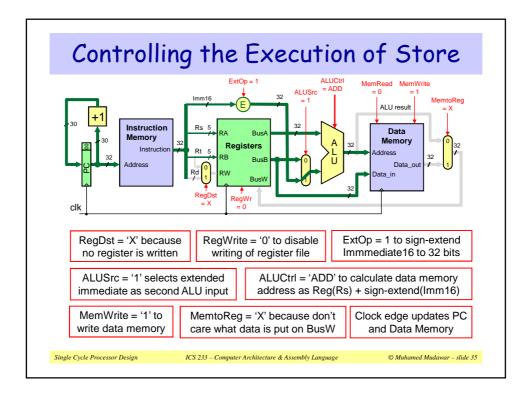

| RegDst               | Destination register = Rt                                            | Destination register = Rd                                   |  |  |  |  |  |

| RegWrite             | None                                                                 | Destination register is written with the data value on BusW |  |  |  |  |  |

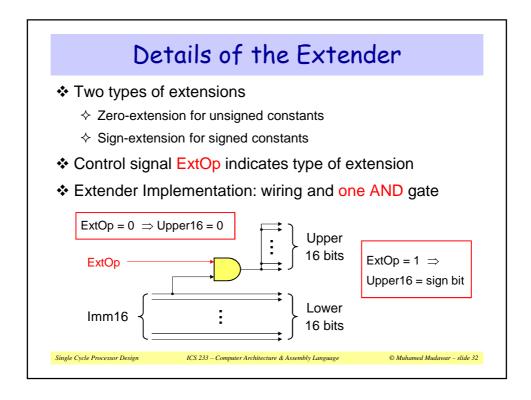

| ExtOp                | 16-bit immediate is zero-extended                                    | 16-bit immediate is sign-extended                           |  |  |  |  |  |

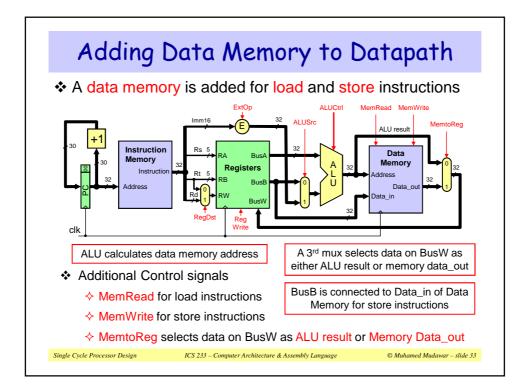

| ALUSrc               | Second ALU operand comes from the second register file output (BusB) | Second ALU operand comes from the extended 16-bit immediate |  |  |  |  |  |

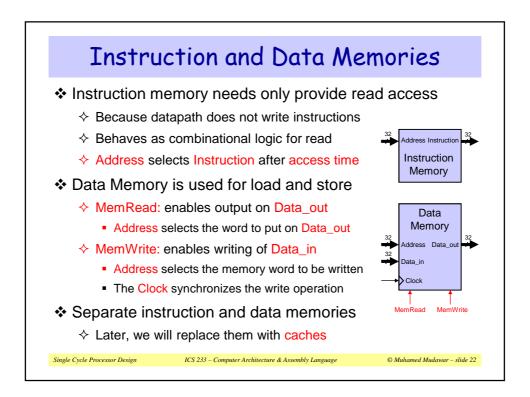

| MemRead              | None                                                                 | Data memory is read<br>Data_out ← Memory[address]           |  |  |  |  |  |

| MemWrite             | None                                                                 | Data memory is written<br>Memory[address] ← Data_in         |  |  |  |  |  |

| MemtoReg             | BusW = ALU result                                                    | BusW = Data_out from Memory                                 |  |  |  |  |  |

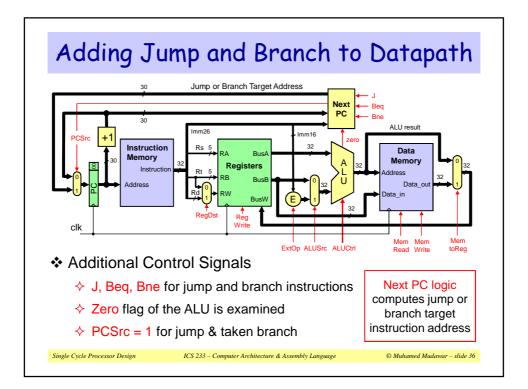

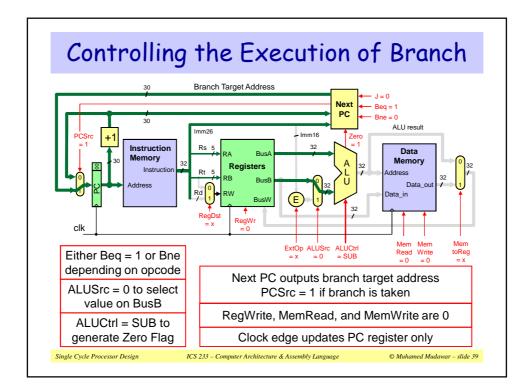

| Beq, Bne             | PC ← PC + 4                                                          | $PC \leftarrow Branch target address$<br>If branch is taken |  |  |  |  |  |

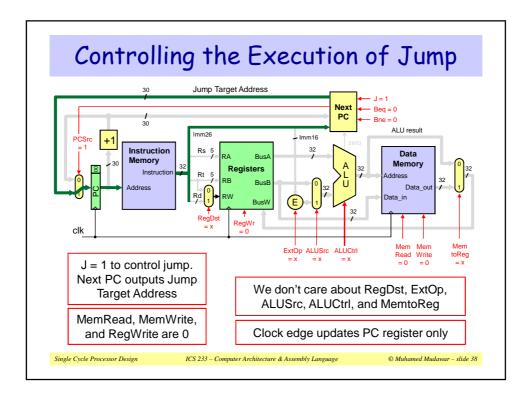

| J                    | $PC \leftarrow PC + 4$                                               | PC ← Jump target address                                    |  |  |  |  |  |

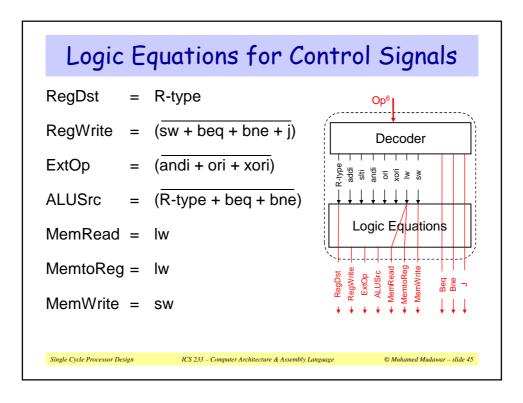

| Ор     | Reg<br>Dst | Reg<br>Write | Ext<br>Op | ALU<br>Src | Beq | Bne | J | Mem<br>Read | Mem<br>Write | Mem<br>toReg |

|--------|------------|--------------|-----------|------------|-----|-----|---|-------------|--------------|--------------|

| R-type | 1 = Rd     | 1            | х         | 0=BusB     | 0   | 0   | 0 | 0           | 0            | 0            |

| addi   | 0 = Rt     | 1            | 1=sign    | 1=lmm      | 0   | 0   | 0 | 0           | 0            | 0            |

| slti   | 0 = Rt     | 1            | 1=sign    | 1=lmm      | 0   | 0   | 0 | 0           | 0            | 0            |

| andi   | 0 = Rt     | 1            | 0=zero    | 1=lmm      | 0   | 0   | 0 | 0           | 0            | 0            |

| ori    | 0 = Rt     | 1            | 0=zero    | 1=lmm      | 0   | 0   | 0 | 0           | 0            | 0            |

| xori   | 0 = Rt     | 1            | 0=zero    | 1=lmm      | 0   | 0   | 0 | 0           | 0            | 0            |

| lw     | 0 = Rt     | 1            | 1=sign    | 1=lmm      | 0   | 0   | 0 | 1           | 0            | 1            |

| SW     | х          | 0            | 1=sign    | 1=lmm      | 0   | 0   | 0 | 0           | 1            | х            |

| beq    | х          | 0            | х         | 0=BusB     | 1   | 0   | 0 | 0           | 0            | х            |

| bne    | х          | 0            | х         | 0=BusB     | 0   | 1   | 0 | 0           | 0            | х            |

| j      | х          | 0            | х         | х          | 0   | 0   | 1 | 0           | 0            | х            |

|                 |                    |         |          | uth Table                    |

|-----------------|--------------------|---------|----------|------------------------------|

| In              | put                | Output  | 4-bit    |                              |

| Op <sup>6</sup> | funct <sup>6</sup> | ALUCtrl | Encoding |                              |

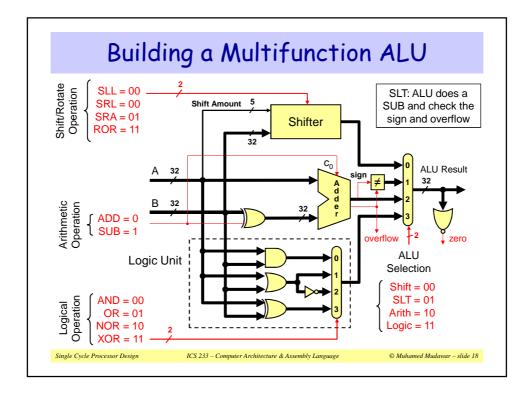

| R-type          | add                | ADD     | 0000     |                              |

| R-type          | sub                | SUB     | 0010     | The 4-bit ALUCtrl is         |

| R-type          | and                | AND     | 0100     | encoded according to the     |

| R-type          | or                 | OR      | 0101     | ALU implementation           |

| R-type          | xor                | XOR     | 0110     |                              |

| R-type          | slt                | SLT     | 1010     | Other ALU control            |

| addi            | х                  | ADD     | 0000     | encodings are also           |

| slti            | х                  | SLT     | 1010     | possible. The idea is to     |

| andi            | х                  | AND     | 0100     | choose a binary encoding     |

| ori             | х                  | OR      | 0101     | that will simplify the logic |

| xori            | х                  | XOR     | 0110     | that will simplify the logic |

| lw              | х                  | ADD     | 0000     |                              |

| SW              | х                  | ADD     | 0000     |                              |

| beq             | х                  | SUB     | 0010     |                              |

| bne             | х                  | SUB     | 0010     |                              |

| i               | х                  | х       | х        |                              |

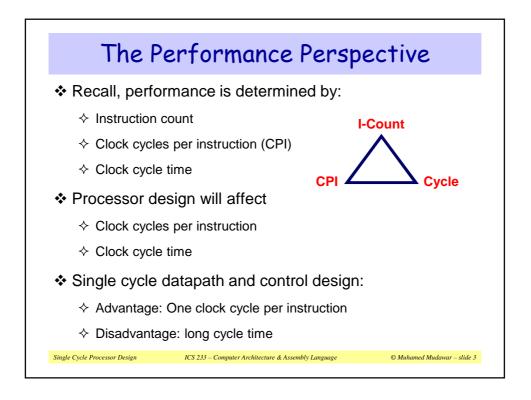

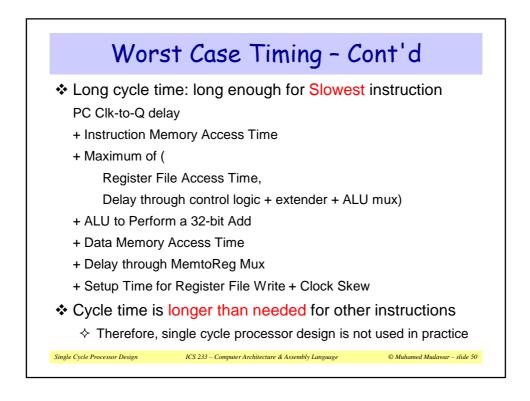

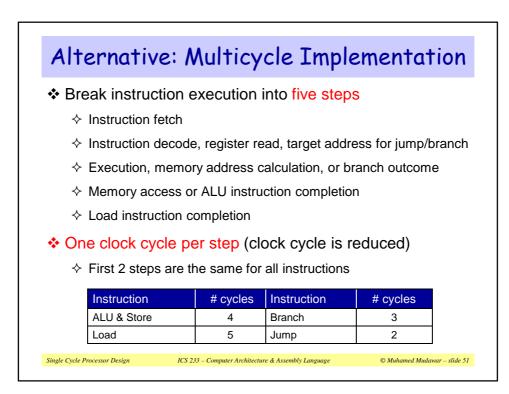

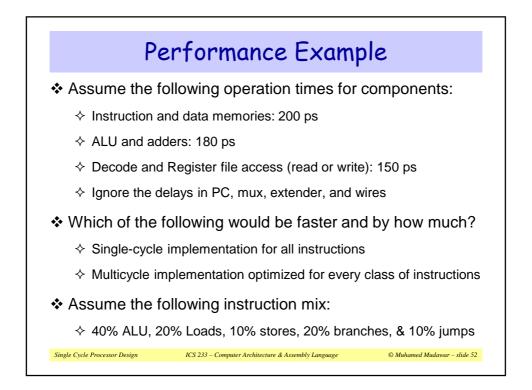

|                                           |                                               |                                           | Soluti           | on                |                   |             |  |

|-------------------------------------------|-----------------------------------------------|-------------------------------------------|------------------|-------------------|-------------------|-------------|--|

| Instruction<br>Class                      | Instruction<br>Memory                         | Register<br>Read                          | ALU<br>Operation | Data<br>Memory    | Register<br>Write | Total       |  |

| ALU                                       | 200                                           | 150                                       | 180              |                   | 150               | 680 ps      |  |

| Load                                      | 200                                           | 150                                       | 180              | 200               | 150               | 880 ps      |  |

| Store                                     | 200                                           | 150                                       | 180              | 200               |                   | 730 ps      |  |

| Branch                                    | 200                                           | 200 150 180 ← Compare and write PC 530 ps |                  |                   |                   |             |  |

| Jump 200 150 ← Decode and write PC 350 ps |                                               |                                           |                  |                   |                   |             |  |

| ♦ Clo                                     | ed single-c<br>ock cycle = 8<br>ulti-cycle im | 380 ps dete                               | ermined by I     | :<br>ongest delay | (load instru      | uction)     |  |

|                                           |                                               | •                                         |                  |                   |                   |             |  |

| ♦ Clo                                     | ock cycle = r                                 | nax (200, <sup>-</sup>                    | 150, 180) = 2    | 200 ps (maxi      | mum delay         | at any step |  |

| ♦ Av                                      | erage CPI =                                   | 0.4×4 + 0                                 | .2×5 + 0.1×4     | 4+ 0.2×3 + 0.     | 1×2 = 3.8         |             |  |

|                                           | a 088 = au                                    | s / (3.8 ×                                | 200 ps) = 8      | 880 / 760 =       | 1.16              |             |  |