# EE 200- Digital Logic Circuit Design 3.6 NAND and NOR Implementation

Dr. Muhammad Mahmoud

جامعة الملك فهد للبترول والمعادن King Fahd University of Petroleum & Minerals

October 3, 2013

#### Introduction

• Can you give an example of don't-care condition

#### Lecture Outline

- 1 The Map Method

- NAND Implementation

- NOR Implementation

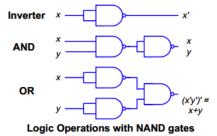

## NAND Implementation

Using NAND instead of AND and OR.

#### NAND Implementation

Alternative graphic symbol for NAND gate.

Two Graphic Symbols for NAND gate

#### Two-Level Implementation with NAND

Must have the function as sum-of-products.

The Map Method

• F = AB + CD

#### Two-Level Implementation with NAND

The Map Method

•

$$F = ((AB)'(CD)')' = AB + CD$$

## Two-Level Implementation (Example)

The Map Method

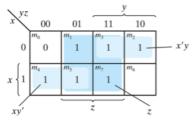

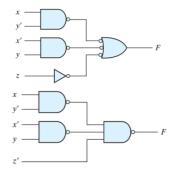

• Implement F using NAND gates F(x, y, z) = (1, 2, 3, 4, 5, 7)

• F = xy' + x'y + z

# Two-Level Implementation (Example)

The Map Method

$$F = xy' + x'y + z$$

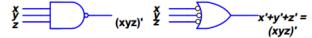

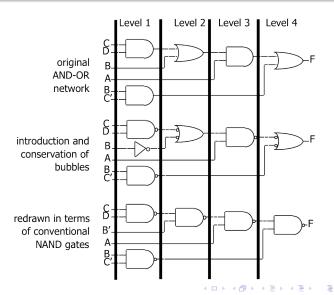

#### Multi-Level Implementation with NAND

The Map Method

$$F = A(CD + B) + BC'$$

$$C$$

$$D$$

$$B$$

$$C$$

$$C$$

$$D$$

$$B$$

$$C$$

$$C$$

$$D$$

$$B$$

$$A$$

$$B$$

$$C$$

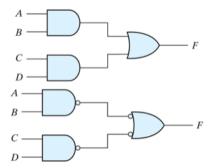

#### Multi-Level Implementation with NAND

•

$$F = (AB' + A'B)(C + D')$$

A

B

C

D

AND-OR gates

NAND zates

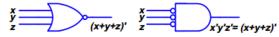

## Multi-Level Implementation with NAND (HOW TO)

- Convert all AND gates to NAND gates with AND-invert symbol.

- Convert all OR gates to NAND gates with invert-OR symbol.

- Make sure that every bubble is compensated with another on the same line, if not, insert an inverter.

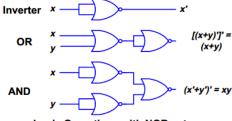

## NOR Implementation

Using NOR instead of AND and OR.

**Logic Operations with NOR gates**

### NAND Implementation

Alternative graphic symbol for NOR gate.

Two graphic symbols for NOR gate

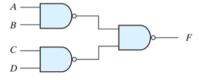

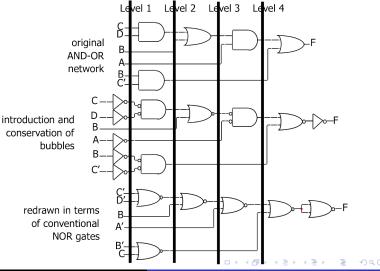

# NOR Implementation

•

$$F = (A + B)(C + D)E$$

A

B

C

D

E'

# NOR Implementation

•

$$F = (AB' + A'B)(C + D')$$

The Map Method

#### AND-OR to NAND Conversion

#### AND-OR to NOR Conversion

# Summary

- 1 The Map Method

- NAND Implementation

- NOR Implementation

#### Next Lecture

- XOR

- HDL