## COE360 – Assignment # 9 (out of 20) Dr. M. Elrabaa (052) (individual submission)

Use a 1  $\mu$ m technology with V<sub>DD</sub>=5V, C<sub>ox</sub>=2 fF/ $\mu$ m<sup>2</sup>,  $\varepsilon_{rox}$ = 4,  $\varepsilon_{rSi}$ = 12,  $\varepsilon_{o}$ = 8.85E-14 F/cm,  $\mu_{n}$ =600 cm<sup>2</sup>/S·V,  $\mu_{p}$ =300 cm<sup>2</sup>/S·V, I<sub>Dsat\_nmos</sub>= 500  $\mu$ A/ $\mu$ m, I<sub>Dsat\_nmos</sub>= 250  $\mu$ A/ $\mu$ m, V<sub>tn</sub> = |V<sub>tp</sub>| = 0.8 V, and q=1.6E-19 C.

## No group submission will be accepted for this assignment!

- Q1) Design a non-inverting (i.e. with even number of stages) CMOS buffer chain with an input capacitance of 35 fF to drive a load of 3.5 pF with minimum delay and equal noise margins and rise and fall delays.

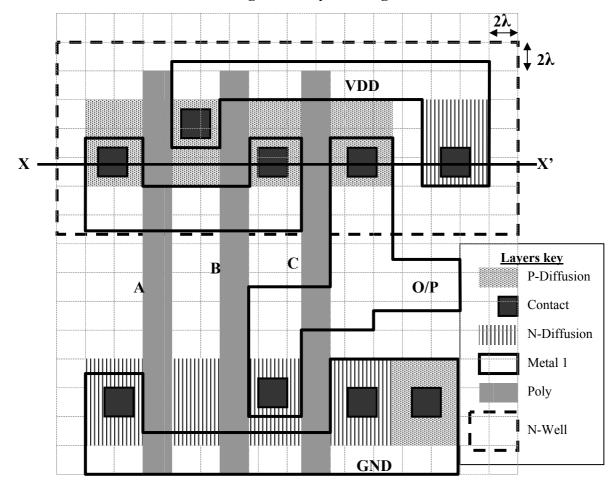

- Q2) The following layout is of a CMOS circuit:

- 1. Obtain the circuit schematic with transistors sizes (W/L) <u>in microns</u> (assume a 1μ m technology)

- 2. What is the function of this circuit?

- 3. Draw a crossection showing all the layers along the line X-X'

Q3) Obtain the symbolic layout of an AOI 122 CMOS gate then draw the layout in Magic. Make all NMOS and PMOS transistors equal in size. Use the following formula to obtain Wn (then set Wp=2 Wn): Wn = your student ID # Mod 7

i.e. Divide your student ID# by 7 then take the remainder as Wn. E.g. if your student ID is 281234 then take  $281234/7 = 40176.28571 \rightarrow Wn = 0.28571 * 7 = 2 \mu m$ . If you get a Wn below 1 $\mu$ m, then just use 1 $\mu$ m.