# King Fahd University of Petroleum & Minerals Computer Engineering Dept

**COE 202 – Fundamentals of Computer Engineering**

**Term 081**

Dr. Ashraf S. Hasan Mahmoud

Rm 22-148-3

Ext. 1724

Email: ashraf@kfupm.edu.sa

1/2009 Dr. Ashraf S. Hasan Mahmoud

1

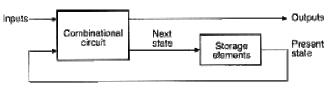

### **Sequential Circuit**

Definition

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

### **Storage Elements**

- Storage can be constructed logic with delay, such as a buffer by connecting the output to the input. The signal must not undergo inversion in the loop or the system will be unstable or astable

- Positive Feedback stability issues and dependence on propagation delay.

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

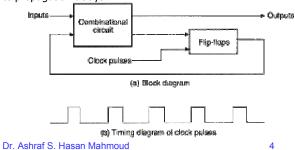

### Synchronous Circuits

- Asynchronous: input changes at any time may result in the any of the outputs or internally stored information (called state) to change.

- Such circuits are difficult to design because of dependence on propagation delays and their interaction with timing of input changes.

- Synchronous: sequential makes use of clock signals so that the storage elements (and outputs) only change at discrete instants of time in relation to the clock signal.

- Clocked synchronous circuits provide some degree of independence on timing variations related to gate propagation delays.

1/11/2009

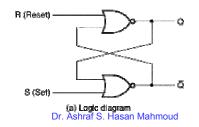

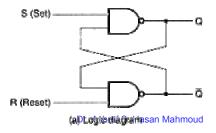

#### **SR Latch**

- Definition: A storage element that maintains binary state indefinitely (as long as power is applied), until directed by an input signal to switch to its other state

- Has two inputs: S and R, and two outputs: Q and Q'

- Notes:

- S=1, R=0  $\rightarrow$  set state (i.e. Q = 1, and Q' = 0)

- S=0, R=1 → reset state (i.e. Q = 0, and Q' = 1)

- S=0, R=0  $\rightarrow$  keep state (i.e. new Q = old Q, new Q' = old Q')

- S=1, R=1 → undefined

| 3 | R                  | Q | ō |             |  |  |  |

|---|--------------------|---|---|-------------|--|--|--|

| 1 | 0                  | 1 | 0 | 0-4-4-4-    |  |  |  |

| 0 | 0                  | 1 | ٥ | Set state   |  |  |  |

| 0 | 1                  | 0 | 1 |             |  |  |  |

| 0 | 0                  | 0 | 1 | Reset state |  |  |  |

| 1 | 1                  | 0 | 0 | Undefined   |  |  |  |

|   | (b) Function table |   |   |             |  |  |  |

1/11/2009

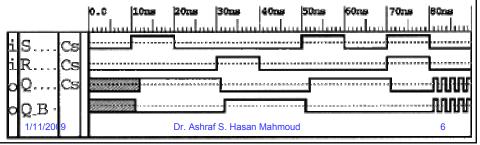

# **SR Latch – Timing Diagram and Stability**

- Note: the outputs are NOW a function of time as well as the inputs

- Stability issue: When SR latch in the undefined state 00 and then both S and R are simultaneously changed to 00 – oscillations appear!!

- S (Set)

- · What is the period of the oscillations?

# **SR Latch – NAND Gates Implementation**

- · Very similar to the NOR gates implementation

- Notes:

1/11/2009

- S=0, R=1  $\rightarrow$  set state (i.e. Q = 1, and Q' = 0)

- S=1, R=0  $\rightarrow$  reset state (i.e. Q = 0, and Q' = 1)

- S=1, R=1  $\rightarrow$  keep state (i.e. new Q = old Q, new Q' = old Q')

- S=0, R=0  $\rightarrow$  undefined

| S                  | R | Q | ā |             |  |  |

|--------------------|---|---|---|-------------|--|--|

| 0                  | 1 | 1 | 0 | Catadata    |  |  |

| 1                  | 1 | 1 | 0 | Sei state   |  |  |

| 1                  | 0 | 0 | 1 |             |  |  |

| 1                  | 1 | 0 | 1 | Resel state |  |  |

| 0                  | 0 | 1 | 1 | Undefined   |  |  |

| (b) Function table |   |   |   |             |  |  |

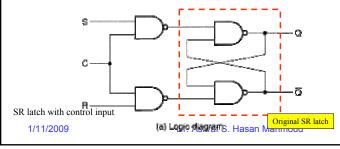

### **SR Latch with Gating**

- The inputs S and R are not always visible to the latch

- Depending on the value of C

- Control signal C

- When enabled (i.e. C = 1):

- You can write a 0 to Q by S=0, R=1

- You can write a 1 to Q by S=1, R=0

- You can keep the state by S=0, R=0

- It is still possible to drive the latch into the undefined state!!

| Ç | Ş | B | Next state of Q    |

|---|---|---|--------------------|

| 0 | х | х | No change          |

| 1 | 0 | ٥ | No change          |

| 1 | 0 | 1 | Q = 0; Reset state |

| 1 | 1 | 0 | Q = 1; Sat state   |

| 1 | 1 | 1 | Undefined          |

(b) Function table 8

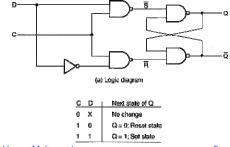

#### **Gated D-Latch**

- With this controlled input D-Latch it is NOT possible to drive it into the invalid state

- Both inputs CAN NOT be active at the same time

- When enabled (i.e. C = 1):

- You can write a 0 to Q by D=0

- You can write a 1 to Q by D=1

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

9

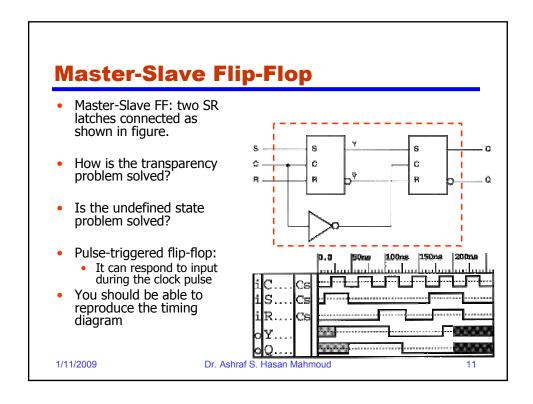

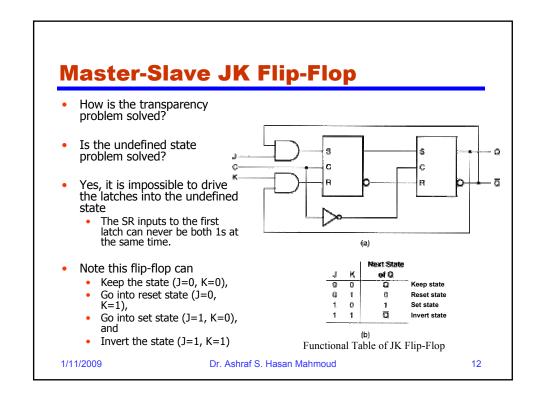

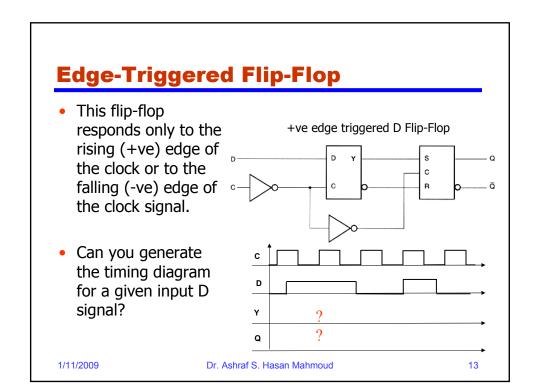

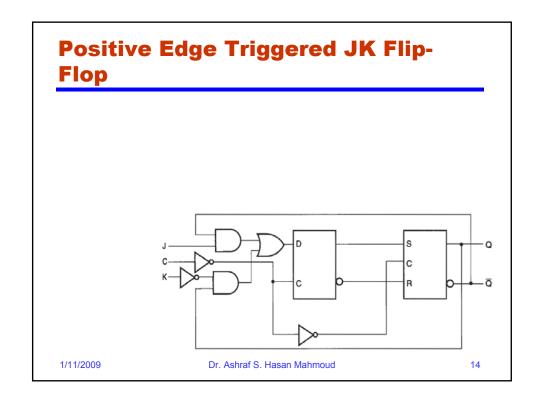

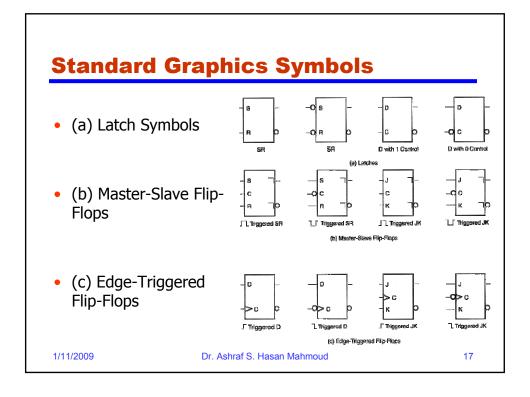

### Flip-Flops

- · Problems with previous latches:

- When C is enabled the latch is in *transparent* mode. i.e. changes in S and R will be reflected in changes to its state so it is still possible to drive the SR latch into the undefined state and then to instability.

- Solutions:

- Master-Slave flip-flop

- Edge-triggered flip-flop

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

### **Timing Issues - Again**

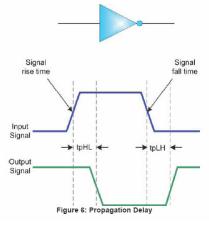

- Propagation Delay: times it takes for an input to appear at the output is called the propagation delay.

- t<sub>PHL</sub>: time it takes for an input to cause the output to change from logic-level-high to logic-level-low.

- t<sub>PLH</sub>: delay associated when an inpu change causes the output to chang from logic-level-low to logic-levelhigh.

- The overall propagation delay is average of t<sub>PHL</sub> and t<sub>PLH</sub>

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

15

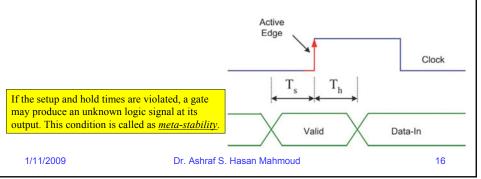

### **Timing Issues - Again**

- Setup Time (Ts): a constant duration for which the inputs must be held prior to the arrival of the clock transition

- Hold Time (Th): refers to the duration for which the inputs must not change after the arrival of the transition

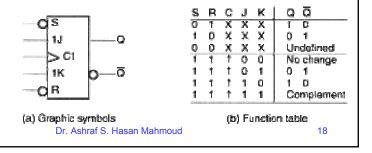

### **Asynchronous Inputs**

- Special inputs for setting or resetting them asynchronously

- Independent of the clock input

- The direct set and direct reset signals are called preset and clear, respectively

- Examining the function table:

- When S=0, R=1, the FF is set regardless of the clock and the JK inputs

- When S=1, R=0, the FF is reset regardless of the clock and the JK inputs

- For the JK to operate normally, S and R should be 1 and 1.

1/11/2009

# Flip-Flop Characteristic Tables

Table 6-7

|                        | (a) <i>JK</i> Flip-Flop |        |            |   |                | (b) SR Flip-Flop |        |            |  |

|------------------------|-------------------------|--------|------------|---|----------------|------------------|--------|------------|--|

| J                      | K                       | Q(t+1) | Operation  | , | S              | R                | Q(t+1) | Operation  |  |

| 0                      | 0                       | Q(t)   | No change  |   | 0              | 0                | Q(t)   | No change  |  |

| 0                      | 1                       | 0      | Reset      |   | 0              | 1                | 0      | Reset      |  |

| 1                      | 0                       | 1      | Set        |   | 1              | 0                | 1      | Set        |  |

| 1                      | 1                       | Q'(t)  | Complement |   | 1              | 1                | ?      | Undefined  |  |

| (c) <i>D</i> Flip-Flop |                         |        |            |   | (d) TFlip-Flop |                  |        |            |  |

| [                      | )                       | Q(t+1) | Operation  |   | -              | Γ                | Q(t+1) | Operation  |  |

| (                      | )                       | 0      | Reset      |   | (              | )                | Q(t)   | No change  |  |

|                        | 1                       | 1      | Set        |   |                | 1                | Q'(t)  | Complement |  |

|                        |                         |        |            |   |                |                  |        |            |  |

1/11/2009 Dr. Ashraf S. Hasan Mahmoud

JK Flip-Flop Characteristic Equation

• Using table on previous slide, one can write:

$$Q(t+1) = J\overline{Q(t)} + \overline{K}Q(t)$$

| J | K | Q(t) | Q(t+1) |

|---|---|------|--------|

| 0 | 0 | 0    | 0      |

| 0 | 0 | 1    | 1      |

| 0 | 1 | 0    | 0      |

| 0 | 1 | 1    | 0      |

| 1 | 0 | 0    | 1      |

| 1 | 0 | 1    | 1      |

| 1 | 1 | 0    | 1      |

| 1 | 1 | 1    | 0      |

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

20

# **SR** Flip-Flop Characteristic Equation

• Using table on slide 19, one can write:

$$Q(t+1) = S + \overline{R}Q(t)$$

| S | R | Q(t) | Q(t+1) |

|---|---|------|--------|

| 0 | 0 | 0    | 0      |

| 0 | 0 | 1    | 1      |

| 0 | 1 | 0    | 0      |

| 0 | 1 | 1    | 0      |

| 1 | 0 | 0    | 1      |

| 1 | 0 | 1    | 1      |

| 1 | 1 | 0    | X      |

| 1 | 1 | 1    | Х      |

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

21

# **D** Flip-Flop Characteristic Equation

• Using table slide 19, one can write:

$$Q(t+1) = D$$

| D | Q(t) | Q(t+1) |

|---|------|--------|

| 0 | 0    | 0      |

| 0 | 1    | 0      |

| 1 | 0    | 1      |

| 1 | 1    | 1      |

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

# **T** Flip-Flop Characteristic Equation

• Using table on slide 19, one can write:

$$Q(t+1) = T \oplus Q(t)$$

| <u>T</u> | Q(t) | Q(t+1) |

|----------|------|--------|

| 0        | 0    | 0      |

| 0        | 1    | 1      |

| 1        | 0    | 1      |

| 1        | 1    | 0      |

1/11/2009

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

23

## **Flip-Flop Excitation Tables**

**Table 6-7**

| (a              | ) <i>JK</i> Flip-F | lop |                | (                     | (b) <i>SR</i> Flip- | Flop |   |

|-----------------|--------------------|-----|----------------|-----------------------|---------------------|------|---|

| Q(t)            | Q(t+1)             | J   | K              | Q(t)                  | Q(t+1)              | S    | R |

| 0               | 0                  | 0   | Χ              | 0                     | 0                   | 0    | Χ |

| 0               | 1                  | 1   | Χ              | 0                     | 1                   | 1    | 0 |

| 1               | 0                  | Χ   | 1              | 1                     | 0                   | 0    | 1 |

| 1               | 1                  | Χ   | 0              | 1                     | 1                   | Χ    | 0 |

| (c) D Flip-Flop |                    |     | (d) TFlip-Flop |                       |                     |      |   |

| Q(t)            | Q(t+1)             | [   | )              | Q(t)                  | Q(t+1)              | 7    | Γ |

| 0               | 0                  | (   | )              | 0                     | 0                   | (    | ) |

| 0               | 1                  | :   | 1              | 0                     | 1                   | 1    | L |

| 1               | 0                  | (   | )              | 1                     | 0                   | 1    | L |

| 1               | 1                  |     | 1              | 1                     | 1                   | (    | ) |

|                 |                    | [   | Or. A          | hraf S. Hasan Mahmoud |                     |      |   |

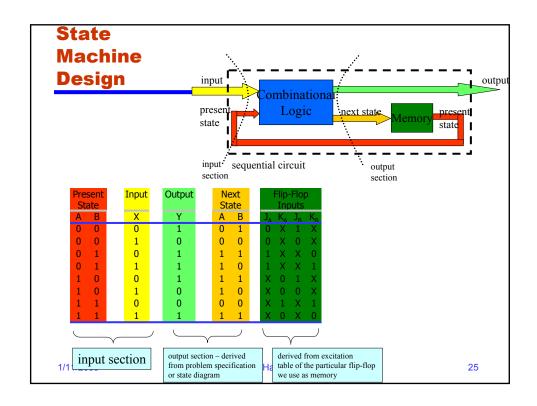

### **Example**

#### • Problem:

- a) Write characteristic equations for each type of flipflops, using the information in Table 6-7. A characteristic equation gives the function Q(t+1) in terms of Q(t) and the input variables to the flip-flop.

- b) Use the characteristic equation for the *JK* flip-flop to find equations A(t+1) and B(t+1) from the flip-flop input equations corresponding to Table shown on next slide.

#### Solution:

a) Refer to previous slides for the development of characteristic equations

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

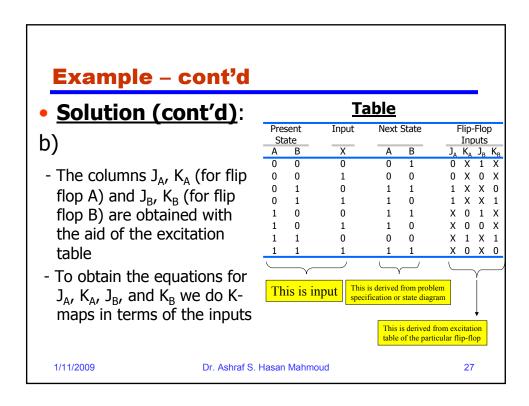

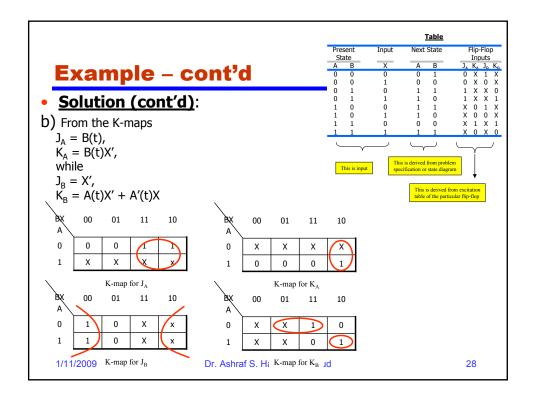

### Example - cont'd

### • Solution (cont'd):

- b) Finally, Using the characteristic equation for the A  ${\it JK}$  flipflop:

- $A(t+1) = J_A A(t)' + K_A' A(t) \rightarrow$

- A(t+1) = B(t)A(t)' + (B(t)X')'A(t)

- = B(t)A(t)' + B(t)'A(t) + XA(t)

- Same for the B JK flip-flop:

- $B(t+1) = J_B B(t)' + K_B' B(t) \rightarrow$

- B(t+1) = X'B(t)' + (A(t)X' + A'(t)X)'B(t)

- B(t+1) = X'B(t)' + A(t)B(t)X + A'(t)B(t)X'

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

29

### **Sequence Recognizer**

- <u>Problem</u>: Design a circuit to recognize the occurrence of the bits 1101 (input from left to right) on an input line X by making an output signal Z equal to 1; Otherwise Z is equal to 0

- Solution:

Sequential circuit with one input X and one output Z

Examples of operation:

1. No sequence – Z remains zero

2. sequence occurs – Z is one

3. Two overlapping sequences – Z is one twice!

Sequence Recognizer

t=4 t=3

t=2 t=1

Sequence Recognizer

t=4 t=3

t=2 t=1

Sequence Recognizer

t=4 t=3

1/11/2009

Sequence

# **Sequence Recognizer – State Diagram**

#### Solution (cont'd):

You always start from an initial state  $\rightarrow$  State  $S_0$

To remember first '1' of sequence  $\rightarrow$  State S<sub>1</sub>

To remember two consecutive 1s of sequence  $\rightarrow$  State S<sub>2</sub>

To remember '110' sequence  $\rightarrow$  State S<sub>3</sub>

**Note** an arrival of  $S_1$  while in state  $S_3$  should make the output Z=1, and move to state B "to remember this '1' which could be the first digit of another 1101 sequence

31

**Sequence Recognizer – State Table** Solution (cont'd): initial state Present **Next State** Output Z State  $X = 0 \mid X = 1$  $X = 0 \mid X = 1$  $S_0$ 0 0  $S_0$  $S_1$  $S_1$  $S_0$  $S_2$ 0 0  $S_3$  $S_2$  $S_2$ 0 0  $S_3$ 0  $S_1$ 1 Dr. Ashraf S. Hasan Mahmoud 32 1/11/2009

# **Sequence Recognizer – State Table**

#### Solution (cont'd):

| Present<br>State | Next  | Next State     |  |       | Output Z |  |  |

|------------------|-------|----------------|--|-------|----------|--|--|

| State            | X = 0 | X = 1          |  | X = 0 | X = 1    |  |  |

| S <sub>0</sub>   | $S_0$ | S <sub>1</sub> |  | 0     | 0        |  |  |

| $S_1$            | $S_0$ | S <sub>2</sub> |  | 0     | 0        |  |  |

| S <sub>2</sub>   | $S_3$ | S <sub>2</sub> |  | 0     | 0        |  |  |

| S <sub>3</sub>   | $S_0$ | $S_1$          |  | 0     | 1        |  |  |

#### State Code Assignment (Grey Coding):

$S_0 \rightarrow 00$

$S_1 \rightarrow 01$   $S_2 \rightarrow 11$

$S_3 \rightarrow 10$

| Present<br>State | Next  | State | Output Z      |

|------------------|-------|-------|---------------|

| State            | X = 0 | X = 1 | X = 0   X = 1 |

| 00               | 00    | 01    | 0 0           |

| 01               | 00    | 11    | 0 0           |

| 11               | 10    | 11    | 0 0           |

| 10               | 00    | 01    | 0 1           |

Dr. Ashraf S. Hasan Mahmoud

33

# **Sequence Recognizer – State Table**

Present State

Input

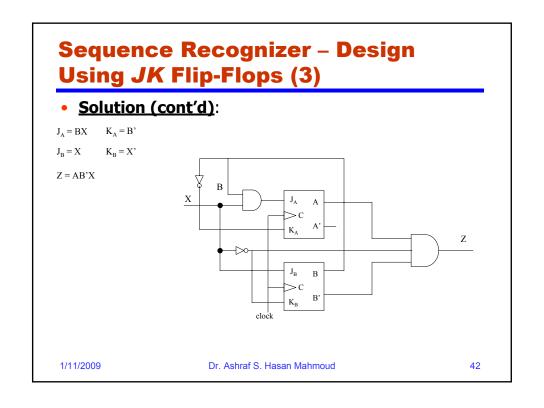

#### Solution (cont'd):

| Present<br>State |     | Next State |       |  | Output Z |       |  |

|------------------|-----|------------|-------|--|----------|-------|--|

| 310              | ite | X = 0      | X = 1 |  | X = 0    | X = 1 |  |

| 0                | )   | 00         | 01    |  | 0        | 0     |  |

| 0                | 1   | 00         | 11    |  | 0        | 0     |  |

| 1                | 1   | 10         | 11    |  | 0        | 0     |  |

| 10               | 0   | 00         | 01    |  | 0        | 1     |  |

1/11/2009

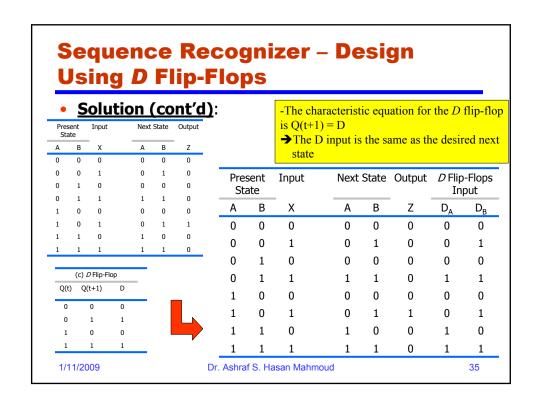

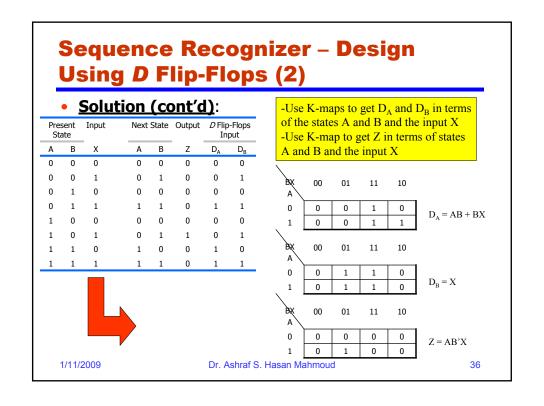

-Another way of writing the state table - Four states → we need two flip-flops A & B (in general if number of states is n, then we require log<sub>2</sub>n flip-flops)

**Next State**

Dr. Ashraf S. Hasan Mahmoud

Output

Ζ

1

0

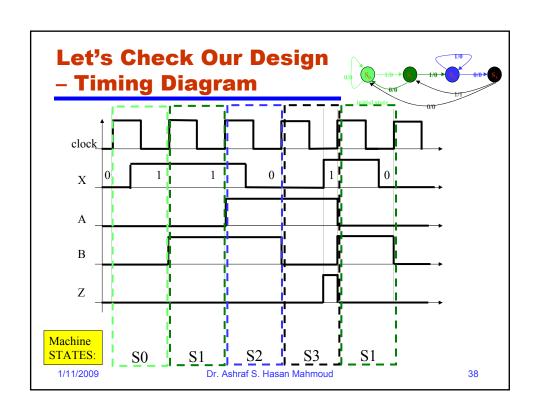

# Let's Check Our Design – Timing Diagram – cont'd

#### Important Notes

- The value of the input prior to the positive edge is the value used to generate the rest of the outputs

- In other words, the input signal is sampled at the positive-edge instant minus epsilon these samples constitute the input signal X

- Positive-edge triggered FFs respond to the input existing prior to the positive edge of the clock – and their output (state) lasts till the next positive edge at least

- The combination logic (AND gate for this example) for producing Z responds to instantaneously to signals at the input of this combination logic – regardless of the clock signal

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

# **Mealy and Moore Type Finite State Machines**

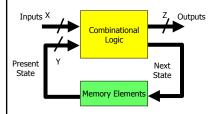

- Mealy Machine:

- In a Mealy machine, the outputs are a function of the present state and the value of the inputs as shown in figure.

- The outputs may change asynchronously in response to any change in the inputs.

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

43

# **Mealy and Moore Type Finite State Machines – cont'd**

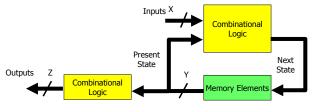

- Moore Machine:

- In a Moore machine the outputs depend only on the present state as shown in figure.

- A combinational logic block maps the inputs and the current state into the necessary flip-flop inputs to store the appropriate next state just like Mealy machine.

- However, the outputs are computed by a combinational logic block whose inputs are only the flip-flops state outputs.

- The outputs change synchronously with the state transition triggered by the active clock edge

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

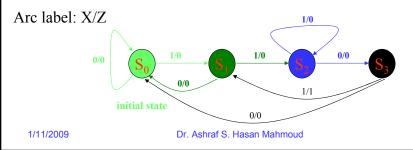

# **Sequence Recognizer – Mealy Machine Example**

- Problem: Design a sequence recognizer (state machine) that outputs '1' if the input is '1' for three consecutive clocks – Use MEALY DESIGN – using D flip-flops

- Solution: State diagram is as shown

State table is as shown

$S_0 \qquad \begin{array}{c} \text{Initial} \\ \text{State} \\ \text{AB} = 00 \end{array} \qquad \begin{array}{c} 0/0 \\ \text{S}_2 \\ \text{O/0} \\ \text{I/0} \qquad \begin{array}{c} \text{Got 11} \\ \text{AB} = 10 \end{array} \\ \\ S_1 \qquad \begin{array}{c} \text{Got 1} \\ \text{AB} = 0 \end{array} \qquad \begin{array}{c} 1/1 \\ \text{AB} = 10 \end{array}$

Arc label: X/Z

1/11/2009

| Present State             |   | Input | Next | Next State |   | D Flip-Flops Input |       |

|---------------------------|---|-------|------|------------|---|--------------------|-------|

| Α                         | В | Х     | Α    | В          | Z | D <sub>A</sub>     | $D_B$ |

| 0                         | 0 | 0     | 0    | 0          | 0 | 0                  | 0     |

| 0                         | 0 | 1     | 0    | 1          | 0 | 0                  | 1     |

| 0                         | 1 | 0     | 0    | 0          | 0 | 0                  | 0     |

| 0                         | 1 | 1     | 1    | 0          | 0 | 1                  | 0     |

| 1                         | 0 | 0     | 0    | 0          | 0 | 0                  | 0     |

| 1                         | 0 | 1     | 1    | 0          | 1 | 1                  | 0     |

| . Ashraf S. Hasan Mahmoud |   |       |      |            |   |                    | 45    |

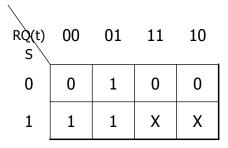

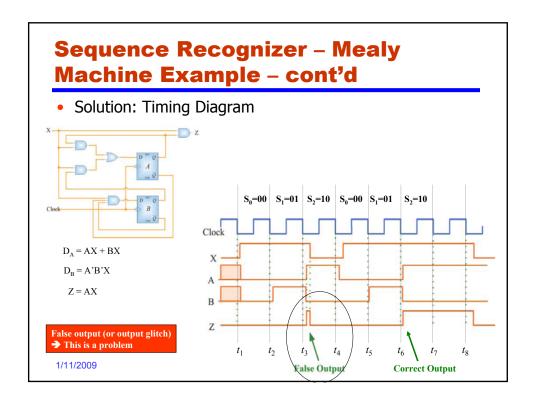

**Sequence Recognizer - Mealy** Machine Example - cont'd Solution: The D flip-flops inputs are: 00 01 11 10 Present State Input Next State Output D Flip-Flops Input Х 0  $D_A = AX + BX$ 0 0 0 0 01 11 10 0 0 0 0 Х х  $D_B = A'B'X$ 01 11 10 0 0 0 0 Notice we chose to use D f/f 0 1 х that respond on -ve clock edge Z = AXB 1/11/2009 46

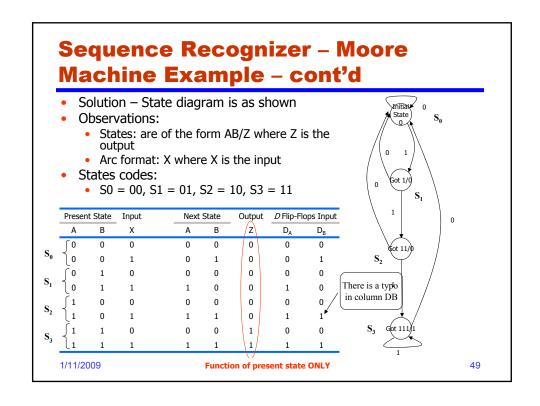

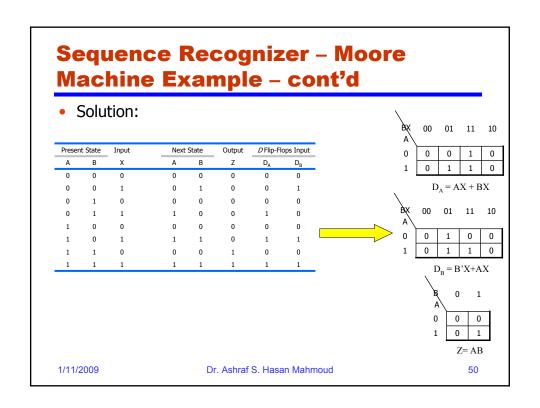

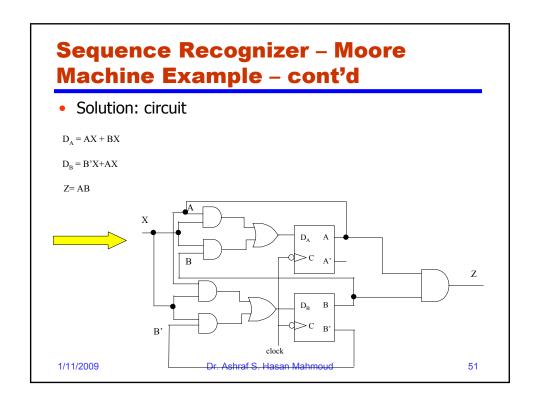

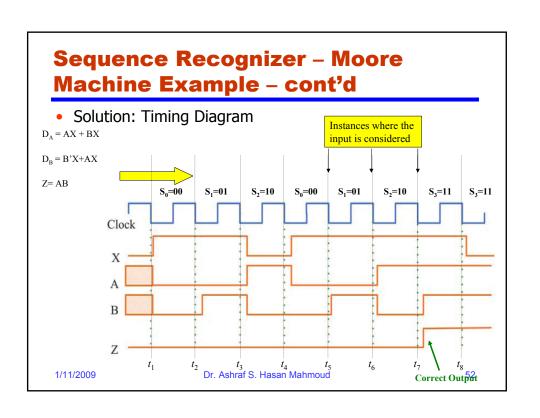

# **Sequence Recognizer – Moore Machine Example**

Problem: Design a sequence recognizer (state machine) that outputs '1' if the input is '1' for three consecutive clocks – Use MOORE DESIGN – using D flip-flops

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

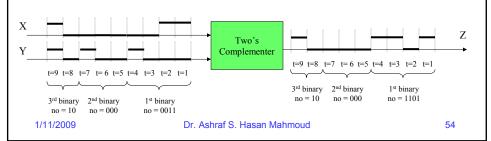

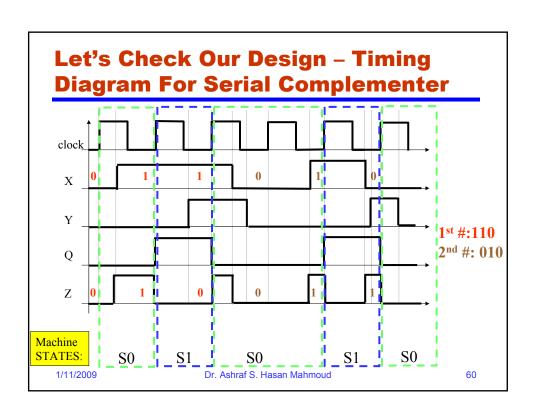

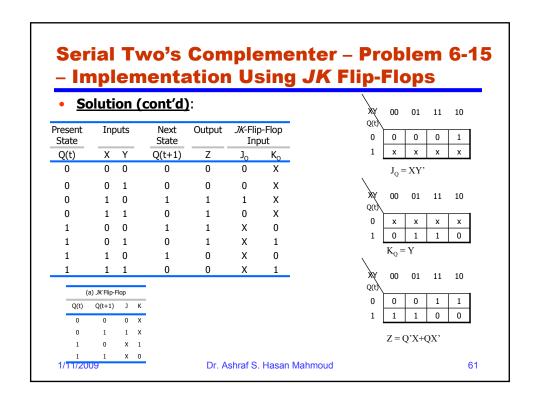

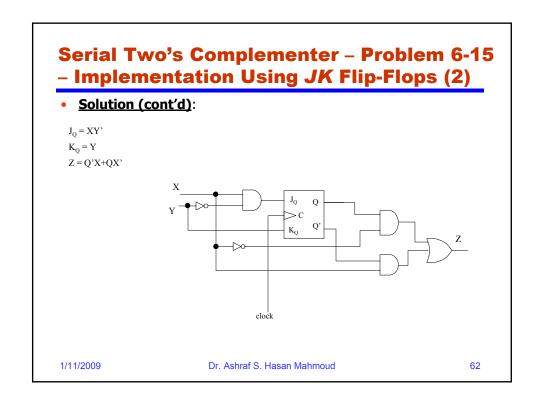

# Serial Two's Complementer – Problem 6-15

- **Problem**: A serial two's complementer is to be designed. A binary integer of arbitrary length is presented to the serial two's complementer least significant bit first on input X. When a given bit is presented on input X, the corresponding output bit is to appear during the same clock cycle on output Z. To indicate that a sequence is complete and that the circuit is to be initialized to receive another sequence, input Y becomes 1 for one clock cycle. Otherwise, Y is 0

- a) Find the state diagram for the serial two's complementer

- b) Find the state table for the serial two's complementer

- c) Design the circuit using D flip-flops

- d) Design the circuit using JK flip-flops

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

53

# **Serial Two's Complementer – Problem 6-15**

#### Solution:

Remember to complement  $A_nA_{n-1}...A_1A_0$ , we scanned the binary digits from LSB to MSB, skipping all zeros and passing the first 1 bit. All subsequent bits are complemented. The result is the two's complement of  $A_nA_{n-1}...A_1A_0$

Example: 2's complement of (10110100) is equal to (01001100)

Example: 2's complement of (0011) is equal to (1101) Example: 2's complement of (000) is equal to (000) Example: 2's complement of (10) is equal to (10)

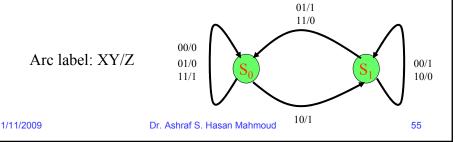

# Serial Two's Complementer – Problem 6-15 – State Diagram

#### Solution (cont'd):

Two inputs X: the binary bits in serial

Y: indicator when number is complete

Scanning the binary number, we switch between two modes:

copying binary digits till first 1 is found

inverting subsequent bits

Hence TWO states are needed – need to remember that we passed the one

Because we have four inputs, each state has FOUR departing arcs

### Serial Two's Complementer – Problem 6-15 – State Diagram (2)

#### Solution (cont'd):

State S<sub>0</sub>: initial state (copying X to Z without inverting bits)

- 1. if zero arrives (input patterns 00 or 01) on X it is copied to Z -

- 2. if one arrives (input patter 11) on X it is also copied to Z if Y is 1 (i.e last bit of number)

- 3. if one arrives and it is not last bit (input pattern 10) then it is copies to Z but circuit moves to the other state to start complementing bits

State  $S_1$ : (copying X to Z while inverting bits) till Y = 1

when Y = 1, another number is about to start – move to initial state  $S_0$

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

### **Serial Two's Complementer -Problem 6-15 – State Table**

#### Solution (cont'd):

2 States → need one flip-flop Let  $S_0 = 0$ , while  $S_1 = 1$

| Present<br>State | Inp | outs | Next<br>State | Output |

|------------------|-----|------|---------------|--------|

| Q(t)             | Х   | Υ    | Q(t+1)        | Z      |

| 0                | 0   | 0    | 0             | 0      |

| 0                | 0   | 1    | 0             | 0      |

| 0                | 1   | 0    | 1             | 1      |

| 0                | 1   | 1    | 0             | 1      |

| 1                | 0   | 0    | 1             | 1      |

| 1                | 0   | 1    | 0             | 1      |

| 1                | 1   | 0    | 1             | 0      |

| 1                | 1   | 1    | 0             | 0      |

|                  |     |      |               |        |

Dr. Ashraf S. Hasan Mahmoud

57

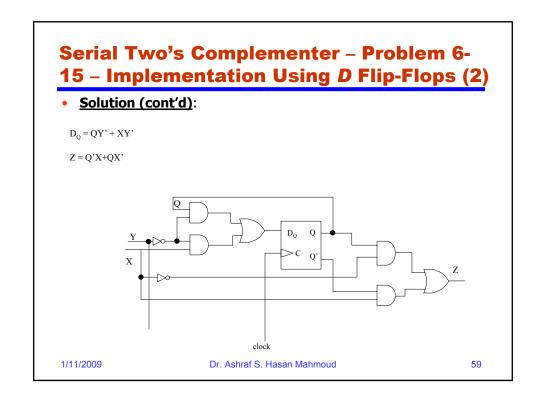

#### **Serial Two's Complementer - Problem 6-**15 - Implementation Using D Flip-Flops

#### Solution (cont'd):

| Present<br>State | Inp      | uts | Next<br>State | Output | <i>D</i> -Flip-Flop<br>Input |

|------------------|----------|-----|---------------|--------|------------------------------|

| Q(t)             | Х        | Υ   | Q(t+1)        | Z      | D <sub>o</sub>               |

| 0                | 0        | 0   | 0             | 0      | 0                            |

| 0                | 0        | 1   | 0             | 0      | 0                            |

| 0                | 1        | 0   | 1             | 1      | 1                            |

| 0                | 1        | 1   | 0             | 1      | 0                            |

| 1                | 0        | 0   | 1             | 1      | 1                            |

| 1                | 0        | 1   | 0             | 1      | 0                            |

| 1                | 1        | 0   | 1             | 0      | 1                            |

| 1                | 1        | 1   | 0             | 0      | 0                            |

| (c) DE           | lin-Elon |     | •             |        |                              |

| XY<br>Q(t)        | 00 | 01 | 11 | 10 |  |  |  |

|-------------------|----|----|----|----|--|--|--|

| 0                 | 0  | 0  | 0  | 1  |  |  |  |

| 1                 | 1  | 0  | 0  | 1  |  |  |  |

| $D_Q = QY' + XY'$ |    |    |    |    |  |  |  |

01 11 10 0

Z = Q'X+QX'

Q(t) Q(t+1) D 1

Dr. Ashraf S. Hasan Mahmoud

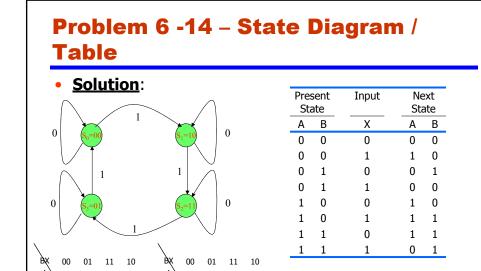

### **More Examples: Problem 6-14**

<u>Problem</u>: Design a sequential circuit with two D flipflops A and B and one input X. When X = 0, the state of the circuit remains the same. When X = 1, the circuit goes through the state transitions 00 to 10 to 11 to 01, and back to 00, and then repeats.

1/11/2009

0

0 0

0

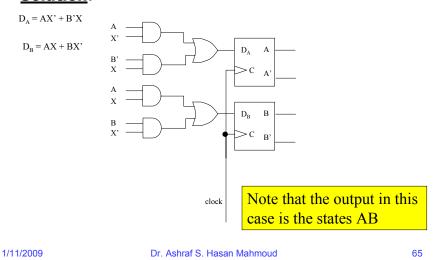

$D_A = AX' + B'X$

1/11/2009

0 0 0 0

0

$D_B = AX + BX$

Dr. Ashraf S. Hasan Mahmoud

Dr. Ashraf S. Hasan Mahmoud

63

64

Note that the output in this

case is the states AB

# **Problem 6-14 – Circuit Implementation**

#### Solution:

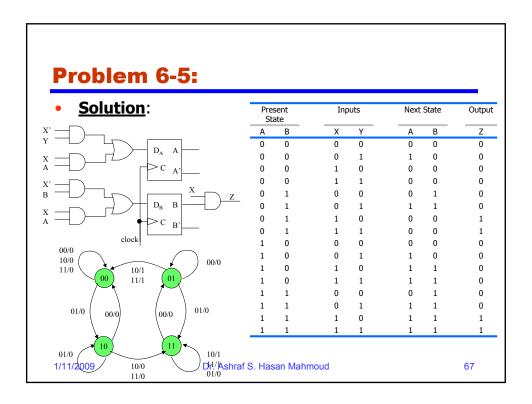

# **Another Example: Problem 6-5**

Problem: A sequential circuit with two D flip-flops A and B, two inputs X and Y, and one output Z is specified by the following input equations:

$$D_A = X'Y + XA$$

;  $D_B = X'B + XA$ ;  $Z = XB$

- a) Draw the logic diagram of the circuit

- b) Derive the state table

- c) Derive the state diagram

This is NOT a design problem – should be much easier than the ones presented earlier!

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

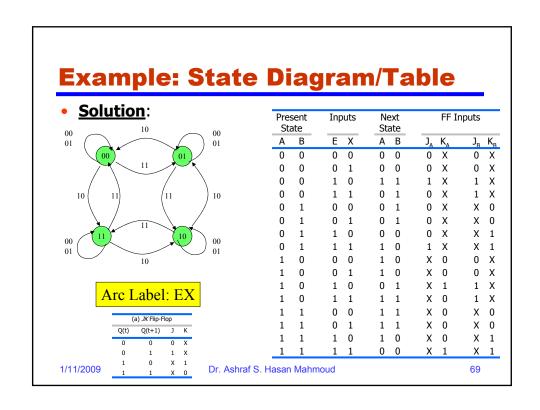

# Yet Another Example: Up/Down Counter with Enable

• <u>Problem</u>: Design a sequential circuit with two *JK* flipflops A and B and two inputs X and E. If E = 0, the circuit remains in the same state, regardless of the input X. When E = 1 and X = 1, the circuit goes through the state transitions from 00 to 01 to 10 to 11, back to 00, and then repeats. When E = 1 and X = 0, the circuit goes through the state transitions from 00 to 11 to 10 to 01, back to 00 and then repeats.

1/11/2009

Dr. Ashraf S. Hasan Mahmoud

# **Recommended Set of Problems**

Problems Of INTEREST:

Problems with "s" are solved in this slides package

1/11/2009

Dr. Ashraf S. Hasan Mahmoud