## COE 405, Term 122

### **Design & Modeling of Digital Systems**

# HW# 5 Solution

#### Due date: Monday, April 15

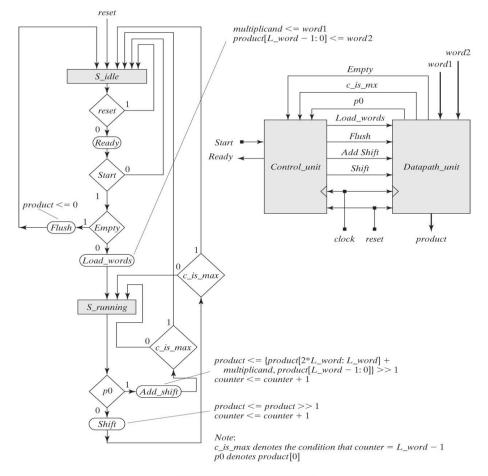

**Q.1.** It is required to design an unsigned 4-bit sequential multiplier. The multiplier is assumed to have an 8-bit register to hold the result, a 4-bit register to hold the multiplicand and a 3-bit counter. When reset is 1, the multiplicand, the product and counter registers are reset. When operation is started, the multiplicand register is loaded with word1 while the least significant 4-bits of the product are loaded with word2. The block diagram and the ASMD chart of the sequential multiplier are given below. *Ready* signals that the unit is ready to accept a command to multiply. If word1 or word2 are 0, *Empty* is set to 1. *Flush* loads the product with 0. *C\_is\_mx* is set when the counter is equal to 3. *P0* is the least significant bit of the product i.e. product[0].

Copyright © 2011 Pearson Education, Inc. publishing as Prentice Hall

(i) Write a Verilog model to model the data-path.

```

module Multiplier DPU #(parameter word size=4)(

output [2*word_size-1: 0] product,

output Empty, c_is_mx, p0,

input [word_size-1:0] word1, word2,

input Load_words, Flush, Add_shift, Shift, Ready, clock, reset

);

reg [word_size-1:0] multiplicand;

reg [2*word_size:0] tproduct;

reg [1:0] counter;

assign product = tproduct[2*word_size-1:0];

assign p0 = tproduct[0];

assign w1z = \sim |word1;

assign w2z = \sim |word2;

assign Empty = w1z \mid w2z;

assign c is mx = \& counter;

always @ (posedge clock)

if (reset == 1'b1) counter \leq 0;

else if (Shift || Add_shift) counter <= counter + 1;

always @ (posedge clock)

if (reset || Flush) tproduct \leq 0;

else if (Load words) begin

tproduct[word size-1:0] <= word2;

end

else if (Shift) tproduct <= tproduct >> 1;

else if (Add_shift)

tproduct <= {tproduct[2*word_size:word_size]+{1'b0,multiplicand}, product[word_size-1:0]}

>>1;

always @ (posedge clock)

if (Load_words) multiplicand <= word1;

```

```

endmodule

```

(ii) Write a Verilog model to model the control unit based on the ASMD chart i.e. not based on equations.

module Multiplier\_CU (output reg Load\_words, Flush, Add\_shift, Shift, Ready, input Start, p0, c\_is\_mx, Empty, clock, reset);

parameter S\_idle = 1'b0, S\_running=1'b1;

```

reg state, next_state;

always @(posedge clock)

if (reset) state <= S_idle;

else state <= next_state;

always @(state, Start, p0, c_is_mx, Empty) begin

Load_words=0; Flush=0; Add_shift=0; Shift=0; Ready=0;

case (state)

S_idle: begin

Ready=1;

if (Start) begin

if (Empty) begin

next_state=S_idle; Flush=1; end

else begin

next_state=S_running; Load_words=1; end

end

else next_state=S_idle;

end

S_running:

if (p0) begin

Add shift=1;

if (c_is_mx) next_state=S_idle;

else next_state=S_running;

end

else begin

Shift=1;

if (c_is_mx) next_state=S_idle;

else next_state=S_running;

end

endcase

end

endmodule

```

(iii) Write a Verilog test bench to test the correctness of a 4-bit sequential multiplier.

```

module Multiplier #(parameter word_size=4)(

output [2*word_size-1: 0] product,

output Ready,

input [word_size-1:0] word1, word2,

input Start, clock, reset

);

```

Multiplier\_CU M1 (Load\_words,Flush, Add\_shift, Shift, Ready, Start, p0, c\_is\_mx, Empty, clock, reset);

Multiplier\_DPU M2 ( product, Empty, c\_is\_mx, p0, word1, word2, Load\_words, Flush, Add\_shift, Shift, Ready, clock, reset);

endmodule

module t\_Multiplier ();

wire [7: 0] product; wire Ready; reg [3:0] word1, word2; reg Start, clock, reset;

Multiplier M1 (product, Ready, word1, word2, Start, clock, reset); initial #220 \$finish; initial begin clock = 0; forever #5 clock =  $\sim$ clock; end initial fork #10 word1 = 'd5;#10 word 2 = 'd8;#10 reset = 0; // Power-up reset #20 reset = 1;#40 reset = 0;#50 Start = 1; #60 Start = 0; #130 reset = 1; #140 reset = 0;#150 word1 = 'd8; #150 word 2 = 'd10;#150 Start = 1; #160 Start = 0; join endmodule

|                         | x      | -0  | )8 | (4) | (1) (40                                                                                                         |  | χ0 | (10       | ),5 ),66 | (33 )(80 |     |  |

|-------------------------|--------|-----|----|-----|-----------------------------------------------------------------------------------------------------------------|--|----|-----------|----------|----------|-----|--|

| 🕘 /t_Multiplier/Ready   | SK     |     |    |     |                                                                                                                 |  |    |           |          |          |     |  |

| ⊞–🌖 /t_Multiplier/word1 | X      | 5   |    |     |                                                                                                                 |  |    | )8        |          |          |     |  |

| ⊕- /t_Multiplier/word2  | X      | 8   |    |     |                                                                                                                 |  |    | (10       |          |          |     |  |

| 🌖 /t_Multiplier/Start   | X      |     |    |     |                                                                                                                 |  |    |           |          |          |     |  |

| 🌖 /t_Multiplier/clock   | 1      |     |    |     |                                                                                                                 |  |    |           |          |          |     |  |

| 🌖 /t_Multiplier/reset   | X      |     |    |     |                                                                                                                 |  |    |           |          |          |     |  |

|                         |        |     |    |     |                                                                                                                 |  |    |           |          |          |     |  |

| Now                     | 220 ns | - 1 |    |     | 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 - 100 |  |    | 150 IIIII |          | 20       | 200 |  |

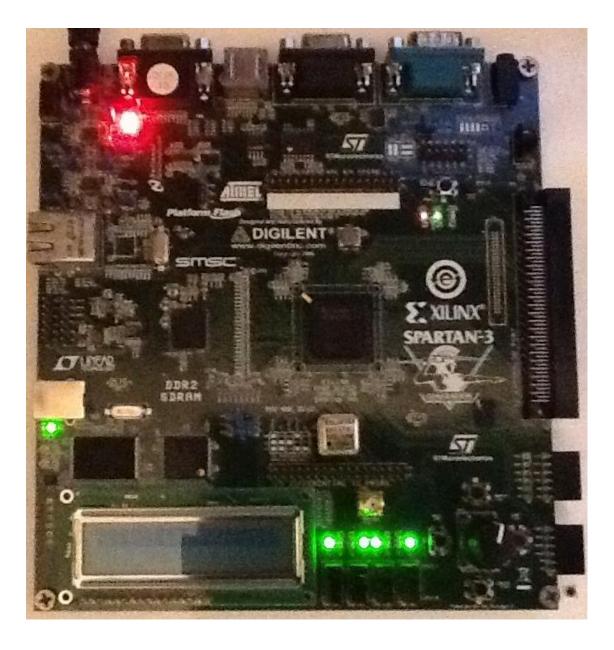

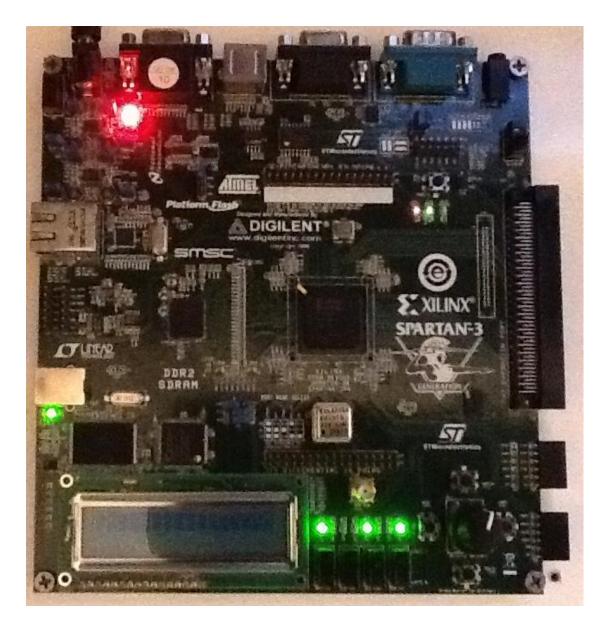

(iv) Implement the 4-bit sequential multiplier using FPGA and demonstrate its correctness.

# Input = 3 Output=9

# Input = 5 Output=25