## **COE 405, Term 131**

## **Design & Modeling of Digital Systems**

## HW#4

Due date: Thursday, Nov. 21

Q.1. Various algorithms have been developed to improve the performance of sequential multipliers and to simplify their circuitry. Booth's recoding algorithm is widely used because it has a simple hardware realization, requires less silicon area and can speed sequential multiplication significantly. Multipliers that use Booth's algorithm recode the bits of the multiplier to reduce the number of additions required to complete the cycle of multiplication. Only the multiplier is recoded; the multiplicand is left unchanged. Booth algorithm is applicable to positive numbers and to negative numbers in 2's complement representation. The key to Booth's algorithm is that it skips over strings of 1's in the multiplier and replaces a series of additions by one addition and one subtraction. For example, the word 1111\_0000 is equivalent to 2<sup>8</sup>-1-(2<sup>4</sup>-1)=2<sup>8</sup> - 2<sup>4</sup> = 256-16=240. The table below summarizes the recoding rules.

| $m_i$ | $m_{i-1}$ | $\mathbf{BRC}_i$ | Value | Status              |

|-------|-----------|------------------|-------|---------------------|

| 0     | 0         | 0                | 0     | String of 0s        |

| 0     | 1         | 1                | +1    | End of string of 1s |

| 1     | 0         | 1                | -1    | Begin string of 1s  |

| 1     | 1         | 0                | 0     | Midstring of 1s     |

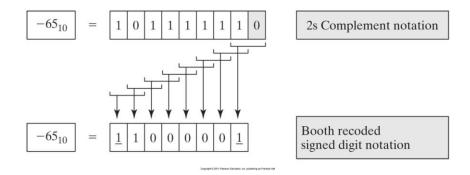

The algorithm reads from the LSB to the MSB and the value of two successive bits ( $m_i$ ,  $m_{i-1}$ ) determines the Booth recoded multiplier bit, BRC<sub>i</sub>. As the algorithm reads two successive bits, the present and the immediate past, it forms and uses BRC<sub>i</sub> to determine whether to add or subtract before skipping to the next bit. The first step of the algorithm is seeded with a value of 0 to the right of the LSB of the word. If the signed digit  $\underline{\mathbf{1}}$  is encountered, a subtraction operation is performed (i.e. an appropriately shifted copy of the 2's complement of the multiplicand is added to the product). The process encodes the first encountered 1 as a  $\underline{\mathbf{1}}$ , skips over any successive 1's until a 0 is encountered. That 0 is encoded as  $\underline{\mathbf{1}}$  to signify the end of a string of 1's, and then the process continues. As an example of Booth recoding, the encoding of -65=1011\_1111 is shown below.

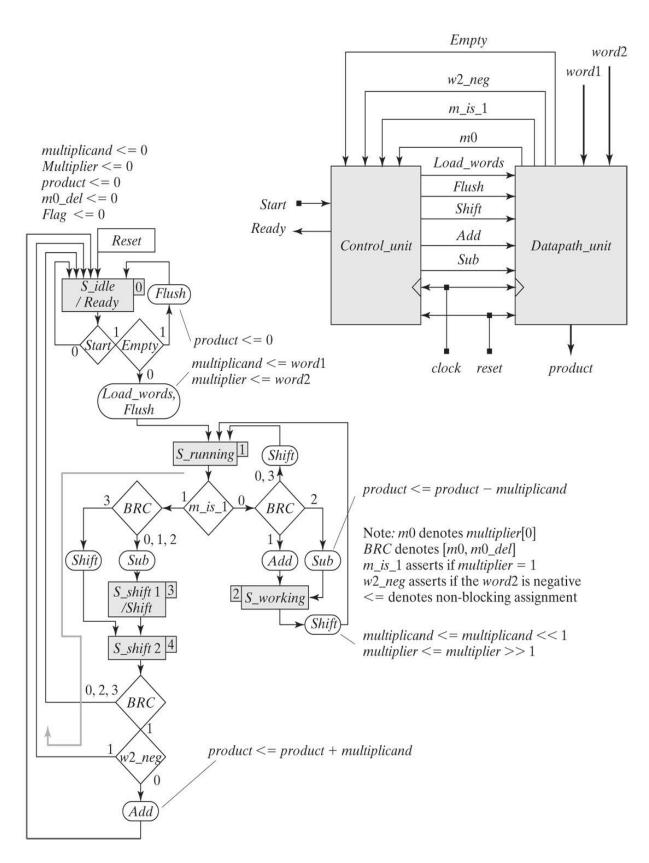

A block diagram and an ASMD chart for the booth multiplier are given below. The machine is efficient as it does not waste time doing needless operations, such as multiplying by 0 or multiplying after the last 1 in the multiplier has been found. When word1 or word2 are 0, Empty signal is asserted. When the value of the multiplier register is 1, the machine's action depends on whether this last bit of 1 is possibly due to word2 having been the 2's complement code corresponding to a negative number (i.e., the MSB of word2 was 1). Moreover, when m\_is\_1 is asserted, there are only two possible values of BRC: 2 and 3. In the former case, the usual subtraction must be performed. Sub is asserted and the state moves from S\_running to S\_shift1, where BRC is now 1. If word2 was negative, no further action is required; otherwise, a final addition must be executed. Shift is asserted in S\_Shift1 to align the multiplicand for the final addition, then the state moves to S\_Shift2, where Add is asserted. The latter case must be handled differently, because the condition that BRC is 3 in S\_running with m\_is\_1 asserted could be due to an intermediate string of 1's or to a terminating string of 1's in word2. A terminating string of 1's corresponds to a negative 2's complement multiplier and dictates that Add not be asserted in S\_shift2. There is no way to distinguish between these two cases without setting a flag in the datapath to indicate that word2 is negative and passing the result as a status signal to the controller. The machine uses a flag register in the datapath to form an additional status signal, w2\_neg, to indicate that the data pattern of word2 has a negative value.

Copyright © 2011 Pearson Education, Inc. publishing as Prentice Hall

(i) Show the design of the data-path and control unit of a 4-bit sequential Booth multiplier. module BMultiplier #(parameter word size=4)( output [2\*word\_size-1: 0] product, output Ready, input [word\_size-1:0] word1, word2, input Start, clock, reset); BMultiplier CU M1 (Load words, Flush, Shift, Add, Sub, Ready, Start, m0, m0 del, m\_is\_1, w2\_neg, Empty, clock, reset); BMultiplier\_DPU #(word\_size) M2 (product, Empty, w2\_neg, m\_is\_1, m0, m0\_del,word1, word2, Load\_words, Flush, Shift, Add, Sub, clock, reset); endmodule module BMultiplier\_DPU #(parameter word\_size=4)( output reg [2\*word\_size-1: 0] product, output Empty, w2\_neg, m\_is\_1, m0, output reg m0\_del, input [word size-1:0] word1, word2, input Load\_words, Flush, Shift, Add, Sub, clock, reset); reg [2\*word\_size-1:0] multiplicand; reg [word\_size-1:0] multiplier; reg Flag; assign m0 = multiplier[0]; assign  $w1z = \sim |word1;$ assign  $w2z = \sim |word2;$ assign Empty =  $w1z \mid w2z$ ; assign m\_is\_1 = (~|multiplier[word\_size-1:1])&multiplier[0]; assign  $w2_{neg} = Flag$ ; always @ (posedge clock, posedge reset) if (reset) Flag  $\leq 0$ ; else if (Load\_words) Flag <= word2[word\_size-1]; always @ (posedge clock, posedge reset) if (reset)  $m0_{del} \le 0$ ; else m0\_del <= multiplier[0]; always @ (posedge clock, posedge reset)

if (reset) product  $\leq 0$ ;

```

else if (Flush) product <= 0;

else if (Add)

product <= product + multiplicand;</pre>

else if (Sub)

product <= product - multiplicand;</pre>

always @ (posedge clock, posedge reset)

if (reset) multiplicand <= 0;

else if (Load_words) multiplicand <= {{word_size{word1[word_size-1]}},word1};

else if (Shift) multiplicand <= multiplicand << 1;

always @ (posedge clock, posedge reset)

if (reset) multiplier <= 0;

else if (Load_words) multiplier <= word2;

else if (Shift) multiplier <= multiplier >> 1;

endmodule

module BMultiplier CU (output reg Load words,

Flush, Shift, Add, Sub, Ready,

input Start, m0, m0 del, m is 1, w2 neg, Empty, clock, reset);

wire [1:0] BRC;

assign BRC = \{m0, m0\_del\};

parameter S_idle = 3'b000, S_running=3'b001, S_working=3'b010,

S_shift1=3'b011, S_shift2=3'b100;

reg [2:0] state, next_state;

always @(posedge clock, posedge reset)

if (reset) state <= S_idle;

else state <= next_state;

always @(state, Start, BRC, m_is_1, Empty, w2_neg) begin

next_state=S_idle;

Load words=0; Flush=0; Add=0; Sub=0; Shift=0; Ready=0;

case (state)

S idle: begin

Ready=1;

if (Start) begin

if (Empty) begin

next_state=S_idle; Flush=1; end

else begin

next state=S running; Load words=1; Flush=1; end

end

```

```

else next_state=S_idle;

end

S running:

if (m_is_1)

case (BRC)

0,1,2: begin Sub=1;next_state=S_shift1; end

3: begin Shift=1; next_state=S_shift2; end

endcase

else

case (BRC)

0,3: begin Shift=1; next_state=S_running; end

1: begin Add=1;

next_state=S_working; end

2: begin Sub=1;

next_state=S_working; end

endcase

S_working: begin Shift=1; next_state=S_running; end

S_shift1: begin Shift=1; next_state=S_shift2; end

S shift2:

case (BRC)

0,2,3: next state=S idle;

1: if (w2_neg) next_state=S_idle;

else begin Add=1; next_state=S_idle; end

endcase

endcase

end

endmodule

```

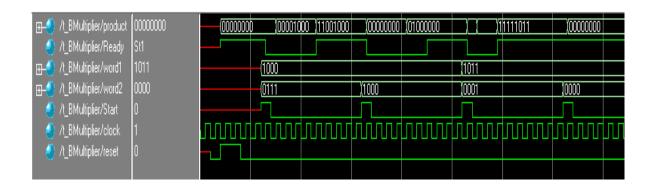

- (ii) Model the circuit in Verilog and verify its correct functionality by simulation for the following values:

- Multiplicand=-8, multiplier=7

- Multiplicand=-8, multiplier=-8

- Multiplicand=-5, multiplier=1

- Multiplicand=-5, multiplier=0

```

module t_BMultiplier ();

wire [7: 0] product;

wire Ready;

reg [3:0] word1, word2;

reg Start, clock, reset;

BMultiplier M1 (product, Ready, word1, word2, Start, clock, reset);

initial #450 $finish;

initial begin clock = 0; forever #5 clock = ~clock; end

initial fork

#10 reset = 0; // Power-up reset

#20 reset = 1;

```

```

#40 \text{ reset} = 0;

#60 \text{ word}1 = b1000;

#60 \text{ word2} = b0111;

#60 Start = 1;

#70 Start = 0;

#160 \text{ word1} = b1000;

#160 \text{ word2} = b1000;

#160 Start = 1;

#170 Start = 0;

#260 \text{ word1} = b1011;

#260 word2 = 'b0001;

#260 Start = 1;

#270 Start = 0;

#360 \text{ word1} = b1011;

#360 \text{ word2} = b0000;

#360 Start = 1;

#370 Start = 0;

join

endmodule

```

- (iii) Implement the circuit using Xilinx FPGA board and verify its correct functionality for the following values: (1% Bonus)

- Multiplicand=-8, multiplier=7

- Multiplicand=-8, multiplier=-8

- Multiplicand=-5, multiplier=1

- Multiplicand=-5, multiplier=0