#### **COE 405, Term 122**

### **Design & Modeling of Digital Systems**

#### HW#2 Solution

Due date: Monday, March 4

Q.1. It is required to design a sequential circuit that has a single input X and a single output Y. The circuit receives an unsigned number serially through the input X from the least significant bit (LSB) to the most significant bit (MSB), and computes the equation 3\*X+1 and generates the output serially from the least significant bit to the most significant bit. The circuit has an additional reset input R which resets the circuit into an initial state. The following are examples of input and output data:

| Exan | <u>iples:</u> |   | LSB |   |   |   | MSB |                      |

|------|---------------|---|-----|---|---|---|-----|----------------------|

|      | Input         | X | 0   | 1 | 1 | 0 | 0   | Input=6<br>Output=19 |

|      | Output        | Y | 1   | 1 | 0 | 0 | 1   | Output=19            |

|      |               |   | LSB |   |   |   | MSB |                      |

|      | Input         | X | 1   | 1 | 0 | 0 | 0   | Input=3<br>Output=10 |

|      | Output        | Y | 0   | 1 | 0 | 1 | 0   | Output=10            |

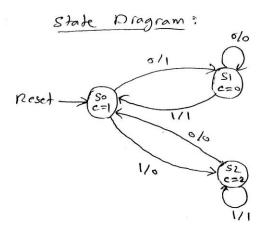

(i) Draw the state diagram of the circuit assuming a **Mealy** model.

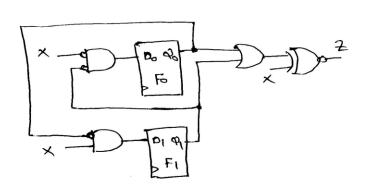

(ii) Implement the circuit using D-FFs.

# errouit Implementation:

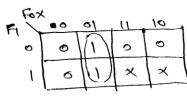

Since we have 3 states, we need 2 flip-flops. Let us use the following 8 state assignment: So = 00, S1=01, S2=10.

|       |   | •  |    |   |

|-------|---|----|----|---|

| Fi Fo | K | Fi | Fo | Z |

| 20    | 0 | •  | ١  | 1 |

| 00    |   | 1  | ٥  | 0 |

| 0     |   | 0  | 1  | 0 |

| 0 1   | 1 | 0  | 0  | 1 |

| 0 1   | 0 | 0  | 0  | 0 |

| 10    | 1 | 1  | 0  | 1 |

| -     | 0 | X  | メ  | × |

|       | 1 | X  | 又  |   |

|       |   |    |    |   |

| Fo | X  |      |    |           |

|----|----|------|----|-----------|

| FI | 00 | 01.  | 11 | 10        |

| 6  | D  | 0    | ပ  | (1)       |

| ł  | 0  | 0    | ×  | $\times$  |

|    | D  | Do = | FI | $\hat{x}$ |

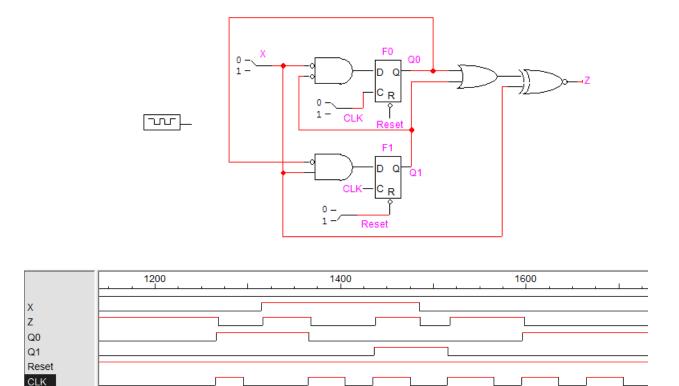

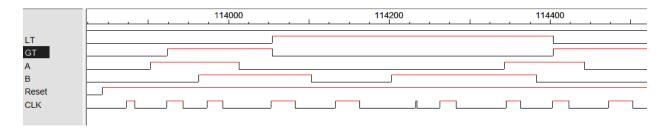

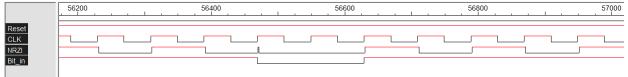

(iii) Verify the correctness of your circuit by simulation.

It can be seen that the circuit is working correctly. The input X=0110=6 is applied and the output Z=10011=19 is produced.

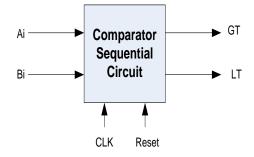

Q.2. It is required to design a sequential circuit that compares two n-bit numbers A=A<sub>n-1</sub>A<sub>2</sub>A<sub>1</sub>A<sub>0</sub> and B=B<sub>n-1</sub>B<sub>2</sub>B<sub>1</sub>B<sub>0</sub>, applied to the sequential circuit serially from the least significant bits to the most significant bits. The circuit produces two outputs GT and LT. If A>B, then the output signal GT is set to 1 and LT is set to 0. If A<B, then the output signal LT is set to 1, and GT is set to 0. Otherwise, both signals will be set to 0, which indicates that the two numbers are equal (i.e. A=B). Assume the existence of a reset input to reset the machine to a reset state. The following is an example of the input and output streams:

|         |    | LSB    | MSB |

|---------|----|--------|-----|

| Input A |    | 010010 | 010 |

| 1       | В  | 000110 | 010 |

| Output  | GT | 001100 | 000 |

| 2 P     | LT | 00001  | 111 |

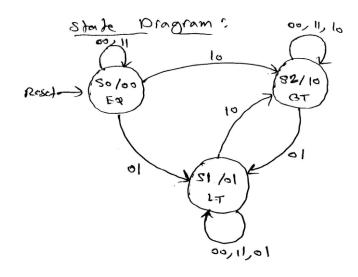

### (i) Draw the state diagram of the circuit assuming a **Moore** model.

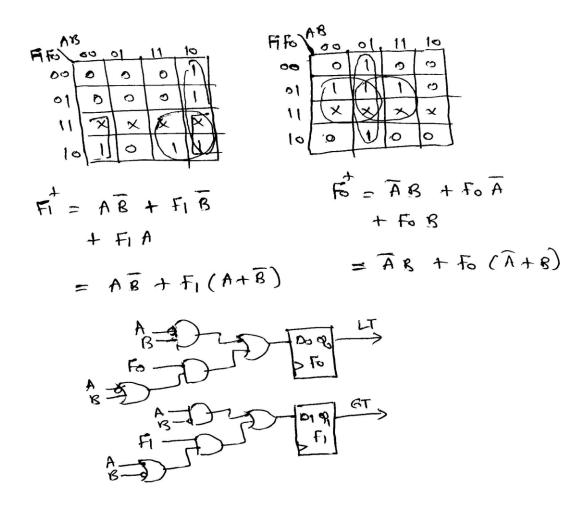

### (ii) Implement the circuit using D-FFs.

# Circuit Implementation:

Since we have 3 states, we need two flip flops, FI and For we use the state assignment to be the same as the output for each state

(1c. So =00, SI =01, S2=10

| Fi     | Fo           | A   | B             | FIF | Fo | GT LT    |   |

|--------|--------------|-----|---------------|-----|----|----------|---|

| -      | 0            | 0   | 0             | 0   | 0  | 0 0      |   |

| 0      | 0            | 0   | 1             | 0   | 1  | o o      |   |

| 0      | 0            | 1   | 0             | l   | 0  | 0 0      |   |

| 0      | 0            | l   | 1             | 5   | 0  | 0 0      |   |

| 0      | 1            | 0   | 0             | 0   | 1  | 0 1      |   |

| 0      | Ť            | 0   | 1             | 0   | ١  | 0 1      | _ |

| 0      | 1            | 1   | 0             | 1   | 0  | 0 1      |   |

| 0      | 1            | - ( | 1             | 0   | 1  | 0 1      |   |

| 1      | 0            | 0   | 0             | 1   | 0  | 1 0      |   |

| 1      | 0            | 0   | 1             | 0   | 1  | 10       |   |

| 1      | 0            | (   | 0             | 1   | 0  | 10       |   |

|        | O            |     | $\overline{}$ | ì   | 0  | 10       |   |

| -      | T            | 0   | 8             | . * | ×  | <u> </u> |   |

| -\\\\\ | <del>-</del> | 9   | 1             | 乂   | 久  | x x      |   |

| -      | 1            | 1   | စ             | ×   | ×  | x x      |   |

| -      | 1            |     | 1             | X   | ×  | х х      |   |

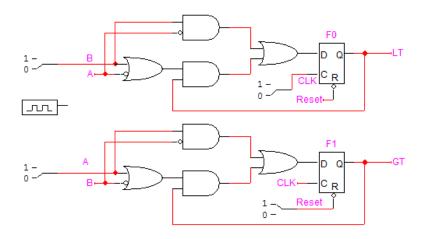

(iii) Verify the correctness of your circuit by simulation.

Simulation results verify the correct operation of the circuit.

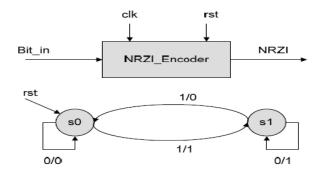

- Q.3. It is required to design a sequential circuit that implements a NRZI line encoder.

- (i) Draw the state diagram of the circuit assuming a **Mealy** model.

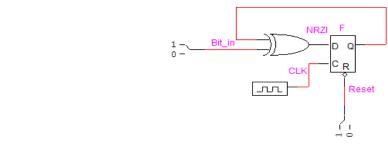

(ii) Implement the circuit using D-FFs.

Since we have two states, we need one flip flop, F. we use the state assignment 80=0, \$1=1

| F | BILLIN | £+ | NRZI |

|---|--------|----|------|

| 0 | 0      | 0  | 0    |

|   | 1      | 1  | -1   |

| 1 | 0      | t  | 1    |

| 1 | (      | 0  | 0    |

(iii) Verify the correctness of your circuit by simulation.

Simulation results verify the correct operation of the circuit.

**Q.4.** Consider the given FSM that has 5 states, one input (X) and one output (Z), represented by the following state table:

| <b>Present State</b> | Next State, Z |       |  |

|----------------------|---------------|-------|--|

|                      | X=0           | X=1   |  |

| S0                   | S2, 1         | S4, 0 |  |

| S1                   | S2, 0         | S4, 1 |  |

| S2                   | S1, 0         | S0, 1 |  |

| S3                   | S3, 0         | S4, 1 |  |

| S4                   | S3, 1         | S0, 0 |  |

(i) Determine the equivalent states.

**Implication Chart**:

| <b>S</b> 1 | X        |          | _                   |            |

|------------|----------|----------|---------------------|------------|

| S2         | X        | (S0,S4)  |                     | _          |

| <b>S</b> 3 | X        | (S2, S3) | (S1,S3),            |            |

|            |          |          | (S1,S3),<br>(S0,S4) |            |

| S4         | (S2, S3) | X        | X                   | X          |

|            | S0       | S1       | S2                  | <b>S</b> 3 |

Thus, equivalent states are: (S1, S2, S3), (S0, S4)

(ii) Reduce the state table into the minimum number of states and show the reduced state table.

Reduced State Table:

| <b>Present State</b> | Next State, Z   |                      |  |

|----------------------|-----------------|----------------------|--|

|                      | X=0             | X=1                  |  |

| $S_{0,4}$            | $S_{1,2,3}$ , 1 | $S_{0,4}, 0$         |  |

| $S_{1,2,3}$          | $S_{1,2,3}, 0$  | S <sub>0,4</sub> , 1 |  |