## 5 MIPS Assembly Language

- Today, digital computers are almost exclusively programmed using **high-level programming languages** (PLs), *e.g.*, C, C++, Java

- The CPU fetch—execute cycle, however, is not prepared to directly

execute high-level constructs like if-then-else, do-while, arithmetic,

method invocations, etc.

- Instead, a CPU can execute a limited number of rather primitive instructions, its **machine language instruction set**

- Machine language instructions are encoded as bit patterns which are interpreted during the instruction decode phase

- A C/C++/Java compiler is needed to translate high-level constructs into a series of primitive machine instructions

#### Why machine language?

- Even with clever compilers available, machine language level programming is still of importance:

- machine language programs can be carefully tuned for **speed** (*e.g.*, computationally heavy simulations, controlling graphics hardware)

- the size of machine language programs is usually significantly smaller than the size of high-level PL code

- specific computer features may only be available at the machine language level (e.g., I/O port access in device drivers)

- For a number of small scale computers (embedded devices, wearable computers)

- high-level PL compilers are not available yet

- or high-level PLs are simply not adequate because compilers introduce uncertainty about the time cost of programs (e.g., brake control in a car)

#### Machine language vs. assembly language

Real machine language level programming means to handle the bit encodings of machine instructions

**Example** (MIPS CPU: addition  $$t0 \leftarrow $t0 + $t1$ ):

1000010010100000000100000

Assembly language introduces symbolic names (mnemonics) for machine instructions and makes programming less error-prone:

**Example** (MIPS CPU: addition  $$t0 \leftarrow $t0 + $t1$ ):

- An assembler translates mnemonics into machine instructions

- Normally: mnemonic  $\stackrel{1:1}{\longleftrightarrow}$  machine instruction

- Also: the assembler supports **pseudo instructions** which are translated into series of machine instructions (mnemonic  $\stackrel{1:n}{\longleftrightarrow}$  machine instruction)

## The MIPS R2000/R3000 CPU

- Here we will use the MIPS CPU family to explore assembly programming

- MIPS CPU originated from research project at Stanford, most successful and flexible CPU design of the 1990s

- MIPS CPUs were found in SGI graphics workstations, Windows CE handhelds, CISCO routers, and Nintendo 64 video game consoles

- MIPS CPUs follow the RISC (Reduced Instruction Set Computer) design principle:

- limited repertoire of machine instructions

- limited arithmetical complexity supported

- extensive supply of CPU registers (reduce memory accesses)

- Here: work with MIPS R2000 instruction set (use MIPS R2000 simulator SPIM: http://www.cs.wisc.edu/~larus/spim.html)

#### MIPS: memory layout

- The MIPS CPU is a 32-bit architecture (all registers are 32 bits wide)

- Accessible memory range: 0x00000000-0xFFFFFFFF

- MIPS is a von-Neumann computer: memory holds both instructions (*text*) and *data*.

- Specific memory **segments** are coventionally used to tell instructions from data:

| Address    | Segment      |

|------------|--------------|

| 0x7FFFFFFF | stack        |

| <b>+</b>   | $\downarrow$ |

| <b>↑</b>   | $\uparrow$   |

| 0x10000000 | data         |

| 0x00400000 | text         |

| 0x0000000  | reserved     |

If a program is loaded into SPIM, its .text segment is automatically placed at 0x00400000, its .data segment at 0x10000000

### MIPS: 32-bit, little endian

- A MIPS word has 32 bits (a halfword 16 bits, a byte 8 bits)

- The MIPS architecture is little-endian: in memory, a word (halfword) is stored with its least significant byte first

**– Example** (representation of 32-bit word 0x11223344 at address n):

| Address | n    | n+1  | n+2  | n+3  |

|---------|------|------|------|------|

| Value   | 0x44 | 0x33 | 0x22 | 0x11 |

(Intel Pentium: big-endian)

- MIPS requires words (and halfwords) to be stored at aligned addresses:

- if an object is of size s bytes, its storage address needs to be divisble by s (otherwise: CPU halts with address error exception)

#### **MIPS:** registers

• MIPS comes with 32 **general purpose registers** named \$0...\$31 Registers also have symbolic names reflecting their conventional<sup>8</sup> use:

| Register | Alias        | Usage             | Register | Alias | Usage                  |

|----------|--------------|-------------------|----------|-------|------------------------|

| \$0      | \$zero       | constant 0        | \$16     | \$s0  | saved temporary        |

| \$1      | \$at         | used by assembler | \$17     | \$s1  | saved temporary        |

| \$2      | \$v0         | function result   | \$18     | \$s2  | saved temporary        |

| \$3      | \$v1         | function result   | \$19     | \$s3  | saved temporary        |

| \$4      | <b>\$</b> a0 | argument 1        | \$20     | \$s4  | saved temporary        |

| \$5      | \$a1         | argument 2        | \$21     | \$s5  | saved temporary        |

| \$6      | \$a2         | argument 3        | \$22     | \$s6  | saved temporary        |

| \$7      | \$a3         | argument 4        | \$23     | \$s7  | saved temporary        |

| \$8      | \$t0         | unsaved temporary | \$24     | \$t8  | unsaved temporary      |

| \$9      | \$t1         | unsaved temporary | \$25     | \$t9  | unsaved temporary      |

| \$10     | \$t2         | unsaved temporary | \$26     | \$k0  | reserved for OS kernel |

| \$11     | \$t3         | unsaved temporary | \$27     | \$k1  | reserved for OS kernel |

| \$12     | \$t4         | unsaved temporary | \$28     | \$gp  | pointer to global data |

| \$13     | \$t5         | unsaved temporary | \$29     | \$sp  | stack pointer          |

| \$14     | \$t6         | unsaved temporary | \$30     | \$fp  | frame pointer          |

| \$15     | \$t7         | unsaved temporary | \$31     | \$ra  | return address         |

<sup>&</sup>lt;sup>8</sup>Most of these conventions concern procedure call and return (library interoperability)

#### MIPS: load and store

- Typical for the RISC design, MIPS is a **load-store architecture**:

- Memory is accessed only by explicit load and store instructions

- Computation (e.g., arithmetics) reads operands from registers and writes results back into registers

- MIPS: **load** word/halfword/byte at address a into target register r  $(r \leftarrow (a))$ :

| Instruction     | Remark            | Pseudo? |

|-----------------|-------------------|---------|

| lw r, a         |                   |         |

| lh <i>r</i> , a | sign extension    |         |

| lb <i>r, a</i>  | sign extension    |         |

| lhu <i>r, a</i> | no sign extension |         |

| lbu <i>r, a</i> | no sign extension |         |

#### MIPS: load and store

• **Example** (load word/halfword/byte into temporary registers):

```

.text

.globl __start

__start:

# load with sign extension

lw

$t0, memory

$t1, memory

lh

1b $t2, memory

# load without sign extension

lhu

$t3, memory

lbu

$t4, memory

.data

memory:

0xABCDE080

# little endian: 80E0CDAB

.word

```

| Register | Value      |

|----------|------------|

| \$t0     | 0xABCDE080 |

| \$t1     | 0xFFFFE080 |

| \$t2     | 0xFFFFFF80 |

| \$t3     | 0x0000E080 |

| \$t4     | 0x00000080 |

#### MIPS: load and store

• MIPS: **store** word/halfword/byte in register r at address a ( $a \leftarrow r$ ):

| Instruction     | Remark              | Pseudo? |

|-----------------|---------------------|---------|

| sw r, a         |                     |         |

| sh <i>r</i> , a | stores low halfword |         |

| sb <i>r, a</i>  | stores low byte     |         |

**Example** (swap values in registers \$t0 and \$t1):

```

.text

.globl __start

start:

# swap values $t0 and $t1 ... slow!

$t0, x

SW

$t1, y

SW

$t0, y

lw

$t1, x

lw

.data

x:

.word

0x00000FF

y:

0xABCDE080

.word

```

#### MIPS: move

MIPS can **move** data between registers directly (no memory access involved)

| Instruction | Remark                                     | Pseudo? |

|-------------|--------------------------------------------|---------|

| move r, s   | target $r$ , source $s$ $(r \leftarrow s)$ | ×       |

**Example** (swap values in registers \$t0 and \$t1, destroys \$t2):

```

.text

.globl __start

__start:

# swap values $t0 and $t1 (clobbers $t2)

move $t2, $t0

move $t0, $t1

move $t1, $t2

# no .data segment

```

- By convention, destroying the contents of the tn registers is OK (sn registers are assumed intact once a procedure returns r)

### MIPS: logical instructions

• MIPS CPUs provide instructions to compute common boolean functions

| Instruction       | Remark                                                | Pseudo? |

|-------------------|-------------------------------------------------------|---------|

| and $r, s, t$     | $r \leftarrow s \cdot t$                              |         |

| andi $r, s, c$    | $r \leftarrow s \cdot c$ (c constant)                 |         |

| or <i>r, s, t</i> | $r \leftarrow s + t$                                  |         |

| ori <i>r,s,c</i>  | $r \leftarrow s + c$ (c constant)                     |         |

| nor r, s, t       | $r \leftarrow \overline{s+t}$                         |         |

| xor r, s, t       | $r \leftarrow s \text{ XOR } t$                       |         |

| xori r,s,c        | $r \leftarrow s \text{ XOR } c  (c \text{ constant})$ |         |

| not r, s          | $r \leftarrow \overline{s}$                           | X       |

- The andi, ori, xori instructions use **immediate addressing**: the constant c is encoded in the instruction bit pattern **Example** (bit pattern for instruction andi x, y, x with  $0 \le x$ ,  $y \le 31$ ):

#### MIPS: pseudo instructions

The MIPS standard defines the CPU instruction set as well as pseudo instructions

• The assembler translates pseudo instructions into real MIPS instructions **Example** (translation of pseudo instructions):

| Pseudo instruction     | MIPS instruction              | Remark                              |

|------------------------|-------------------------------|-------------------------------------|

| not r, s               | nor <i>r</i> , <i>s</i> , \$0 |                                     |

| move r, s              | or <i>r</i> , <i>s</i> , \$0  |                                     |

| li <i>r</i> , <i>c</i> | ori <i>r</i> ,\$0, <i>c</i>   | load immediate (c: 16 bit constant) |

• How does the assembler translate li r, 0xABCDEF00 (c in ori is 16 bit only)?

| Pseudo instruction | MIPS instructions <sup>9</sup> | Remark               |

|--------------------|--------------------------------|----------------------|

| li r, 0xABCDEF00   | lui \$at, OxABCD               | (c: 32 bit constant) |

|                    | ori <i>r</i> ,\$at,0xEF00      |                      |

$<sup>^9</sup>$ MIPS instruction: lui r, c: load constant halfword c into upper halfword of register r

### MIPS: using pseudo instructions

• **Example** (replace the low byte of \$t0 by the low byte of \$t1, leaving \$t0 otherwise intact—use **bitmasks** and logical instructions):

Expand the pseudo instruction:

| Pseudo instruction         | MIPS instructions    |

|----------------------------|----------------------|

| and \$t0, \$t0, 0xFFFFFF00 | lui \$at,0xFFFF      |

|                            | ori \$at,0xFF00      |

|                            | and \$t0, \$t0, \$at |

## MIPS: optimized register swap

Question: swap the contents of register \$t0 and \$t1 without using memory accesses and without using temporary registers)

```

.text

.globl __start

__start:

# swap values of $t0 and $t1 (xor-based)

xor $t0, $t0, $t1

xor $t1, $t0, $t1

xor $t0, $t1

# no .data segment

```

Explain how this "xor swap" works!

#### Remember:

- (1) a XOR 0 = a

- ② a XOR a = 0

#### **MIPS:** arithmetic instructions

MIPS provides unsigned and signed (two's complement) 32-bit integer arithmetics

| Instruction                         | Remark                    | Pseudo? |

|-------------------------------------|---------------------------|---------|

| add <i>r</i> , <i>s</i> , <i>t</i>  | $r \leftarrow s + t$      |         |

| addu <i>r</i> , <i>s</i> , <i>t</i> | without overflow          |         |

| addi <i>r</i> , <i>s</i> , <i>c</i> | $r \leftarrow s + c$      |         |

| addiu <i>r</i> , s, c               | without overflow          |         |

| sub <i>r</i> , <i>s</i> , <i>t</i>  | $r \leftarrow s - t$      |         |

| subu <i>r</i> , <i>s</i> , <i>t</i> | without overflow          |         |

| mulo r, s, t                        | $r \leftarrow s \times t$ | ×       |

| mul r, s, t                         | without overflow          | ×       |

| $\operatorname{div} r, s, t$        | $r \leftarrow s/t$        | ×       |

| divu r,s,t                          | without overflow          | X       |

- The 64-bit result of mulo (mul) is stored in the special registers hi and lo: lo is moved into  $r^{10}$

- div (divu): MIPS places the quotient in \$10, remainder in \$hi; \$10 is moved into r

<sup>&</sup>lt;sup>10</sup>Access to \$10, \$hi: mflo, mfhi (read) and mtlo, mthi (write)

## MIPS: artihmetic and shift/rotate instructions

| Instruction                        | Remark                                                                                        | Pseudo? |

|------------------------------------|-----------------------------------------------------------------------------------------------|---------|

| abs <i>r</i> , <i>s</i>            | $r \leftarrow  s $                                                                            | ×       |

| neg r, s                           | $r \leftarrow -s$                                                                             | ×       |

| negu <i>r</i> , <i>s</i>           | without overflow                                                                              | ×       |

| rem r, s, t                        | $r \leftarrow \text{remainder of } s/t$                                                       | ×       |

| remu r, s, t                       | without overflow                                                                              | ×       |

| sll <i>r</i> , <i>s</i> , <i>c</i> | $r \leftarrow \text{shift } s \text{ left } c \text{ bits, } r_{0c-1} \leftarrow 0$           |         |

| sllv r, s, t                       | $r \leftarrow \text{shift } s \text{ left } t \text{ bits, } r_{0t-1} \leftarrow 0$           |         |

| srl <i>r, s, c</i>                 | $r \leftarrow \text{shift } s \text{ right } c \text{ bits, } r_{31-c+131} \leftarrow 0$      |         |

| srlv r, s, t                       | $r \leftarrow \text{shift } s \text{ right } t \text{ bits, } r_{31-t+131} \leftarrow 0$      |         |

| sra <i>r, s, c</i>                 | $r \leftarrow \text{shift } s \text{ right } c \text{ bits, } r_{31-c+131} \leftarrow s_{31}$ |         |

| srav <i>r,s,t</i>                  | $r \leftarrow \text{shift } s \text{ right } t \text{ bits, } r_{31-t+131} \leftarrow s_{31}$ |         |

| rol <i>r</i> , <i>s</i> , <i>t</i> | $r \leftarrow \text{rotate } s \text{ left } t \text{ bits}$                                  | ×       |

| ror r, s, t                        | $r \leftarrow \text{rotate } s \text{ right } t \text{ bits}$                                 | X       |

• **Question:** How could the assembler implement the rol, ror pseudo instructions?

## MIPS: shift/rotate instructions

MIPS assemblers implement the pseudo rotation instructions (rol, ror)

based on the CPU shifting instructions:

```

.text

.globl __start

start:

# rotate left 1 bit

.text

.globl __start

$at, 0x8001

lui

ori $t0, $at, 0x0004

start:

# rotate left 1 bit

srl $at, $t0, 31

$t0, 0x80010004

sll $t1, $t0, 1

li

$t1, $t0, 1

$t1, $t1, $at

rol

or

# rotate right 3 bits

# rotate right 3 bits

$t0, 0x80010004

$at, 0x8001

lί

lui

$t1, $t0, 3

ori $t0, $at, 0x004

ror

sll $at, $t0, 29

# no .data segment

srl $t1, $t0, 3

$t1, $t1, $at

or

# no .data segment

```

#### **MIPS:** branch instructions

- **Branch instructions** provide means to change the program control flow (manipulate the CPU IP register)

- The CPU can branch unconditionally (**jump**) or depending on a specified condition (*e.g.*, equality of two registers, register  $\leq 0, \ldots$ )

- In assembly programs, the branch target may be specified via a

label—internally the branch instruction stores an 16-bit offset

```

again: lw $t0, memory

sub $t0, $t0, 1

beqz $t0, exit  # jump offset: 2 instructions

b $t0, again  # jump offset: -4 instructions

exit: sw $t1, memory

:

```

- With a 16-bit offset, MIPS can branch  $2^{15} - 1$  ( $2^{15}$ ) instructions backward (forward)

#### **MIPS:** branch instructions

| Instruction                        | Condition       | Remark        | Pseudo? | MIPS instructions                           |

|------------------------------------|-----------------|---------------|---------|---------------------------------------------|

| ъ <i>I</i>                         | none            | IP ← <i>I</i> | X       | beq \$zero, \$zero, /                       |

| beq <i>r</i> , <i>s</i> , <i>l</i> | r = s           |               |         |                                             |

| bne <i>r</i> , <i>s</i> , /        | $r \neq s$      |               |         |                                             |

| bgez r, l                          | $r \geqslant 0$ |               |         |                                             |

| bgtz r, l                          | r > 0           |               |         |                                             |

| blez $r, l$                        | $r \leqslant 0$ |               |         |                                             |

| bltz r, l                          | r < 0           |               |         |                                             |

| beqz <i>r</i> , /                  | r = 0           |               | ×       | beq r, \$zero, l                            |

| bnez $r, l$                        | $r \neq 0$      |               | ×       | bne r, \$zero, l                            |

| bge <i>r</i> , <i>s</i> , /        | $r \geqslant s$ |               | ×       | slt \$at, <i>r</i> , <i>s</i> <sup>11</sup> |

|                                    |                 |               |         | beq \$at,\$zero,/                           |

| bgt <i>r</i> , <i>s</i> , <i>l</i> | r > s           |               | ×       | slt \$at, <i>s</i> , <i>r</i>               |

|                                    |                 |               |         | bne \$at,\$zero,/                           |

| ble $r, s, l$                      | $r \leqslant s$ |               | ×       | slt \$at, <i>s</i> , <i>r</i>               |

|                                    |                 |               |         | beq \$at,\$zero,/                           |

| blt <i>r</i> , <i>s</i> , <i>l</i> | r < s           |               | ×       | slt \$at, <i>r</i> , <i>s</i>               |

|                                    |                 |               |         | bne \$at,\$zero,/                           |

<sup>11</sup>slt \$at, r, s: \$at  $\leftarrow$  1 if r < s, \$at  $\leftarrow$  0 otherwise.

### **MIPS:** comparison instructions

• Compare the values of two registers (or one register and a constant)

- Comparison

$$\begin{cases} \text{successful: } r \leftarrow 1 \\ \text{fails: } r \leftarrow 0 \end{cases}$$

| Instruction                         | Comparison      | Remark            | Pseudo? | MIPS instructions           |

|-------------------------------------|-----------------|-------------------|---------|-----------------------------|

| slt r, s, t                         | s < t           |                   |         |                             |

| sltu r, s, t                        | s < t           | unsigned          |         |                             |

| slti <i>r,s,c</i>                   | s < c           | c 16-bit constant |         |                             |

| sltiu r, s, c                       | s < c           | unsigned          |         |                             |

| seq r, s, t                         | s = t           |                   | ×       | beq <i>s</i> , <i>t</i> , 3 |

|                                     |                 |                   |         | ori <i>r</i> ,\$zero,0      |

|                                     |                 |                   |         | beq \$zero, \$zero, 2       |

|                                     |                 |                   |         | ori <i>r</i> ,\$zero,1      |

| sne $r$ , $s$ , $t$                 | $s \neq t$      |                   | ×       |                             |

| sge r, s, t                         | $s \geqslant t$ |                   | ×       |                             |

| sgeu <i>r</i> , <i>s</i> , <i>t</i> | $s \geqslant t$ | unsigned          | ×       |                             |

| sgt <i>r,s,t</i>                    | s > t           |                   | ×       |                             |

| sgtu <i>r</i> , <i>s</i> , <i>t</i> | s > t           | unsigned          | ×       |                             |

| sle r, s, t                         | $s \leqslant t$ |                   | ×       |                             |

| sleu r, s, t                        | $s \leqslant t$ | unsigned          | ×       |                             |

#### MIPS: division by zero, overflow

- Arithmetic exceptions (division by 0, overflow during multiplication) are handled on the MIPS instruction layer itself:

- MIPS instructions for div \$t0, \$t1, \$t2:

- MIPS instructions for mulo \$t0, \$t1, \$t2:

```

mult $t1, $t2  # result bits 31..0 in $lo, 63..32 in $hi

mfhi $at

mflo $t0

sra $t0, $t0, 31  # $t0 = 0x00000000 or 0xFFFFFFFF (sign bit)

beq $at, $t0, 2

break $0  # exception: arithmetic overflow

mflo $t0

```

# Compute Fibonacci numbers (iteratively)

- The **Fibonacci numbers**<sup>12</sup> are an infinite sequence of positive integers (originally used to describe the development of rabbit poulations)

- Start of sequence:

- 0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, 89, 144, 233, 377, 610, 987, . . .

- The *n*-th Fibonacci number is **recursively defined** as follows:

$$fib(n) = \begin{cases} 0 & \text{if } n = 0\\ 1 & \text{if } n = 1\\ fib(n-2) + fib(n-1) & \text{if } n \geqslant 2 \end{cases}$$

**Example** (compute fib(3)):

$$fib(3) = fib(1) + fib(2) = 1 + fib(0) + fib(1) = 1 + 0 + 1 = 2$$

<sup>&</sup>lt;sup>12</sup>Leonardo Fibonacci (Leonardo di Pisa), 1200

# Compute Fibonacci numbers (iteratively)

| Register | Usage                                              |

|----------|----------------------------------------------------|

| \$a0     | parameter <i>n</i>                                 |

| \$v0     | last Fibonacci number computed so far (and result) |

| \$t0     | second last Fibonacci number computed so far       |

| \$t1     | temporary scratch register                         |

```

.text

.globl __start

__start:

$a0, 1

li

# fib(n): parameter n

$v0, $a0

\# n < 2 \Rightarrow fib(n) = n

move

$a0, 2, done

blt

li

$t0, 0

# second last Fib' number

li

$v0, 1

# last Fib' number

add

$t1, $t0, $v0

# compute next Fib' number in sequence

fib:

$t0, $v0

# update second last

move

$v0, $t1

# update last

move

$a0, $a0, 1

# more work to do?

sub

$a0, 1, fib

bgt

# yes: iterate again

done:

$v0, result

# no: store result, done

SW

.data

```

result: .word

0x11111111

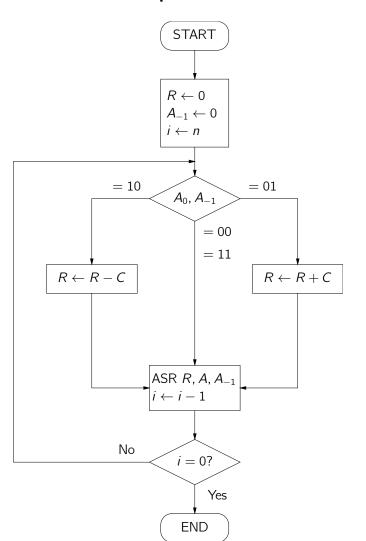

## MIPS: Booth's algorithm

- Remember Booth's algorithm to multiply two's complement numbers

- Note: equivalent functionality is provided by MIPS instruction mult

- Register assignment:

| Register | Usage                              |

|----------|------------------------------------|

| \$a0     | A                                  |

| \$a1     | C                                  |

| \$v0     | R                                  |

| \$t0     | i                                  |

| \$t1     | $A_{-1}$ (only bit 0 of \$t1 used) |

– Implementation quite straightforward, ASR of "connected registers" R, A,  $A_{-1}$  needs some care

#### MIPS: Booth's algorithm

```

.text

.globl __start

__start:

$a0, -5

li

# parameter A

li

$a1, 7

# parameter C

li

$v0, 0

# R <- 0

\# A(-1) < - 0

li

$t1, 0

$t0, 32

# i <- n (32 bits)

li

booth:

$t2, $a0, 0x00000001 # $t2 <- A0

and

sll

$t2, $t2, 1

$t2, $t2, $t1

# $t2 = A0, A(-1)

or

# $t2 = 10?

$t2, 2, case10

beq

# $t2 = 01?

$t2, 1, case01

beq

# $t2 = 00 \text{ or } $t2 = 11

shift

b

$v0, $v0, $a1

case10: sub

# R <- R - C

shift

$v0, $v0, $a1

# R <- R + C

case01: add

shift:

t1, t0, 0x00000001  # A(-1) <- A0

and

$t2, $v0, 0x00000001 # save R0

and

$t2, $t2, 31

sll

srl

$a0, $a0, 1

# shift right A

$a0, $a0, $t2

# A31 <- R0

or

$v0, $v0, 1

# arithmetic shift right R

sra

sub

$t0,$t0, 1

# i <- i - 1

$t0, booth

# i = 0?

bnez

# result in $v0,$a0

```

### MIPS: Addressing modes

A MIPS instruction like

1b \$t0, memory

addresses a given, fixed address in memory.

• Commonly, however, programs need to access consecutive ranges of memory addresses (e.g., to perform string processing)

**Example** (place string representation in the data segment):

.data

str: .asciiz "foobar" # null-terminated ASCII encoded string

Content of data segment at address str:

| Address | str+0 | str+1 | str+2 | str+3 | str+4 | str <b>+5</b> | str+6 |

|---------|-------|-------|-------|-------|-------|---------------|-------|

| Value   | 102   | 111   | 111   | 98    | 97    | 114           | 0     |

## MIPS: Addressing modes

• **Assembler instructions** available to place constant sequences of data into data segment:

| Assembler instruction     | Data                                                              |

|---------------------------|-------------------------------------------------------------------|

| .ascii <i>s</i>           | ASCII encoded characters of string s                              |

| .asciiz <i>s</i>          | like .ascii, null-terminated                                      |

| .word $w_1, w_2, \ldots$  | 32-bit words $w_1, w_2, \ldots$                                   |

| .half $h_1, h_2, \ldots$  | 16-bit halfwords $h_1, h_2, \ldots$                               |

| .byte $b_1, b_2, \dots$   | 8-bit bytes $b_1, b_2, \ldots$                                    |

| .float $f_1, f_2, \dots$  | 32-bit single precision floating point numbers $f_1, f_2, \ldots$ |

| .double $d_1, d_2, \dots$ | 64-bit double precision floating point numbers $d_1, d_2, \ldots$ |

| .space <i>n</i>           | n zero bytes                                                      |

• To consecutively access all characters (bytes, halfwords, words) in such a sequence, the CPU needs to **compute the next address** to access

#### MIPS: Indirect addressing

• Indirect Addressing: address is held in a register

#### **Example**:

```

la $t0, str

lb $t1, ($t0) # access byte at address $t0 ('f')

add $t0, $t0, 3

lb $t2, ($t0) # access byte at address $t0 + 3 ('b')

.data

str: .asciiz "foobar"

```

lw \$t0, a and la \$t0, a

#### MIPS: Indexed addressing

- Actually, in keeping with the RISC philosophy, MIPS has only one general memory addressing mode: indexed addressing

- In indexed addressing, addresses are of the form (16-bit constant c, CPU register r)

r holds a 32-bit address to which the signed 16-bit constant c is added to form the final address

**Example** (repeated from last slide):

.text

```

la $t0, str

lb $t1, 0($t0)  # access byte at address $t0 ('f')

lb $t2, 3($t0)  # access byte at address $t0 + 3 ('b')

```

.data

```

str: .asciiz "foobar"

```

### MIPS: Indexed addressing

• **Example** (copy a sequence of *n* bytes from address src to address dst):

```

.text

.globl __start

__start:

# length n of byte sequence - 1

$t0, 5

li

copy:

lb

$t1, src($t0)

# pseudo! (src: 32 bits wide)

sb

$t1, dst($t0)

$t0, $t0, 1

sub

$t0, copy

bgez

.data

.byte 0x11, 0x22, 0x33, 0x44, 0x55, 0x66

src:

.space 6

dst:

```

Questions: which changes are necessary to turn this into a n word (n halfword) copy routine?

#### MIPS: Optimized copy routine

• Copying byte sequences via 1b/sb is inefficient on von-Neumann machines

```

.text

.globl

__start

__start:

$a0, 11

# length n of byte sequence

li

# source address

la

$a1, src

la

$a2, dst

# destination address

$t1, $a0, 0x03

and

srl

$t0, $a0, 2

beqz

$t0, rest

copy:

$t2, ($a1)

lw

$t2, ($a2)

SW

$a1, $a1, 4

add

add

$a2, $a2, 4

sub

$t0, $t0, 1

copy

beqz

$t1, done

rest:

lb

$t2, ($a1)

sb

$t2, ($a2)

add

$a1, $a1, 1

add

$a2, $a2, 1

$t1, $t1, 1

sub

rest

done:

.data

.align 4

.byte 0x00, 0x11, 0x22, 0x33, 0x44, 0x55, 0x66, 0x77, 0x88, 0x99, 0xAA

src:

.align 4

dst:

.space 11

```

# MIPS: Addressing modes (summary)

| Mode        | Example                  | MIPS instruction(s)                                                    | Remark [Address]                                                           |

|-------------|--------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------|

| immediate   | andi \$t0,\$t0,0x03      |                                                                        | 16-bit constant embedded in instruction                                    |

| IP relative | beqz \$t0, done          |                                                                        | signed 16-bit jump offset $o$ embedded in instruction [IP $+ 4 \times o$ ] |

| direct      | lw \$t0,0x11223344       | lui \$at,0x1122<br>lw \$t0,0x3344(\$at                                 | [0x11223344]<br>)                                                          |

| indirect    | lw \$t0, (\$t1)          | lw \$t0,0(\$t1)                                                        | [\$t1]                                                                     |

| indexed     | lw \$t0,0x11223344(\$t1) | <pre>lui \$at, 0x1122 addu \$at, \$at, \$t1 lw \$t0, 0x3344(\$at</pre> | [0x11223344 + \$t1]                                                        |

### **SPIM: System calls**

- The MIPS emulator SPIM provides a few services (**system calls**) which would normally be provided by the underlying **operating system**

- Most importantly, these services provide basic console input/output

(I/O) functionality to read/write numbers and strings

| Service                 | Call code | Arguments                          | Result        |

|-------------------------|-----------|------------------------------------|---------------|

| print integer           | 1         | \$a0: integer                      |               |

| print null-term. string | 4         | \$a0: string address               |               |

| read integer            | 5         |                                    | \$v0: integer |

| read string             | 8         | \$a0: buffer address, \$a1: length |               |

| exit                    | 10        |                                    |               |

#### **Remarks:**

- Place system call code in \$v0, then execute syscall

- System call read integer reads an entire line (including newline) and ignores characters following the number

- The *read string* system call reads at most a1 1 characters into the buffer and terminates the input with a null byte

## **SPIM: System calls**

• **Example** (read integer n from SPIM console, then print  $42 \times n$  on console):

```

.text

.globl __start

start:

$v0, 5

li

# read integer

syscall

mul

$t0, $v0, 42

# compute and save result

li $v0, 4

# print string

la

$a0, the_result_is

syscall

$v0, 1

li

# print integer

$a0, $t0

move

syscall

$v0, 10

li

# exit

syscall

.data

the_result_is:

.asciiz "The result is "

```

#### **SPIM: System calls**

- **Example** (read integer *n*, then print hexadecimal equivalent on console):

- **Idea**: groups of 4 bits correspond to one hexadecimal digit (0...F), use value of group (0...15) as index into table of hexadecimal digits

```

.text

.globl __start

__start:

$v0, 5

li

# read integer n

syscall

$t0, $v0

# save n

move

$t1, 7

li

# 7 (+ 1) hex digits for 32 bits

$t2, $t0, 0x0F

# extract least significant 4 bits

hexify:

and

srl $t0, $t0, 4

# prepare for next digit

$t3, hex_table($t2)

lb

# convert 4 bit group to hex digit

sb

$t3, hex_digits($t1)

# store hex digit

sub $t1, $t1, 1

# next digit

# more digits?

bgez

$t1, hexify

li $v0, 4

# print string

$a0, the_result_is

la

syscall

$v0, 10

# exit

li

syscall

.data

.ascii "0123456789ABCDEF"

hex_table:

the_result_is: .ascii "Hexadecimal value: 0x"

```

hex\_digits: .asciiz "XXXXXXXX"

#### **Bubble sort**

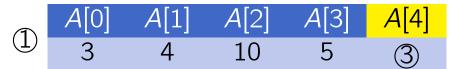

- **Bubble sort** is a simple sorting algorithm (with *quadratic complexity*: to sort n items, bubble sort in general needs  $n^2$  steps to complete)

- **Input:** array A of n items (numbers, strings, . . . ) and an ordering <, e.g., n = 5:

| A[0] | A[1] | A[2] | A[3] | A[4] |

|------|------|------|------|------|

| 3    | 4    | 10   | 5    | 3    |

- Output: sorted array A, e.g.:

| A[0] | A[1] | A[2] | A[3] | <i>A</i> [4] |

|------|------|------|------|--------------|

| 3    | 3    | 4    | 5    | 10           |

#### • Basic idea:

- ①  $j \leftarrow n-1$  (index of last element in A)

- ② If A[j] < A[j-1], swap both elements

- ③  $j \leftarrow j 1$ , goto ② if j > 0

- (4) Goto (1) if a swap occurred

## **Bubble sort (trace)**

Swap occured? (Yes, goto ①)

| <b>1</b>                | A[0] | A[1] | A[2] | A[3] | <i>A</i> [4] |

|-------------------------|------|------|------|------|--------------|

| $\overline{\mathbf{T}}$ | 3    | 3    | 4    | 10   | (5)          |

#### MIPS: Bubble sort

```

.text

.globl

__start

start:

li

$a0, 10

# parameter n

sll

$a0, $a0, 2

# number of bytes in array A

outer:

$t0, $a0, 8

# $t0: j-1

sub

li

$t1, 0

# no swap yet

inner:

$t2, A+4($t0)

# $t2 <- A[j]

lw

$t3, A($t0)

# $t3 <- A[j-1]

lw

# A[i] <= A[i-1]?

$t2, $t3, no_swap

bgt

$t2, A($t0)

# A[j-1] <- $t2 \setminus move bubble

SW

$t3, A+4($t0)

# A[j] <- $t3 / $t2 upwards

SW

li

# swap occurred

$t1, 1

no_swap:

$t0, $t0, 4

sub

# next array element

# more?

$t0, inner

bgez

bnez

$t1, outer

# did we swap?

$v0, 10

li

# exit

syscall

.data

A:

# array A (sorted in-place)

.word 4,5,6,7,8,9,10,2,1,3

```

## Procedures (sub-routines)

- The solution to a complex programming problem is almost always assembled from simple program pieces (procedures) which constitute a small building block of a larger solution

- Often, procedures provide some service which can then be requested by the main program in many places

- Instead of copying and repeating the procedure code over and over,

- the main program calls the procedure (jumps to the procedure code),

- ② the called procedure does its job before it returns control (jumps back to the instruction just after the procedure call)

- The main program is often referred to as the caller, the procedure as the callee

### MIPS: Procedure example

- **Example** (procedure to compute the average of two parameters x, y):

- Input: parameter x in \$a0, parameter y in \$a1

- Output: average of x, y in \$v0  $\left(\$v0 \leftarrow \frac{\$a0 + \$a1}{2}\right)$

.text

```

# procedure average (x,y)

# input: x in $a0, y in $a1

# output: $v0

average:

add $v0, $a0, $a1 # $v0 <- $a0 + $a1

sra $v0, $v0, 1 # $v0 <- $v0 / 2

j ??? # where to return to?</pre>

```

#### MIPS: Procedure call

• A typical main program (caller of average) might look like as follows:

.text

```

lί

$a0, $t0

# set parameter x

li

$a1, 12

# set parameter y

average

# compute average

$t0, $v0

# save result

★1:

move

li

$a0, $t0

# set parameter x

li $a1, $t1

# set parameter y

# compute average

average

★2:

$t1, $v0

# save result

move

```

• After the first call, average needs to return to label  $\bigstar 1$ , after the second call the correct address to return to is  $\bigstar 2$

#### MIPS: Procedure call and return

MIPS instruction jal (jump and link) jumps to the given address a

(procedure entry point) and records the correct return address in

register \$ra:

| Instruction | Effect                 |

|-------------|------------------------|

| jal a       | $ra \leftarrow IP + 4$ |

|             | $IP \leftarrow a$      |

• The callee may then simply return to the correct address in the caller via

| Instruction | Effect                        |

|-------------|-------------------------------|

| j \$ra      | $IP \leftarrow \mathtt{\$ra}$ |

- \$ra is reserved MIPS CPU register \$31; programs overwriting/abusing

\$ra are likely to yield chaos

#### MIPS: Procedure call and return<sup>13</sup>

```

:

li

$a0, $t0

# set parameter x

lί

$a1, 12 # set parameter y

# compute average ($ra = ★1)

jal

average

# save result

★1:

move $t0, $v0

li $a0, $t0

# set parameter x

li $a1, $t1

# set parameter y

# compute average ($ra = ★2)

jal average

move $t1, $v0

# save result

★2:

li

$v0, 10

# exit program

syscall

# procedure average (x,y)

input: x in $a0, y in $a1

output: $v0

average:

$v0, $a0, $a1  # $v0 <- $a0 + $a1

add

$v0, $v0, 1 # $v0 <- $v0 / 2

sra

$ra

# return to caller

```

.text

<sup>&</sup>lt;sup>13</sup>NB: The  $\bigstar$  labels merely illustrate the effect of jal and do not appear in the real assembly file

### Recursive algorithms/procedures

- Some algorithms solve a complex problem as follows:

- ① Is the size of the problem such that we can trivially solve it?

Yes ⇒ Return the answer immediately

- ② Try to reduce the size/complexity of the original problem

- (3) Invoke the algorithm on the reduced problem

- In step ③, the algorithm *invokes itself* to compute the answer; such algorithms are known as **recursive**

- Recursion may also be used in MIPS assembly procedures, typically:

```

.text

:

proc: ... # code for procedure proc

:

jal proc # recursive call

:

```

### **Binary search**

- **Binary search** is a recursive algorithm that searches for a given value (needle) in a sorted array of values

- General idea:

- ① If the array is of size 1 only, compare *needle* against the array entry, return result of comparison (true/false)

- ② Locate the middle array entry m; compare *needle* and m

- $\bigcirc$  If needle = m return true

- If needle < m, call binary search on left half of array</li>

- Otherwise, call binary search on right half of array

- NB: since the array is sorted, we know for all entries a to the left of m that  $a \le m$  (for all entries b to the right of m:  $b \ge m$ )

# Binary search (example, needle = 35)

| $\bigcirc$ | A[0] | A[1]     | A[2] | A[3]         | A[4]         | <i>A</i> [5]    | <i>A</i> [6]       | <i>A</i> [7]       | A[8]            | A[9]            |

|------------|------|----------|------|--------------|--------------|-----------------|--------------------|--------------------|-----------------|-----------------|

| 1          | 2    | 3        | 8    | 10           | 16           | 21              | 35                 | 42                 | 43              | 50              |

|            | A[0] | A[1]     | A[2] | <i>A</i> [3] | <i>A</i> [4] | <i>A</i> [5]    | A[6]               | <i>A</i> [7]       | A[8]            | <b>A</b> [9]    |

| 2          | 2    | 3        | 8    | 10           | 16           | 21              | 35                 | 42                 | 43              | 50              |

|            | _    |          |      | 10           | 10           | <b>4</b>        |                    | 12                 | 10              |                 |

| <b>2</b>   |      |          |      |              |              | A[5]            | A[6]               | A[7]               | A[8]            | <b>A</b> [9]    |

| 3          | 2    | 3        | 8    | 10           | 16           | 21              | 35                 | 42                 | 43              | 50              |

| ı          |      |          |      |              |              | <b>V[E]</b>     | <b>1</b> [6]       | <b>∧[</b> 7]       | /[O]            | 4[0]            |

| 2          | 2    | 3        | 8    | 10           | 16           | <i>A</i> [5] 21 | <i>A</i> [6] 35    | <i>A</i> [7]<br>42 | <i>A</i> [8] 43 | <i>A</i> [9] 50 |

|            |      | <u> </u> | U    | 10           | 10           | <b>Z</b> I      | <b>33</b>          | TL                 | тЭ              | 30              |

|            |      |          |      |              |              | <i>A</i> [5]    | <i>A</i> [6]       | A[7]               |                 |                 |

| 3          | 2    | 3        | 8    | 10           | 16           | 21              | 35                 | 42                 | 43              | 50              |

| Ī          |      |          |      |              |              | <b>∧</b> [⊏]    | <u> </u>           | <b>Λ</b> [¬]       |                 |                 |

| 2          | 2    | 3        | 8    | 10           | 16           | <i>A</i> [5] 21 | <i>A</i> [6]<br>35 | <i>A</i> [7] 42    | 43              | 50              |

|            |      | 3        | O    | 10           | 10           | <b>Z I</b>      | 33                 | 42                 | 43              | 30              |

|            |      |          |      |              |              | A[5]            | A[6]               | A[7]               |                 |                 |

| 3          | 2    | 3        | 8    | 10           | 16           | 21              | 35                 | 42                 | 43              | 50              |

### Binary search: efficiency

- Binary search is very efficient: in each recursive call, the size of the problem is cut in half

- Let the original array come with n entries; each recursive call halves the problem size:

$$n \cdot \frac{1}{2} \cdot \frac{1}{2} \cdot \frac{1}{2} \cdots$$

Binary search is guaranteed to end after s recursive calls when the array size has been reduced to 1:

$$n \cdot \left(\frac{1}{2}\right)^s \stackrel{!}{=} 1 \quad \Leftrightarrow \quad \frac{n}{2^s} = 1 \quad \Leftrightarrow \quad s = \log_2 n$$

| array size n | $\lceil \log_2 n \rceil$ |

|--------------|--------------------------|

| 10           | 4                        |

| 100          | 7                        |

| 1000         | 10                       |

| 10000        | 14                       |

| 100000       | 17                       |

| 1000000      | 20                       |

### MIPS: Recursive procedures

Note that the MIPS procedure call/return via jal a/j \$ra does not work for recursive procedures

#### • What is going wrong?

Using jal in callee *overwrites* register \$ra which is later needed to return to caller:

```

.text

# main program

# invoke procedure ($ra = \pm 1)

jal proc

★1:

# procedure

proc:

# recursive call ($ra = $\star 2)

jal proc

★2:

(will jump to \bigstar 2, not \bigstar 1)

$ra

```

# MIPS: Save/restore \$ra in recursive procedure

```

.text

# main program

jal proc

# invoke procedure ($ra = \pm 1)

★1:

# procedure

save $ra

proc:

# recursive call ($ra = $\star 2)

jal proc

★2:

restore $ra

# will jump to \bigstar 1

$ra

```

NB: Each invocation of proc needs its own place to save

\$ra—the save location will otherwise be overwritten in the recursive call!

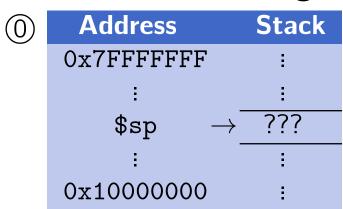

- Conventionally, procedures save registers on the stack if they need to preserve register values

- A stack is an area of memory that may grow/shrink depending on the actual space needed by a program

- CPU register \$sp points just below the last object stored on the stack

- Pushing more items on the stack moves \$sp and lets the stack grow

- **Example** (MIPS: push 32-bit word z on stack):

subu

$$$sp, $sp, 4$$

$sw z, 4($sp)$

| Address    | Stack |

|------------|-------|

| 0x7FFFFFFF | ÷     |

| :          | ÷     |

| p + 8      | X     |

| p+4        | У     |

| sp 	o      |       |

| :          | i i   |

| 0x10000000 | ÷     |

| before     |       |

| Address    | Stack |

|------------|-------|

| 0x7FFFFFFF | :     |

| <b>:</b>   | :     |

| sp + 12    | X     |

| sp + 8     | У     |

| sp + 4     | Z     |

| sp 	o      |       |

| ÷          | :     |

| 0x10000000 | :     |

| after      |       |

```

.text

1

.globl

__start

__start:

$a0, 1

# (0)

li

jal

proc

done:

$v0, 10

li

syscall

10 proc:

$sp, $sp, 4

subu

11

$ra, 4($sp) # (1),(2)

12

SW

13

beqz

$a0, return

14

li

$a0, 0

15

16

jal

proc

17

18 return:

$ra, 4($sp)

lw

19

$sp, $sp, 4 # (3),(4)

addu

20

$ra

21

# no .data segment

23

```

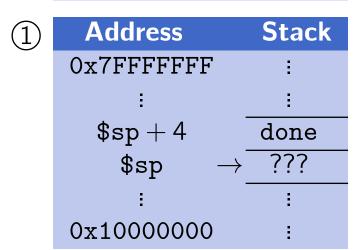

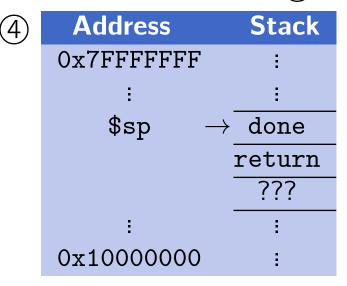

#### State of stack at time (t):

#### State of stack at time (t):

| 1  |                  | .text    |        |         |   |          |

|----|------------------|----------|--------|---------|---|----------|

| 2  |                  | .globl   | sta    | art     |   |          |

| 3  | start            | •        |        |         |   |          |

| 4  |                  | li       | \$a0,  | 1       | # | (0)      |

| 5  |                  | jal      | proc   |         |   |          |

| 6  | done:            |          |        |         |   |          |

| 7  |                  | li       | \$v0,  | 10      |   |          |

| 8  |                  | syscall  |        |         |   |          |

| 9  |                  |          |        |         |   |          |

| 10 | <pre>proc:</pre> |          |        |         |   |          |

| 11 |                  | subu     | _      | \$sp, 4 |   |          |

| 12 |                  | sw       | \$ra,  | 4(\$sp) | # | (1),(2)  |

| 13 |                  |          |        |         |   |          |

| 14 |                  | beqz     |        |         |   |          |

| 15 |                  | li       | \$a0,  | 0       |   |          |

| 16 |                  | jal      | proc   |         |   |          |

| 17 |                  |          |        |         |   |          |

| 18 | return:          |          |        |         |   |          |

| 19 |                  |          |        | 4(\$sp) |   |          |

| 20 |                  | addu     | \$sp,  | \$sp, 4 | # | (3), (4) |

| 21 |                  | j        | \$ra   |         |   |          |

| 22 |                  |          |        |         |   |          |

| 23 |                  | # no .da | ata se | egment  |   |          |

|    |                  |          |        |         |   |          |

| 2 | Address    | Stack  |

|---|------------|--------|

|   | 0x7FFFFFF  | :      |

|   | 1          |        |

|   | sp + 8     | done   |

|   | sp+4       | return |

|   | \$sp -     | → ???  |

|   | <b>!</b>   | :      |

|   | 0x10000000 | :      |

| 3 | Address    | Stack    |

|---|------------|----------|

|   | 0x7FFFFFF  | ÷        |

|   | i i        |          |

|   | sp+4       | done     |

|   | \$sp -     | → return |

|   |            | ???      |

|   | i          | :        |

|   | 0x10000000 | 1        |

```

.text

1

__start

.globl

__start:

$a0, 1

# (0)

li

jal

proc

done:

li

$v0, 10

syscall

10 proc:

$sp, $sp, 4

subu

11

$ra, 4($sp) # (1),(2)

12

SW

13

$a0, return

beqz

14

li

$a0, 0

15

16

jal

proc

17

18 return:

$ra, 4($sp)

lw

19

$sp, $sp, 4

#(3),(4)

addu

20

$ra

21

# no .data segment

23

```

#### State of stack at time (t):

NB: the memory pointed to by \$sp and below is considered garbage

### MIPS: Recursive binary search

• **Example** (recursive binary search procedure, \$ra saved on stack):

```

.data

1

3 first: # sorted array of 32 bit words

.word 2, 3, 8, 10, 16, 21, 35, 42, 43, 50, 64, 69

.word 70, 77, 82, 83, 84, 90, 96, 99, 100, 105, 111, 120

6 last:

# address just after sorted array

.text

.globl __start

__start:

11

# binary search in sorted array

12

input: search value (needle) in $a0

13

base address of array in $a1

14

last address of array in $a2

15

output: address of needle in $v0 if found,

16

#

0 in $v0 otherwise

17

$a0, 42

li

# needle value

18

$a1, first

# address of first array entry

la

19

# address of last array entry

la

$a2, last - 4

20

binsearch

jal

# perform binary search

21

22

li $v0, 10

23

syscall

24

25

```

## MIPS: Recursive binary search (cont.)

```

binsearch:

$sp, $sp, 4

subu

# allocate 4 bytes on stack

27

# save return address on stack

$ra, 4($sp)

SW

subu

$t0, $a2, $a1

# $t0 <- size of array

bnez

$t0, search

# if size > 0, continue search

$v0, $a1

# address of only entry in array

33

move

lw

$t0, ($v0)

# load the entry

34

# equal to needle value? yes => return

$a0, $t0, return

beq

li

$v0, 0

# no => needle not in array

36

b

return

# done, return

37

search:

$t0, $t0, 3

# compute offset of middle entry m:

sra

$t0, $t0, 2

$t0 <- ($t0 / 8) * 4

sll

addu

$v0, $a1, $t0

# compute address of middle entry m

$t0, ($v0)

# $t0 <- middle entry m

lw

42

$a0, $t0, return

# m = needle? yes => return

43

beq

blt

$a0, $t0, go_left

# needle less than m? yes =>

44

# search continues left of m

45

46 go_right:

addu

$a1, $v0, 4

# search continues right of m

jal

# recursive call

binsearch

return

# done, return

49

50 go_left:

$a2, $v0

# search continues left of m

move

binsearch

# recursive call

jal

53 return:

$ra, 4($sp)

# recover return address from stack

lw

54

$sp, $sp, 4

addu

# release 4 bytes on stack

55

56

$ra

# return to caller

57

```