## King Fahd University of Petroleum and Minerals College of Computer Science and Engineering Computer Engineering Department

#### ICS 233: COMPUTER ARCHITECTURE & ASSEMBLY LANGUAGE

Term 142 (Spring 2014-2015) Major Exam II Sunday April 19, 2015

Time: 150 minutes, Total Pages: 13

| Name:_ |                         | ID:                 | Section: |

|--------|-------------------------|---------------------|----------|

| Notes: |                         |                     |          |

| •      | Do not open the exam bo | ok until instructed |          |

| •      | Answer all questions    |                     |          |

| •      | All steps must be shown |                     |          |

• Any assumptions made must be clearly stated

| Question | Max Points | Score |

|----------|------------|-------|

| Q1       | 12         |       |

| Q2       | 15         |       |

| Q3       | 18         |       |

| Q4       | 30         |       |

| Total    | 75         |       |

Dr. Aiman El-Maleh Dr. Mayez Al-Mouhamed (Q1) Write a procedure, GCD, that receives two positive numbers in \$a0 and \$a1 and returns their greatest common divisor in register \$v0. It is required that the procedure **preserves the content of all used registers** according to the MIPS programming convention by saving them and restoring them on the stack. Then, write a program that reads two positive numbers from the user and displays the GCD obtained by the above procedure. The pseudo code of the GCD procedure is given below:

```

int gcd(int m, int n) {

if ((m % n) == 0)

return n;

else

return gcd(n, m % n);

}

```

#### A **sample execution** of the program is:

Enter two numbers:

90

24

GCD is: 6

A summary of syscall services you can use is given below:

| Service       | \$v0 | Arguments / Result                       |

|---------------|------|------------------------------------------|

| Print Integer | 1    | \$a0 = integer value to print            |

| Print String  | 4    | \$a0 = address of null-terminated string |

| Read Integer  | 5    | \$v0 = integer read                      |

| Exit          | 10   |                                          |

Page 3 of 13 move \$a0, \$v0

li \$v0, 5 syscall move \$a1, \$v0

jal GCD move \$t0, \$v0

li \$v0, 4 la \$a0, msg2 syscall

move \$a0, \$t0 li \$v0, 1 syscall

li \$v0, 10 # Exit program syscall

GCD: divu \$a0, \$a1 mfhi \$t0 bne \$t0, \$0, Else move \$v0, \$a1 jr \$ra Else: addi \$sp, \$sp, -4 sw \$ra, (\$sp) move \$a0, \$a1 move \$a1, \$t0 jal GCD lw \$ra, (\$sp) addi \$sp, \$sp, 4

jr \$ra

(Q2)

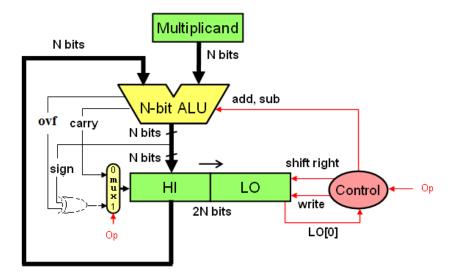

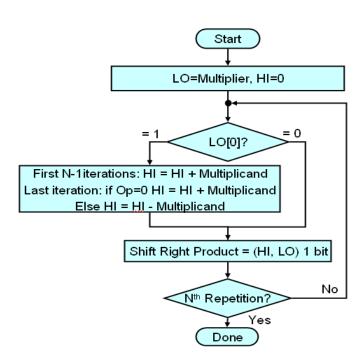

- You are required to design a circuit that can be used to perform either signed or unsigned multiplication of two 32-bit operands A and B depending on an input signal OP. When OP=0, the circuit will perform unsigned multiplication. Otherwise, it will perform signed multiplication.

- a. Given the circuit below, which performs unsigned multiplication, add the necessary changes so that it can be used for performing either signed or unsigned multiplication depending on OP.

b. Show the algorithm that will be used along with your circuit in (a) for performing either signed or unsigned multiplication depending on OP.

(ii) Given that Multiplicand=1010 and Multiplier=1011, using the signed multiplication hardware, show the signed multiplication of Multiplicand by Multiplier. The result of the multiplication should be an 8 bit signed number in HI and LO registers. Show the steps of your work.

| Iteration |                                      | Multiplicand | Sign | Product = HI,LO         |

|-----------|--------------------------------------|--------------|------|-------------------------|

| 0         | Initialize (LO = Multiplier)         | 1010         |      | 0000 101 <b>1</b>       |

| 1         | $LO[0] = 1 \Rightarrow ADD$          |              | 1    | 1010 1011               |

|           | Shift Product = (HI, LO) right 1 bit | 1010         |      | 1101 010 <b>1</b>       |

| 2         | $LO[0] = 1 \Rightarrow ADD$          |              | 1    | 0111 0101               |

|           | Shift Product = (HI, LO) right 1 bit | 1010         |      | 1011 101 <b>0</b>       |

| 3         | $LO[0] = 0 \Rightarrow Do nothing$   |              | 1    | 1011 1010               |

|           | Shift Product = (HI, LO) right 1 bit | 1010         |      | 1101 110 <mark>1</mark> |

| 4         | LO[0] = 1 => SUB                     |              | 0    | 0011 1101               |

|           | Shift Product = (HI, LO) right 1 bit |              |      | 0001 1110               |

(iii) Given that **Dividend=1011** and **Divisor=0010**, Using the **unsigned division** hardware, show the **unsigned** division of **Dividend** by **Divisor**. The result of division should be stored in the Remainder and Quotient registers. Show the steps of your work.

| Iteration |                                      | Remainder     | Quotient     | Divisor | Difference |

|-----------|--------------------------------------|---------------|--------------|---------|------------|

|           |                                      | ( <b>HI</b> ) | (LO)         |         |            |

| 0         | Initialize                           | 0000          | 1011         | 0010    |            |

| 1         | 1: SLL, Difference                   | 0001          | 0110         | 0010    | 1111       |

|           | 2: Diff $< 0 \Rightarrow$ Do Nothing | 0001          | 0110         | 0010    |            |

| 2         | 1: SLL, Difference                   | 0010          | 1100         | 0010    | 0000       |

|           | 2: Rem = Diff, set lsb Quotient      | 0000          | 110 <b>1</b> | 0010    |            |

| 3         | 1: SLL, Difference                   | 0001          | 1010         | 0010    | 1111       |

|           | 2: Diff < 0 => Do Nothing            | 0001          | 1010         | 0010    |            |

| 4         | 1: SLL, Difference                   | 0011          | 0100         | 0010    | 0001       |

|           | 2: Rem = Diff, set lsb Quotient      | 0001          | 0101         | 0010    |            |

(Q3)

1. [3 Points] What is the decimal value of following single precision float:

2. [3 Points] Find the normalized single precision representation of –21.625.

- 3. [2 Points] Find the smallest positive normalized float for single precision.

- $\Rightarrow$  Exponent bias = 1 127 = –126 (smallest exponent for SP)

- $\Rightarrow$  Significand =  $(1.000 \dots 0)_2 = 1$

- $\Rightarrow$  Value in decimal =  $1 \times 2^{-126} = 1.17549 \dots \times 10^{-38}$

- 4. [2 Points] Find the largest positive denormalized float for single precision.

- $\Rightarrow$  Exponent = -126

- $\Rightarrow$  Significand =  $(0.111 \dots 1)_2 \approx 1$

- ♦ Value in decimal  $\approx 1 \times 2^{-126}$  Exact value =1.1754942 × 10<sup>-38</sup>

- 5. [3 Points] Give the representation of Zero, -infinity, and NAN for single precision:

-infinity:

$$[\ 1\ ,\ 111111111\ ,\ 000\ 0000\ 0000\ 0000\ 0000\ 0000\ ]$$

6. [5 Points] Find the normalized difference between A and B by using rounding to nearest even. Perform the operation using **guard**, **round** and **sticky** bits

```

A= + 1.000\ 0001\ 0000\ 1111\ 1000\ 0001 \times 2^4

B= +1.000\ 0111\ 1100\ 0000\ 1010\ 0000 \times 2^{-3}

```

(Q4)

The instruction set (ISA<sub>x</sub>) of a 32-bit RISC processor with 32 registers is defined as follows:

a. R-type: register-d = register-t op register-s, where each register denotes one of the 32-bit user registers, and op denotes an arithmetic or logic operation.

| INTRUCTION | OPCODE |

|------------|--------|

| Add        | 0000   |

| Sub        | 0001   |

| Or         | 0010   |

| And        | 0011   |

b. I-type: register-t = register-s op imm16, where imm16 denotes a 16-bit immediate data.

| INTRUCTION | OPCODE |

|------------|--------|

| Addi       | 0100   |

| Subi       | 0101   |

| Ori        | 0110   |

| Andi       | 0111   |

c. LS-type: load using register-t = M(register-s) and store using M(register-s) = register-t, where M is the data memory and register-s contains the base address.

| INTRUCTION | OPCODE |

|------------|--------|

| Lw         | 1000   |

| Sw         | 1001   |

d. I/O-type (I/O) or input and output defined as: (1) read the I/O Unit (IOU) addressed by register-s and store data in destination register-t = IO(register-s), and (2) write register-t data to IOU at address register-s as IO(register-s) = register-t.

| INTRUCTION | OPCODE |

|------------|--------|

| In         | 1010   |

| Out        | 1011   |

The IOU is a read/write unit such as reading from keyboard and writing to CRT. The interface of the CPU with the IOU is similar to the interface to data memory, i.e., it is a box with input address, data-in and data-out and other control signals.

e. CB-type (CB): conditional branch (CB) using PC = PC+4+ Ext[Imm16]\*4 if condition is True or PC= PC+4 if Condition is False. The condition checked is whether register-s and register-t are either equal or not equal. Note that the ALU has a Zero flag (Z).

| INTRUCTION | OPCODE |

|------------|--------|

| BEQ        | 1100   |

| BNE        | 1101   |

f. J-type (Jump): Jump using  $PC = [(PC+4)_{31-28}, (Imm26), 00]$ , i.e. concatenation

| INTRUCTION | OPCODE |

|------------|--------|

| J          | 1110   |

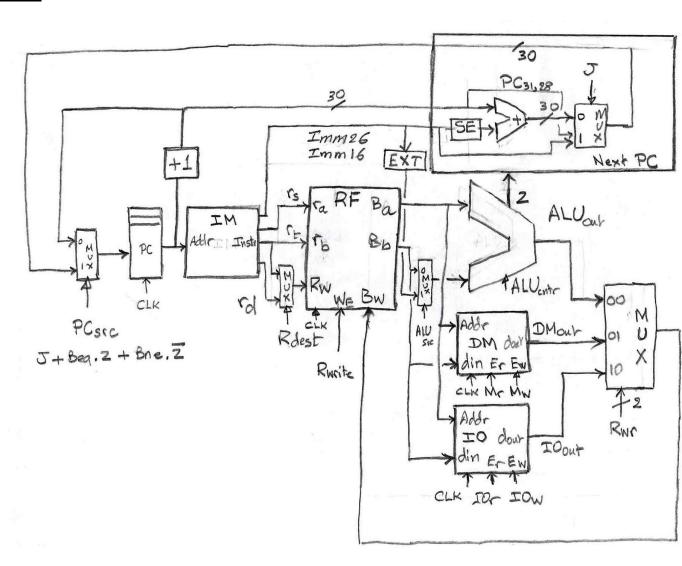

The objective of this question is to design a Single Cycle Datapath (SCD). Assume the availability of the following components: PC, IM, RF, ALU, I/O, and DM.

- 1. [16 points] Give the drawing of the SCD Design and answer each of the following questions:

- a. Show the needed components for SCD with controls, clocking (if any), and write enables (if any),

- b. Explain why a component may require clocking and/or write enable! When the write should take place and why!,

- c. Show all needed multiplexers and their controls,

- d. Show the PC with all possible target values.

### **Solution**

- a. The RF, DM, and IO must have Write Enable and be clocked because their write should take place at the end of the single cycle. (Directly or indirectly on the design: 4 points)

- b. In total we need 4 2-to-1 Muxes and one 4-to-1 Mux (same as above: 4 points).

- c. The PC values can be PC+4 (R, I-R, L/S, and Beq/Bne if not taken),

PC + E(Imm16) in the case of Beq/Bne if taken, or [PC31-28, Imm26,00] for the J.

Same as above + details of PCnext (4 points)

- d. Correct connectivity details (Addr, din, dout, WE, etc) of M and IO (4 points).

- e. Note: The above SCD arrangement may shorten the average execution time for R and IR types because the ALU, DM, and I/O are parallel. The exception is the L/S types, for which 2 instructions will be required instead of one if a base address is added to an offset. In some cases we may avoid the use of offset if we directly increment a register address.

2. [8 points] List in the following table all the controls needed for your SCD. Fill in the Table for all value of control corresponding to each listed instruction.

#### **Solution**

| Type | Instr. | <b>OPCODE</b> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | Rdest | Rwrite | Ext | ALUsrc | ALUop | Beq | Bne | J | Mrd | Mw<br>t | IOr<br>d | IOw<br>t | Rwr |

|------|--------|---------------------------------------------------------------------------|-------|--------|-----|--------|-------|-----|-----|---|-----|---------|----------|----------|-----|

| R    | Add    | 0000                                                                      | 1     | 1      | 1   | 0      | 00    | 0   | 0   | 0 | 0   | 0       | 0        | 0        | 00  |

|      | Sub    | 0001                                                                      | 1     | 1      | 1   | 0      | 01    | 0   | 0   | 0 | 0   | 0       | 0        | 0        | 00  |

|      | Or     | 0010                                                                      | 1     | 1      | 0   | 0      | 10    | 0   | 0   | 0 | 0   | 0       | 0        | 0        | 00  |

|      | And    | 0011                                                                      | 1     | 1      | 0   | 0      | 11    | 0   | 0   | 0 | 0   | 0       | 0        | 0        | 00  |

| I    | Addi   | 0100                                                                      | 0     | 1      | 1   | 1      | 00    | 0   | 0   | 0 | 0   | 0       | 0        | 0        | 00  |

|      | Subi   | 0101                                                                      | 0     | 1      | 1   | 1      | 01    | 0   | 0   | 0 | 0   | 0       | 0        | 0        | 00  |

|      | Ori    | 0110                                                                      | 0     | 1      | 0   | 1      | 10    | 0   | 0   | 0 | 0   | 0       | 0        | 0        | 00  |

|      | Andi   | 0111                                                                      | 0     | 1      | 0   | 1      | 11    | 0   | 0   | 0 | 0   | 0       | 0        | 0        | 00  |

| L/S  | Lw     | 1000                                                                      | 0     | 1      | X   | X      | XX    | 0   | 0   | 0 | 1   | 0       | 0        | 0        | 01  |

|      | Sw     | 1001                                                                      | X     | 0      | X   | X      | XX    | 0   | 0   | 0 | 0   | 1       | 0        | 0        | XX  |

| I/O  | In     | 1010                                                                      | 0     | 1      | X   | X      | XX    | 0   | 0   | 0 | 0   | 0       | 1        | 0        | 10  |

|      | Out    | 1011                                                                      | X     | 0      | X   | X      | XX    | 0   | 0   | 0 | 0   | 0       | 0        | 1        | XX  |

| СВ   | Beq    | 1100                                                                      | X     | 0      | X   | 0      | 01    | 1   | 0   | 0 | 0   | 0       | 0        | 0        | XX  |

|      | Bne    | 1101                                                                      | X     | 0      | X   | 0      | 01    | 0   | 1   | 0 | 0   | 0       | 0        | 0        | XX  |

| J    | J      | 1110                                                                      | X     | 0      | X   | X      | XX    | 0   | 0   | 1 | 0   | 0       | 0        | 0        | XX  |

Note: (1) Controls must appear on the design, (2) Beq, Bne, J, Mrd, Mw, IOr and IOw are given less weight, and (3) ALUop must be expressed as function of OPCODE.

3. [6 Points] Find the **simplest combinational logic function** for each of the SCD control as function of Opcode.

#### **Solution**

Rdest = x3'x2'

**Rwrite= X3'+ x3x2'x0'**

Ext = x3'x1'

ALUsrc = x2

$\mathbf{ALUop} = (\mathbf{x1}, \mathbf{x0} + \mathbf{x3x2})$

Beq =x3x2x1'x0'

Bne = x3x2x1'x0

J = x3x2x1x0,

Mrd = x3x2'x1'x0'

$\mathbf{Mwt} = \mathbf{x3x2'x1'x0}$

IOrd = x3x2'x1x0'

IOwt = x3x2'x1x0

Rwr = (x3x2'x1, x3x2'x1')

# **MIPS Instructions:**

| Instr | ruction          | R-Type Format      |        |           |           |           |        |          |

|-------|------------------|--------------------|--------|-----------|-----------|-----------|--------|----------|

| add   | \$s1, \$s2, \$s3 | \$s1 = \$s2 + \$s3 | op = 0 | rs = \$s2 | rt = \$s3 | rd = \$s1 | sa = 0 | f = 0x20 |

| addu  | \$s1, \$s2, \$s3 | \$s1 = \$s2 + \$s3 | op = 0 | rs = \$s2 | rt = \$s3 | rd = \$s1 | sa = 0 | f = 0x21 |

| sub   | \$s1, \$s2, \$s3 | \$s1 = \$s2 - \$s3 | op = 0 | rs = \$s2 | rt = \$s3 | rd = \$s1 | sa = 0 | f = 0x22 |

| subu  | \$s1, \$s2, \$s3 | \$s1 = \$s2 - \$s3 | op = 0 | rs = \$s2 | rt = \$s3 | rd = \$s1 | sa = 0 | f = 0x23 |

| Ins | truction         | Meaning             | R-Type Format |           |           |           |        |          |

|-----|------------------|---------------------|---------------|-----------|-----------|-----------|--------|----------|

| and | \$s1, \$s2, \$s3 | \$s1 = \$s2 & \$s3  | op = 0        | rs = \$s2 | rt = \$s3 | rd = \$s1 | sa = 0 | f = 0x24 |

| or  | \$s1, \$s2, \$s3 | \$s1 = \$s2   \$s3  | op = 0        | rs = \$s2 | rt = \$s3 | rd = \$s1 | sa = 0 | f = 0x25 |

| XOL | \$s1, \$s2, \$s3 | \$s1 = \$s2 ^ \$s3  | op = 0        | rs = \$s2 | rt = \$s3 | rd = \$s1 | sa = 0 | f = 0x26 |

| nor | \$s1, \$s2, \$s3 | \$s1 = ~(\$s2 \$s3) | op = 0        | rs = \$s2 | rt = \$s3 | rd = \$s1 | sa = 0 | f = 0x27 |

| Inst | ruction        | Meaning             | R-Type Format |           |           |           |         |       |

|------|----------------|---------------------|---------------|-----------|-----------|-----------|---------|-------|

| sll  | \$s1,\$s2,10   | \$s1 = \$s2 << 10   | op = 0        | rs = 0    | rt = \$s2 | rd = \$s1 | sa = 10 | f = 0 |

| srl  | \$s1,\$s2,10   | \$s1 = \$s2>>>10    | op = 0        | rs = 0    | rt = \$s2 | rd = \$s1 | sa = 10 | f = 2 |

| sra  | \$s1, \$s2, 10 | \$s1 = \$s2 >> 10   | op = 0        | rs = 0    | rt = \$s2 | rd = \$s1 | sa = 10 | f = 3 |

| sllv | \$s1,\$s2,\$s3 | \$s1 = \$s2 << \$s3 | op = 0        | rs = \$s3 | rt = \$s2 | rd = \$s1 | sa = 0  | f = 4 |

| srlv | \$s1,\$s2,\$s3 | \$s1 = \$s2>>>\$s3  | op = 0        | rs = \$s3 | rt = \$s2 | rd = \$s1 | sa = 0  | f = 6 |

| srav | \$s1,\$s2,\$s3 | \$s1 = \$s2 >> \$s3 | op = 0        | rs = \$s3 | rt = \$s2 | rd = \$s1 | sa = 0  | f = 7 |

| Instru | uction         | Meaning          | I-Type Format |           |           |                        |  |

|--------|----------------|------------------|---------------|-----------|-----------|------------------------|--|

| addi   | \$s1, \$s2, 10 | \$s1 = \$s2 + 10 | op = 0x8      | rs = \$s2 | rt = \$s1 | imm <sup>16</sup> = 10 |  |

| addiu  | \$s1, \$s2, 10 | \$s1 = \$s2 + 10 | op = 0x9      | rs = \$s2 | rt = \$s1 | imm <sup>16</sup> = 10 |  |

| andi   | \$s1, \$s2, 10 | \$s1 = \$s2 & 10 | op = 0xc      | rs = \$s2 | rt = \$s1 | imm <sup>16</sup> = 10 |  |

| ori    | \$s1, \$s2, 10 | \$s1 = \$s2   10 | op = 0xd      | rs = \$s2 | rt = \$s1 | imm <sup>16</sup> = 10 |  |

| xori   | \$s1, \$s2, 10 | \$s1 = \$s2 ^ 10 | op = 0xe      | rs = \$s2 | rt = \$s1 | imm <sup>16</sup> = 10 |  |

| lui    | \$s1, 10       | \$s1 = 10 << 16  | op = 0xf      | 0         | rt = \$s1 | imm <sup>16</sup> = 10 |  |

| Instruction |               | Meaning              | Format  |                   |                 | mat               |

|-------------|---------------|----------------------|---------|-------------------|-----------------|-------------------|

| j           | label         | jump to label        | op6 = 2 | imm <sup>26</sup> |                 |                   |

| beq         | rs, rt, label | branch if (rs == rt) | op6 = 4 | rs <sup>5</sup>   | rt <sup>5</sup> | imm <sup>16</sup> |

| bne         | rs, rt, label | branch if (rs != rt) | op6 = 5 | rs <sup>5</sup>   | rt <sup>5</sup> | imm <sup>16</sup> |

| blez        | rs, label     | branch if (rs<=0)    | op6 = 6 | rs <sup>5</sup>   | 0               | imm <sup>16</sup> |

| bgtz        | rs, label     | branch if (rs > 0)   | op6 = 7 | rs <sup>5</sup>   | 0               | imm <sup>16</sup> |

| bltz        | rs, label     | branch if (rs < 0)   | op6 = 1 | rs <sup>5</sup>   | 0               | imm <sup>16</sup> |

| bgez        | rs, label     | branch if (rs>=0)    | op6 = 1 | rs <sup>5</sup>   | 1               | imm <sup>16</sup> |

| Instr | ruction                   | Meaning                                                                                                                                        | Format  |                 |                 |                   |   |      |

|-------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|-----------------|-------------------|---|------|

| slt   | rd, rs, rt                | rd=(rs <rt?1:0)< td=""><td>op6 = 0</td><td>rs<sup>5</sup></td><td>rt<sup>5</sup></td><td>rd<sup>5</sup></td><td>0</td><td>0x2a</td></rt?1:0)<> | op6 = 0 | rs <sup>5</sup> | rt <sup>5</sup> | rd <sup>5</sup>   | 0 | 0x2a |

| sltu  | rd, rs, rt                | rd=(rs <rt?1:0)< td=""><td>op6 = 0</td><td>rs<sup>5</sup></td><td>rt<sup>5</sup></td><td>rd<sup>5</sup></td><td>0</td><td>0x2b</td></rt?1:0)<> | op6 = 0 | rs <sup>5</sup> | rt <sup>5</sup> | rd <sup>5</sup>   | 0 | 0x2b |

| slti  | rt, rs, imm <sup>16</sup> | rt=(rs <imm?1:0)< td=""><td>0xa</td><td>rs<sup>5</sup></td><td>rt<sup>5</sup></td><td colspan="2">imm<sup>16</sup></td><td>16</td></imm?1:0)<> | 0xa     | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |   | 16   |

| sltiu | rt, rs, imm <sup>16</sup> | rt=(rs <imm?1:0)< td=""><td>0xb</td><td>rs<sup>5</sup></td><td>rt<sup>5</sup></td><td colspan="2">imm<sup>16</sup></td><td>16</td></imm?1:0)<> | 0xb     | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |   | 16   |

| Instruction |                            | Meaning                         | I-Type Format |                 |                 |                   |  |

|-------------|----------------------------|---------------------------------|---------------|-----------------|-----------------|-------------------|--|

| lb          | rt, imm <sup>16</sup> (rs) | rt = MEM[rs+imm <sup>16</sup> ] | 0x20          | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |  |

| lh          | rt, imm <sup>16</sup> (rs) | rt = MEM[rs+imm <sup>16</sup> ] | 0x21          | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |  |

| lw          | rt, imm <sup>16</sup> (rs) | rt = MEM[rs+imm <sup>16</sup> ] | 0x23          | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |  |

| lbu         | rt, imm <sup>16</sup> (rs) | rt = MEM[rs+imm <sup>16</sup> ] | 0x24          | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |  |

| lhu         | rt, imm <sup>16</sup> (rs) | rt = MEM[rs+imm <sup>16</sup> ] | 0x25          | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |  |

| sb          | rt, imm <sup>16</sup> (rs) | MEM[rs+imm <sup>16</sup> ] = rt | 0x28          | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |  |

| sh          | rt, imm <sup>16</sup> (rs) | MEM[rs+imm <sup>16</sup> ] = rt | 0x29          | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |  |

| sw          | rt, imm <sup>16</sup> (rs) | MEM[rs+imm <sup>16</sup> ] = rt | 0x2b          | rs <sup>5</sup> | rt <sup>5</sup> | imm <sup>16</sup> |  |

| Insti | ruction | Meaning         | Format  |                         |   |                 |   |   |

|-------|---------|-----------------|---------|-------------------------|---|-----------------|---|---|

| jal   | label   | \$31=PC+4, jump | op6 = 3 | imm <sup>26</sup>       |   |                 |   |   |

| jr    | Rs      | PC = Rs         | op6 = 0 | rs <sup>5</sup> 0 0 0 8 |   |                 |   | 8 |

| jalr  | Rd, Rs  | Rd=PC+4, PC=Rs  | op6 = 0 | rs <sup>5</sup>         | 0 | rd <sup>5</sup> | 0 | 9 |

| Instruction    | Format                  |         |                 |     |                 |   |      |

|----------------|-------------------------|---------|-----------------|-----|-----------------|---|------|

| mult Rs, Rt    | Hi, Lo = $Rs \times Rt$ | op6 = 0 | Rs <sup>5</sup> | Rt⁵ | 0               | 0 | 0x18 |

| multu Rs, Rt   | Hi, Lo = $Rs \times Rt$ | op6 = 0 | Rs <sup>5</sup> | Rt⁵ | 0               | 0 | 0x19 |

| mul Rd, Rs, Rt | $Rd = Rs \times Rt$     | 0x1c    | Rs <sup>5</sup> | Rt⁵ | Rd⁵             | 0 | 0x02 |

| div Rs, Rt     | Hi, Lo = $Rs / Rt$      | op6 = 0 | Rs <sup>5</sup> | Rt⁵ | 0               | 0 | 0x1a |

| divu Rs, Rt    | Hi, Lo = Rs / Rt        | op6 = 0 | Rs <sup>5</sup> | Rt⁵ | 0               | 0 | 0x1b |

| mfhi Rd        | Rd = Hi                 | op6 = 0 | 0               | 0   | Rd <sup>5</sup> | 0 | 0x10 |

| mflo Rd        | Rd = Lo                 | op6 = 0 | 0               | 0   | Rd <sup>5</sup> | 0 | 0x12 |