King Fahd University of Petroleum and Minerals College of Computer Science and Engineering Computer Engineering Department

## COE 301 COMPUTER ORGANIZATION ICS 233: COMPUTER ARCHITECTURE & ASSEMBLY LANGUAGE Term 151 (Fall 2015-2016) Final Exam Sunday Dec. 20, 2015 8:00-11:00 AM

### Time: 180 minutes, Total Pages: 14

| Name: | ID: | Section: |

|-------|-----|----------|

|       |     |          |

#### Notes:

- Do not open the exam book until instructed

- Answer all questions

- All steps must be shown

- Any assumptions made must be clearly stated

- Mobile phones must be switched off

| Question | Max Points | Score |

|----------|------------|-------|

| Q1       | 15         |       |

| Q2       | 18         |       |

| Q3       | 13         |       |

| Q4       | 17         |       |

| Q5       | 12         |       |

| Total    | 75         |       |

Dr. Aiman El-Maleh Dr. Mayez Al-Muhammad

### [15 Points]

(Q1)

(i) We wish to compare the performance of two different computers: M1 and M2. The following measurements have been made for running a program (Program 1) on these computers:

| Program 1              | M1                | M2              |

|------------------------|-------------------|-----------------|

| #Instructions Executed | $5 \times 10^{9}$ | $6 \times 10^9$ |

| СРІ                    | 1.2               | 1.25            |

| Clock Rate             | 3 GHZ             | 5 GHZ           |

a. Which computer is faster for running the program and by how much?

(3 points)

b. Suppose the execution time of a second program (Program 2) on both computers is given below.

| Program 2             | M1          | M2           |  |

|-----------------------|-------------|--------------|--|

| <b>Execution</b> Time | 5.0 seconds | 10.0 seconds |  |

Suppose that program 1 must be executed 1600 times each hour. Any remaining time should be used to run program 2. Which computer is faster for this workload? Performance is measured here by the throughput of program 2.

(4 points)

(ii) Consider two different implementations, M1 and M2, of the same instruction set. There are three classes of instructions (A, B, and C) in the instruction set. M1 has a clock rate of 6 GHz and M2 has a clock rate of 3 GHz. The CPI for each instruction class on M1 and M2 is given in the following table:

| Class | CPI on M1 | CPI on M2 | C1 Usage | C2 Usage |

|-------|-----------|-----------|----------|----------|

| А     | 2         | 1         | 40%      | 60%      |

| В     | 3         | 2         | 40%      | 15%      |

| С     | 5         | 2         | 20%      | 25%      |

The above table also contains a summary of the usage of instruction classes generate by two different compilers: C1 and C2. Assume that each compiler generates the same number of instructions for a given program. Which computer and compiler combination give the best performance? (5 points)

(iii) A benchmark program runs for 200 seconds. We want to improve the execution time of the benchmark by a factor of 2.5. We enhance the floating-point unit to make the floating-point instructions run 4 times faster. How much of the initial execution time would floating-point instructions have to account for to show an overall speedup of 2.5 on this benchmark?

(3 points)

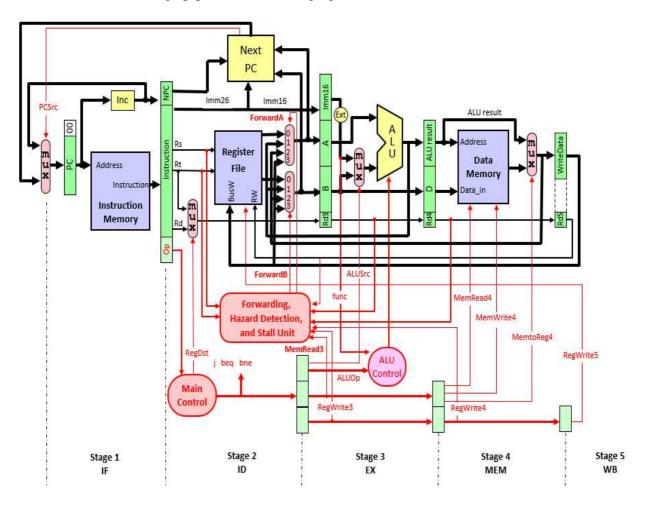

# (Q2) Consider the 5-stage pipelined CPU design given below:

(i) Show the control signals that will be used for stalling the pipeline due to data hazards along with their conditions. Add the necessary changes to the design, on the given diagram, to allow it to handle data hazards. (5 points)

(ii) Consider the instruction sequence given below:

lw \$t1, (\$s0) sw \$t1, (\$s1)

We can forward that data of **lw** instruction to the next **sw** instruction as required by the above example. However, such forwarding is not supported by the given 5-stage pipeline CPU design.

- a. Show the required changes in the datapath and forwarding unit to support such forwarding.

- b. Write the condition for generating the forwarding control signal. Identify the pipeline registers and control signals used by the **sw** and **lw** instructions when writing the condition.

(6 points)

(iii) Consider the following MIPS assembly language code: (7 Points)

| 11 <b>:</b> | ADDI | \$s0, | \$0, 10    |

|-------------|------|-------|------------|

| 12:         | ADD  | \$s0, | \$s0, \$s0 |

| I3:         | SLL  | \$s0, | \$s0, 4    |

| <b>I4:</b>  | LW   | \$s1, | 4(\$s0)    |

| 15:         | ADDI | \$s2, | \$s1, -1   |

| I6:         | SW   | \$s2, | 4(\$s0)    |

Complete the following table showing the timing of the above code on the 5-stage pipeline given in part (i) (IF, ID, EX, MEM, WB) assuming that it supports **forwarding** and **pipeline stall**. Draw an arrow showing forwarding between the stage that provides the data and the stage that receives the data. Show all stall cycles (draw an X in the box to represent a stall cycle). Determine the number of clock cycles to execute this code.

|          | 1  | 2  | 3  | 4 | 5  | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|----------|----|----|----|---|----|---|---|---|---|----|----|----|----|----|----|

| I1: ADDI | IF | ID | EX | - | WB |   |   |   |   |    |    |    |    |    |    |

| I2: ADD  |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |

| I3: SLL  |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |

| I4: LW   |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |

| I5: ADDI |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |

| I6: SW   |    |    |    |   |    |   |   |   |   |    |    |    |    |    |    |

### (Q3)

- (i) Fill in the blanks in each of the following questions: (8 points)

- 1. The Direct Mapped Cache organization leads to a \_\_\_\_\_\_ access time but lacks \_\_\_\_\_\_ in block placement compared to fully associative mapping.

- 2. The Fully Associative Cache organization leads to a \_\_\_\_\_\_ access time due to the multiplexer used but has a lot of \_\_\_\_\_\_ in block placement.

- 3. Access time of a \_\_\_\_\_ Cache \_\_\_\_\_ with the set size.

- 4. With the Write Through policy, every write to cache is propagated to DRAM, which makes DRAM data always \_\_\_\_\_\_ with the cached data. A Write Through cache may not use a \_\_\_\_\_\_ policy.

- With the Write Back policy, multiple writes to a block accumulate in the cache, but the block will be written back to DRAM if it has been \_\_\_\_\_.

A Write Back cache must use a \_\_\_\_\_ policy.

- 6. In a 4-way set-associative cache with 64 Kbyte data capacity (i.e. not counting tag and other bits), and with a 64 byte block size, the number of bits used for the offset is \_\_\_\_\_\_ and the number of bits for the index is

\_\_\_\_\_.

7. In a \_\_\_\_\_\_ replacement policy, one counter is used per set to replace the \_\_\_\_\_\_ block.

Page 8 of 14

```

(ii) (5 points)

```

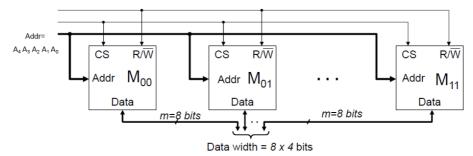

1. A memory system consists of memory modules  $M_{00}$ ,  $M_{01}$ ,  $M_{10}$  and  $M_{11}$  which are interconnected using the below drawing, where the address is 5-bit  $A_4 A_3 A_2 A_1 A_0$ .

Assume two 32-bit data to be written in the above memory system at the corresponding addresses as shown in the table below:

| Address $A_4 A_3 A_2 A_1 A_0$ | 01010    | 10100    |

|-------------------------------|----------|----------|

| Data Values (Hex)             | 4326016A | A3414640 |

Fill in the table below to show where the above data values for the given addresses will be written in the above memories:

| $A_4 A_3 A_2 A_1 A_0$ | $M_{00}$ | $M_{01}$ | M <sub>10</sub> | M <sub>11</sub> |

|-----------------------|----------|----------|-----------------|-----------------|

|                       |          |          |                 |                 |

|                       |          |          |                 |                 |

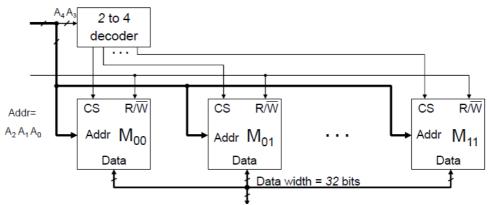

2. Now the four memory modules  $M_{00}$ ,  $M_{01}$ ,  $M_{10}$  and  $M_{11}$  are interconnected using the below drawing:

Assume three 32-bit data to be written in the above memory system at the corresponding addresses as shown in the table below:

| Address $A_4 A_3 A_2 A_1 A_0$ | 01010    | 10100    | 11000    |

|-------------------------------|----------|----------|----------|

| Data Values (Hex)             | 4326016A | A3414640 | FEF12306 |

Fill in the table below to show where the data values for the given addresses will be stored in the memories:

| $A_4 A_3 A_2 A_1 A_0$ | $M_{00}$ | $M_{01}$ | $M_{10}$ | M <sub>11</sub> |

|-----------------------|----------|----------|----------|-----------------|

|                       |          |          |          |                 |

|                       |          |          |          |                 |

|                       |          |          |          |                 |

(Q4) A 4 GHz CPU uses a unified cache memory (Both IC and DC) with the following specs:

- 1. The cache hit time is 2 ns.

- 2. The cache hit probability is 0.93

- 3. The main memory access is 30 ns.

- 4. The CPI=2 clocks when instruction fetch and data fetch results in hits.

- 5. The probability of load/store instructions P(L/S) = 0.25

Answer each of the following questions:

- (i) How many clocks there are in one DRAM access time? (1 point)

- (ii) Evaluate the Average Memory Access Time (AMAT), the average number of stalls per access (stalls/access), average number of stalls per instruction (stalls/ins) and the CPI. (4 points)

(iii) Suppose the CPU is enhanced by increasing its clock rate to 5 GHz. Evaluate the speedup of the enhanced CPU compared to the original CPU. (4 points)

.

(iv) Suppose the CPU uses a Write-Through policy with a write buffer. The write buffer access time is 10 ns but the probability to be found free is 0.75 and it takes 15ns to free one buffer slot if found full. Assume that when the buffer is full, it will be written after a slot is made free. Evaluate the AMAT for data accesses only. Assume that the probability of load and store instructions is the same. (4 points)

(v) Suppose we use a split cache with IC and DC having:

- 1. IC: 1 ns access time and 0.95 hit probability,

- 2. DC: 2 ns access times and 0.91 hit probability.

The main memory is the same as above. Evaluate the AMAT(IC) and AMAT(DC) and the CPU AMAT. (4 points)

### (Q5)

### (i) (9 points)

A sequence of four branches are shown in the first column of the Table below with their respective PC value, branch target address, and next PC. These braches are executed in four passes (pass 1 to 4). The actual branch outcomes of each branch in each pass are shown in columns 2, 3, 4 and 5, respectively, where T represents a taken branch and NT represents a not taken branch. Assume a Branch Target Buffer (BTB) is used for early prediction of taken branches.

| Four Bra | nches with their respective | Branch outcomes in four passes |           |           |           |  |  |

|----------|-----------------------------|--------------------------------|-----------|-----------|-----------|--|--|

|          | s, branch target address,   | Actual                         | Actual    | Actual    | Actual    |  |  |

| and next | -                           | Branch                         | Branch    | Branch    | Branch    |  |  |

|          |                             | outcome                        | outcome   | outcome   | outcome   |  |  |

|          |                             | In pass 1                      | In pass 2 | In pass 3 | In pass 4 |  |  |

| 00010    | Beq -,-, (target=00100)     | NT                             | Т         | NT        | NT        |  |  |

| 00011    |                             |                                |           |           |           |  |  |

|          |                             |                                |           |           |           |  |  |

| 00101    | Beq -,-, (target=00111)     | Т                              | Т         | NT        | Т         |  |  |

| 00110    |                             |                                |           |           |           |  |  |

|          |                             |                                |           |           |           |  |  |

| 01000    | Beq -,-, (target=10010)     | NT                             | Т         | Т         | NT        |  |  |

| 01001    |                             |                                |           |           |           |  |  |

|          |                             |                                |           |           |           |  |  |

| 01011    | Beq -,-, (target=01101)     | Т                              | NT        | NT        | Т         |  |  |

| 01100    |                             |                                |           |           |           |  |  |

1. Fill in the BTB entries for PC, target and initial prediction (T for all) for the above four branches. Fill in the prediction in BTB table following each pass (1 to 4) by assuming a 1-bit prediction. (2 points)

| BTB |        |         | BTB Prediction just after pass k ( $k$ = 1 to 4) |        |        |            |  |

|-----|--------|---------|--------------------------------------------------|--------|--------|------------|--|

| PC  | Target |         | Prediction                                       |        |        | Prediction |  |

|     |        | initial | pass 1                                           | pass 2 | pass 3 | pass 4     |  |

|     |        |         |                                                  |        |        |            |  |

|     |        |         |                                                  |        |        |            |  |

|     |        |         |                                                  |        |        |            |  |

|     |        |         |                                                  |        |        |            |  |

|     |        |         |                                                  |        |        |            |  |

|     |        |         |                                                  |        |        |            |  |

|     |        |         |                                                  |        |        |            |  |

|     |        |         |                                                  |        |        |            |  |

2. Repeat the above question by predicting the branch outcome using a 2-bit saturating counter (given below). Denote by NT1 and T1 the weak NT and weak T, respectively. Assume initial prediction of strong predict taken. (2 points)

| BTB |        |                    | BTB Prediction just after pass k (1 to 4) |                   |                   |                      |  |

|-----|--------|--------------------|-------------------------------------------|-------------------|-------------------|----------------------|--|

| PC  | Target | Prediction initial | Prediction pass 1                         | Prediction pass 2 | Prediction pass 3 | Prediction<br>pass 4 |  |

|     |        |                    |                                           |                   |                   |                      |  |

|     |        |                    |                                           |                   |                   |                      |  |

|     |        |                    |                                           |                   |                   |                      |  |

|     |        |                    |                                           |                   |                   |                      |  |

Answer the following questions:

- a. Using all the above branches, evaluate the probability of correct prediction (Pcorrect). (2 points)

- b. Assume that each miss-prediction incurs 2 stalls to the CPU and the probability an instruction to be branch is 0.18. Assume the CPI =2 when all the predictions are correct. Evaluate the CPI based on the above four passes. (3 points)

```

(3 points)

(ii)

A loop can take one of the following two constructs:

Repeat:

...

...

• • •

• • •

Beq -,-, Repeat

or

Repeat:

Beq -,-, Exit

...

•••

...

J Repeat

Exit:

```

Prove that a 2-bit history prediction is always better than a 1-bit history prediction when the above loop (either of its constructs) is executed many times and its entry is maintained in BTB.

# BLANK PAGE