#### EE200 DIGITAL LOGIC CIRCUIT DESIGN

The material covered in this lecture will be as follows:

- Binary counter with parallel load.

- Design of counters with unused states.

- Ring counter.

- Johnson counter.

### After finishing this lecture, you should be able to:

- ⇒ Understand the flexibility of using counters with parallel load to implement modulus-N counters.

- ⇒ Understand the principle of operation of ring counters.

- ⇒ Understand the principle of operation of Johnson counter.

# Binary counter with parallel load

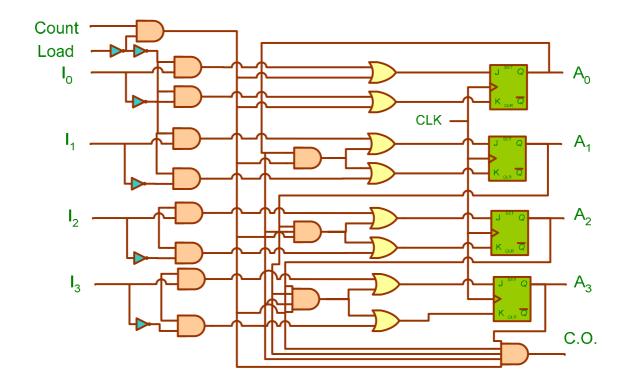

Parallel load capability is used for transmission of an initial binary number into the counter prior to the count operation. The logic diagram of a 4-bit register with parallel load, which can be used as a counter. When the input load is one, it disables the count operation and allows the transfer of the data inputs into the flipflops. If the count and load inputs are both zero, then the outputs will not change. Only when the count is one and the load is zero, then the register will act as a counter and starts counting from the last output. The function table of this counter with parallel load is shown, followed by the logic diagram.

The function table for the counter shown above is as follows:

| Clear | Clock    | Load | Count | Function   |

|-------|----------|------|-------|------------|

| 0     | X        | X    | X     | Clear      |

| 1     | <b>↑</b> | 1    | Х     | Load I's   |

| 1     | <b>↑</b> | 0    | 1     | Count next |

| 1     | <b>↑</b> | 0    | 0     | No change  |

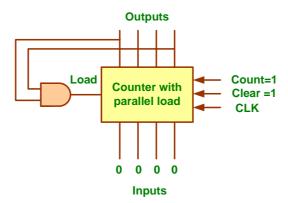

A counter with parallel load can be used to generate any desired count sequence. In the first example, the counter is used to generate the BCD count sequence by using the load input to load four zeros after reaching 1001. In the second example, the clear input is used to clear the counter after detecting that the count passed 1001 and attempts to go to 1010.

BCD counter , using the counter with parallel load and the load input:

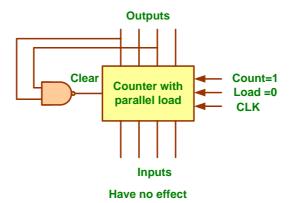

The second example is fro the BCD counter using the counter with parallel load. This time the clear input is used instead of the load input.

# **Design of Counters with Unused States**

When we design a counter with modulus m such that  $m < 2^N$ , where N is the number of flip-flops, then some states will be

unused. The unused states can be treated as don't care conditions. After completing the design, we must test to see that the counter is self correcting and goes back to one of the used states after being in an unused state.

Design of a modulus-6 counter using JK flip-flops

The count cycle of this counter is 0, 1, 2, 4, 5, 6. The state table for this counter together with the required flip-flop inputs is given in the following table:

| P.S. |   |   | N.S. |   | Flip-Flop Inputs |       |       |         |         |         |                       |

|------|---|---|------|---|------------------|-------|-------|---------|---------|---------|-----------------------|

| Α    | В | С | Α    | В | С                | $J_A$ | $K_A$ | $J_{B}$ | $K_{B}$ | $J_{C}$ | <b>K</b> <sub>C</sub> |

| 0    | 0 | 0 | 0    | 0 | 1                | 0     | Χ     | 0       | Χ       | 1       | Χ                     |

| 0    | 0 | 1 | 0    | 1 | 0                | 0     | Χ     | 1       | X       | Χ       | 1                     |

| 0    | 1 | 0 | 1    | 0 | 0                | 1     | Χ     | Χ       | 1       | 0       | Χ                     |

| 1    | 0 | 0 | 1    | 0 | 1                | Χ     | 0     | 0       | Χ       | 1       | Χ                     |

| 1    | 0 | 1 | 1    | 1 | 0                | Χ     | 0     | 1       | Χ       | Χ       | 1                     |

| 1    | 1 | 0 | 0    | 0 | 0                | Χ     | 1     | Χ       | 1       | 0       | Χ                     |

The two states 011 and 111 are not used and can be considered as don't care when simplifying the flip-flop inputs. This will result in the following simplified input functions:

$$J_A = B$$

$K_A = B$   $J_B = C$   $K_B = 1$   $K_C = 1$

The logic diagram of the counter is shown next. We also have to determine the next state to any of the unused states. This will determine whether the design is successful or not. A successful design means that the next state to unused one is a used state after a limited number of clock pulses.

To check if the design is self correcting or not, we have to start from the unused state e.g. ABC  $\rightarrow$  011 and find the next state when a clock pulse is applied. B=1 will make A toggle (because JA=KA=B). Similarly, C=1 will make B toggle (because JB=C and KB=1). Finally B'=0 will cause no change in C (because JC=B'=0 and KC=1). This results in the next state of ABC  $\rightarrow$  100.

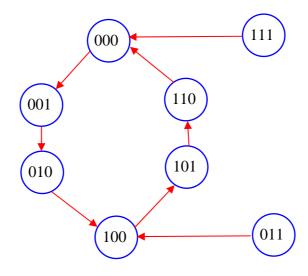

In a similar way we can find the next state to the second unused state 111 which will be 000. The complete state diagram, showing the transitions from the unused states, is shown next.

State Diagram of the modulus-6 counter

## **Ring Counter**

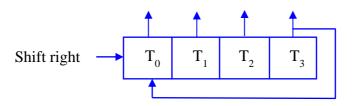

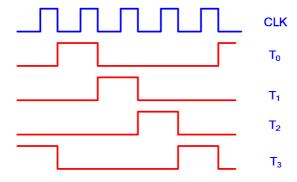

Ring counter is useful in generating the timing signals that control the sequence of operations in a digital system. A ring counter is a circular shift register with only one flip-flop set at any particular time while all the others are cleared. The single bit is shifted from one flip-flop to the next to produce the sequence of timing signals. This is demonstrated by the 4-bit shift register connected as a ring counter. The generated timing signals are also shown.

# Sequence of the four timing signals

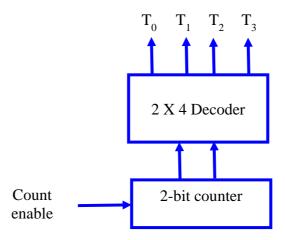

The ring counter can also be implemented with a counter and a decoder. The 4-bit ring counter needs a 2-bit counter and a 2X4 decoder. This is illustrated in the following block diagram.

#### **Johnson Counter**

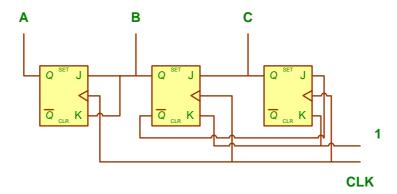

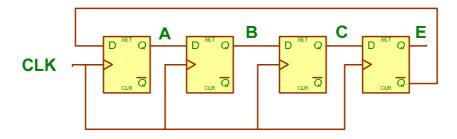

The number of timing signals can be doubled if the shift register is connected as a switch-tail ring counter. This is a circular shift register with the complement output of the last flip-flop connected to the input of the first flip-flop. The register shifts its contents once to the right with every clock pulse and at the same time, the complement value of the last flip-flop is transferred into the first flip-flop. Starting from a cleared state, this switch-tail counter goes through a sequence of eight states (2k) as listed in the accompanying table.

# The count sequence and required decoding are as follows:

| Sequence |   | AND gate required |   |   |          |  |

|----------|---|-------------------|---|---|----------|--|

| No.      | Α | В                 | С | E | required |  |

| 1        | 0 | 0                 | 0 | 0 | A'E'     |  |

| 2        | 1 | 0                 | 0 | 0 | AB'      |  |

| 3        | 1 | 1                 | 0 | 0 | BC'      |  |

| 4        | 1 | 1                 | 1 | 0 | CE'      |  |

| 5        | 1 | 1                 | 1 | 1 | AE       |  |

| 6        | 0 | 1                 | 1 | 1 | A'B      |  |

| 7        | 0 | 0                 | 1 | 1 | B'C      |  |

| 8        | 0 | 0                 | 0 | 1 | C'E      |  |