#### **EE200 DIGITAL LOGIC CIRCUIT DESIGN**

The material covered in this class will be as follows:

- ⇒Combinational circuits.

- ⇒Analysis procedure.

- ⇒Design procedure.

- ⇒Code conversion example.

#### **Combinational Circuits**

Logic circuits are either combinational or sequential. Combinational logic circuits consists of logic gates whose outputs at any time are determined from the present combination of the inputs. Sequential circuits consist of memory elements and logic gates.

A block Diagram of Combinational Circuit

# **Analysis Procedure**

1. Obtain Boolean expression from logic diagram

- a. Label all gate outputs that are a function of input variables. Obtain Boolean function for each gate.

- b. Label all gate outputs that are a function of input variables and previously labeled gates. Obtain Boolean function for each of these gates.

- c. Repeat step (b) until the outputs of the circuit are obtained.

# 2. Obtain the truth table from the logic diagram

- a. Prepare the truth table for n input variables and 2n input combinations.

- b. Label all gate outputs that are a function of input variables. Fill in the truth table for these outputs.

- c. Label all gate outputs that are functions of input variables and previously labeled gates. Fill in the truth table columns for these outputs.

- d. Repeat step (c) until the columns for all the outputs are obtained.

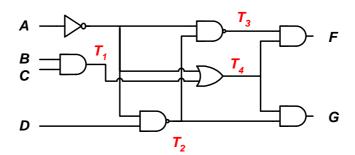

Example 1: Determine the Boolean functions for the outputs F and G as a function of the four inputs A, B, C, and D.

$$T_1 = BC$$

$$T_2 = (A'D)' = A + D'$$

$$T_{3} = (A'T_{2})' = A + T'_{2} = A + A'D = A + D$$

$$T_{4} = A' + T_{1} = A' + BC$$

$$F = T_{3}T_{4} = (A + D)(A' + BC) = AA' + ABC + A'D + BCD$$

$$= ABC + A'D + BCD = ABC + A'D$$

$$G = T_{2}T_{4} = (A + D')(A' + BC) = AA' + ABC + A'D' + BCD'$$

$$= ABC + A'D' + BCD' = ABC + A'D'$$

Example 2: Analyze the previous logic circuit by establishing the truth table for F and G.

| Inputs           |   |   |   |       |       |           |       | Outputs |   |

|------------------|---|---|---|-------|-------|-----------|-------|---------|---|

| $\boldsymbol{A}$ | В | C | D | $T_1$ | $T_2$ | <i>T3</i> | $T_4$ | F       | G |

| 0                | 0 | 0 | 0 | 0     | 1     | 0         | 1     | 0       | 1 |

| 0                | 0 | 0 | 1 | 0     | 0     | 1         | 1     | 1       | 0 |

| 0                | 0 | 1 | 0 | 0     | 1     | 0         | 1     | 0       | 1 |

| 0                | 0 | 1 | 1 | 0     | 0     | 1         | 1     | 1       | 0 |

| 0                | 1 | 0 | 0 | 0     | 1     | 0         | 1     | 0       | 1 |

| 0                | 1 | 0 | 1 | 0     | 0     | 1         | 1     | 1       | 0 |

| 0                | 1 | 1 | 0 | 1     | 1     | 0         | 1     | 0       | 1 |

| 0                | 1 | 1 | 1 | 1     | 0     | 1         | 1     | 1       | 0 |

| 1                | 0 | 0 | 0 | 0     | 1     | 1         | 0     | 0       | 0 |

| 1                | 0 | 0 | 1 | 0     | 1     | 1         | 0     | 0       | 0 |

| 1                | 0 | 1 | 0 | 0     | 1     | 1         | 0     | 0       | 0 |

| 1                | 0 | 1 | 1 | 0     | 1     | 1         | 0     | 0       | 0 |

| 1                | 1 | 0 | 0 | 0     | 1     | 1         | 0     | 0       | 0 |

| 1                | 1 | 0 | 1 | 0     | 1     | 1         | 0     | 0       | 0 |

| 1                | 1 | 1 | 0 | 1     | 1     | 1         | 1     | 1       | 1 |

| 1                | 1 | 1 | 1 | 1     | 1     | 1         | 1     | 1       | 1 |

### **Design Procedure**

- 1. Describe the problem (i.e., the problem statement).

- 2. Determine the available number of input variables and required output variables.

- 3. Assign letter symbols to the input and output variables.

- 4. Derive the truth table that defines the required relationships between inputs and outputs.

- 5. Obtain the simplified Boolean function for each output.

- 6. Draw the logic diagram.

# **Design of a Code Converter**

Design a combinational logic circuit that will convert from a BCD code to Excess-3 code.

Design

$$\rightarrow$$

4 inputs  $\rightarrow$  A, B, C, and C

4 outputs

$$\rightarrow$$

w, x, y, and z

#### **Truth Table:**

| Inpi | uts (Bo | CD Co | ode) | Outputs(Excess-3) |   |   |   |  |

|------|---------|-------|------|-------------------|---|---|---|--|

| A    | В       | C     | D    | W                 | x | y | z |  |

| 0    | 0       | 0     | 0    | 0                 | 0 | 1 | 1 |  |

| 0    | 0       | 0     | 1    | 0                 | 1 | 0 | 0 |  |

| 0    | 0       | 1     | 0    | 0                 | 1 | 0 | 1 |  |

| 0    | 0       | 1     | 1    | 0                 | 1 | 1 | 0 |  |

| 0    | 1       | 0     | 0    | 0                 | 1 | 1 | 1 |  |

| 0    | 1       | 0     | 1    | 1                 | 0 | 0 | 0 |  |

| 0    | 1       | 1     | 0    | 1                 | 0 | 0 | 1 |  |

| 0    | 1       | 1     | 1    | 1                 | 0 | 1 | 0 |  |

| 1    | 0       | 0     | 0    | 1                 | 0 | 1 | 1 |  |

| 1    | 0       | 0     | 1    | 1                 | 1 | 0 | 0 |  |

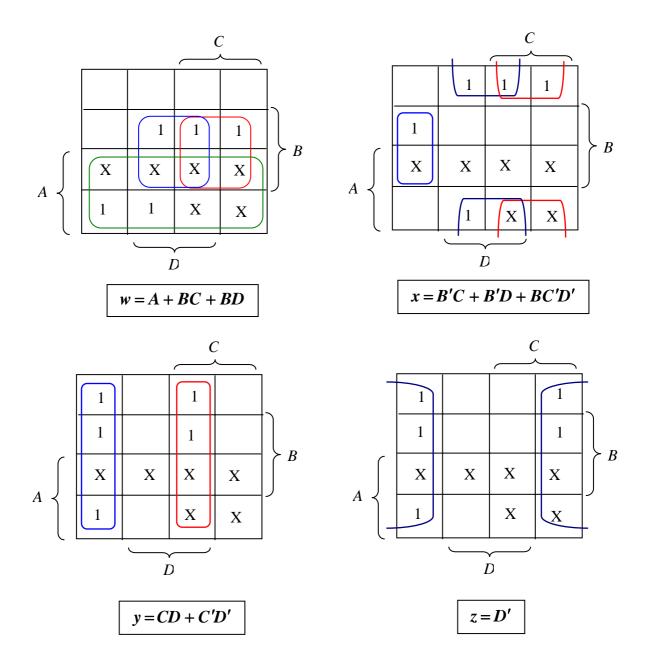

The six unused combinations are considered don't care conditions. These correspond to 10, 11, 12, 13, 14, and 15.

Simplification of the output functions is made using Karnaugh maps and making use of the don't care conditions.

A two level logic diagram can be obtained directly from the logic expressions. Also the logic expressions may be arranged such that:

$$z = D'$$

$y = CD + (C + D)'$   $x = B'(C + D) + B(C + D)'$

$w = A + B(C + D)$