#### **EE200 DIGITAL LOGIC CIRCUIT DESIGN**

The material covered in this class will be as follows:

- ⇒Digital logic gates

- ⇒Extension to multiple inputs

- ⇒Positive and negative logic

- ⇒Integrated circuits

# **Digital Logic Gates**

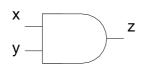

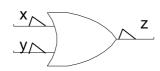

Commonly used digital logic gates are given in the following table.

| Name     | Graphic Symbol | Algebraic<br>Function | Truth Table                                                                                                                     |

|----------|----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| AND      | <i>x</i> F     | F = xy                | $ \begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 0 \\ \hline 0 & 1 & 0 \\ \hline 1 & 0 & 0 \\ \hline 1 & 1 & 1 \end{array} $ |

| OR       | <i>x</i>       | F=x+y                 | $\begin{array}{c cccc} xy & F \\ \hline 00 & 0 \\ \hline 01 & 1 \\ \hline 10 & 1 \\ \hline 11 & 1 \\ \end{array}$               |

| Inverter | $rac{1}{x}$    | F = x'                | $\begin{array}{c c c} x & F \\ \hline 0 & 1 \\ 1 & 0 \end{array}$                                                               |

| Buffer   | $rac{1}{x}$    | F = x                 | $\begin{array}{c cc} x & F \\ \hline 0 & 0 \\ \hline 1 & 1 \end{array}$                                                         |

| NAND | <i>x</i> | F = (xy)'     | $ \begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 1 \\ \hline 0 & 1 & 1 \\ \hline 1 & 0 & 1 \\ \hline 1 & 1 & 0 \end{array} $ |

|------|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------|

| NOR  | x<br>y   | F=(x+y)'      | $ \begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 1 \\ \hline 0 & 1 & 0 \\ \hline 1 & 0 & 0 \\ \hline 1 & 1 & 0 \end{array} $ |

| XOR  | x<br>y   | F = xy' + x'y | $ \begin{array}{c cccc} x y & F \\ \hline 0 0 & 0 \\ \hline 0 1 & 1 \\ \hline 1 0 & 1 \\ \hline 1 1 & 0 \end{array} $           |

| XNOR | x<br>y   | F = xy + x'y' | $ \begin{array}{c cccc} x & y & F \\ \hline 0 & 0 & 1 \\ \hline 0 & 1 & 0 \\ \hline 1 & 0 & 0 \\ \hline 1 & 1 & 1 \end{array} $ |

#### **Extension to Multiple Inputs**

The commonly used gates, except the buffer and the inverter, can be extended to have more than two inputs if the binary operation is commutative and associative (e.g. AND, OR).

NAND and NOR are commutative but not associative

$$\left[\left(x+y\right)'+z\right]'\neq\left[x+\left(y+z\right)'\right]'.$$

We define the multiple NOR and NAND gate as a complemented OR or AND gate.

e.g. three variable NOR gate  $\rightarrow$  (x + y + z)'.

### **Integrated Circuits**

Integrated circuits are classified based on the levels of integration.

SSI < 10 gates

MSI 10 – 100 gates (e.g., decoders, adders, MUXs)

LSI 100 – few 1000s (e.g., processors, memory chips)

**VLSI > 1000s**

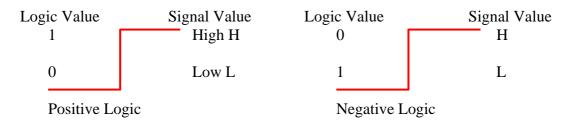

#### **Positive and Negative Logic**

## **Demonstration of positive & Negative Logic**

Positive Logic AND Gate

Negative Logic OR Gate

| xy | $\boldsymbol{z}$ |

|----|------------------|

| LL | L                |

| LH | L                |

| ΗL | L                |

| нн | н                |

| xy  | $\boldsymbol{z}$ |

|-----|------------------|

| 0 0 | 0                |

| 01  | 0                |

| 10  | 0                |

| 11  | 1                |

| xy  | z |

|-----|---|

| 11  | 1 |

| 10  | 1 |

| 01  | 1 |

| 0 0 | 0 |