# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2015/0227373 A1

Aug. 13, 2015 (43) **Pub. Date:**

## (54) STOP BITS AND PREDICATION FOR ENHANCED INSTRUCTION STREAM CONTROL

(71) Applicant: King Fahd University of Petroleum and Minerals, Dhahran (SA)

Muhamed Fawzi MUDAWAR, Dhahran (72) Inventor:

(73) Assignee: King Fahd University of Petroleum

and Minerals, Dhahran (SA)

Appl. No.: 14/175,604

Feb. 7, 2014 (22) Filed:

#### **Publication Classification**

(51) Int. Cl. (2006.01)G06F 9/38 G06F 9/30 (2006.01) (52) U.S. Cl. CPC ...... G06F 9/3804 (2013.01); G06F 9/381 (2013.01); G06F 9/30145 (2013.01)

#### (57)ABSTRACT

A microprocessor including an instruction set architecture includes: a decode and fetch control; a instruction cache; a data cache; a control stack; and an instruction set including a stop bit; a qualifying predicate; an opcode, a register and/or an immediate operand. A data processing method includes: fetch instructions encoded with a stop bit from an instruction set architecture of the microprocessor; popping, a top address off a control stack and transfer control back to a caller function, to an indirect function, or to a top of a loop block when the stop bit indicate a function return, an indirect function call, or a loop branch; save control stack registers on a backing store after the stop bit indicate the call or loop branch function when a number of used control stack registers exceeds a HI threshold; overflow a control stack signal when the number of the used and the saved entries exceeds the backing store size; allocate more memory to increase a size of the backing store from a data cache or terminate the execution; restoring, the control stack registers from the data cache when the number of the used control stack registers drops below a LO threshold.

# **Control Stack**

Fig.1A

Fig.1B

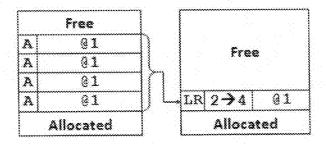

Fig.2A

| ٠,  | MARKAGA KAMPANA | 000000000000000000000000000000000000000 | and the second s | ter er er fertir for er                                                    | ************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               | 3   |

|-----|-----------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|

| - 3 |                 | 2 5                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               | . 🔅 |

| - 3 |                 | 3. 3                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 101.35 (1892) (10.05) (20.15) |     |

| - 3 | - 0             | 7 . 3                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ~~ ~~ ~~                                                                                                       | and the first than the first than the said                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | / SS 1 3 /                    |     |

| . 1 | 246.2           | 3 200                                   | 1 12 3 3 4 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | \$ 100 S | aiainia simmi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 333 45 642 / 64             | - 3 |

| : { | €3~             | 3.79.8                                  | 1.7541.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | { \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                                                         | CICKLIAN MINISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Proc 5 5 Proc 1990 1          |     |

|     | 5~              | 3.200.0                                 | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                | and the second s |                               |     |

| - 4 |                 |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |     |

| . 3 |                 |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               | 3   |

| - 1 |                 |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |     |

|     |                 |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |     |

Fig.2B

|      |     |      | 1.1    |   |    |          |       |         |     |         |    | وأووار والأوارات | منسسن | in in | w   |                       | 4   |

|------|-----|------|--------|---|----|----------|-------|---------|-----|---------|----|------------------|-------|-------|-----|-----------------------|-----|

| -30  |     | **** |        |   | ,  | *****    | ~~~~  | ******* |     |         | 1  |                  |       |       | 8   |                       | •   |

| - 1  |     |      | - 3    |   |    |          |       |         |     |         | ķ. |                  |       |       | -3- |                       |     |

| - 35 |     | 200  | . 3    |   | 8  | 42       |       |         |     | 30 b    | ķ. | ***              |       |       | 3   |                       | 3   |

| - 1  | 32% |      | 3      | ~ | ٤  | AN MINER | 10000 | 1.3     | ſΥΛ | 3.3     | ķ. | Sec.             | 23.7  |       | 3   | WILWAIDINA INTERIO    | 3   |

| 18   | 2.3 | ~    | - 3    |   | 3  | 1313     | 2000  | 1.3     | ~~  | <b></b> | ş  | 13               | CZ :  |       | ş   | 1 0-10100000 01100000 | . 2 |

| - 2  | ~   |      | - : 5  | • | 3  | ~ ;~     |       |         |     |         | ٤  |                  |       |       | ٠.  |                       | . 5 |

| - 3. |     |      |        |   | 3: |          |       |         |     |         | £  |                  |       |       | ٤.  |                       | 8   |

| - 31 |     |      | - : \$ |   | 3. |          |       |         |     |         | \$ |                  |       |       | ٤.  |                       |     |

Fig.3B

Fig.4A

Fig.4B

Fig.4C

Fig.4D

# Control Stack

Fig.5A

# **Control Stack**

Fig.5B

| - 3 | <b>{</b> | { · · | · · · · · · · · · · · · · · · · · · · | } |

|-----|----------|-------|---------------------------------------|---|

Fig.5C

| Succession | <br>S | op <sup>8</sup> | Ra <sup>6</sup> | Rb⁵      | opx <sup>5</sup> /Rc <sup>5</sup> | Rd <sup>6</sup> /plf <sup>6</sup> |

|------------|-------|-----------------|-----------------|----------|-----------------------------------|-----------------------------------|

|            | 39    | V               | <b>4</b>        | <b>{</b> | <b>{</b>                          | {:                                |

FIG.6A

FIG.6B

FIG.7A

FIG.7B

| ş     |       |          | <b>}</b> | <br> | <br> |

|-------|-------|----------|----------|------|------|

| BSize | Saved | Used TOP |          | BSP  | BOT  |

| 1     |       |          |          |      | i    |

FIG.7C

Fig.8A

Fig.8B

Fig.8C

Fig.8D

Fig.9

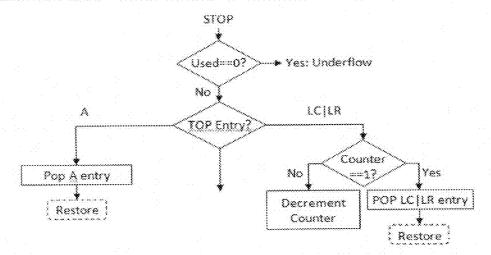

Fig.10A

Fig.10C

Fig.10B

Fig.10D

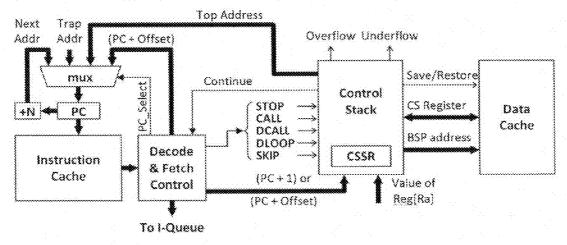

```

if (CS[TOP] == A)

Top_Address = CS[TOP].Address;

else

Top_Address = PC.HI || CS[TOP].Address;

```

```

!f (CS[TOP] == LC && CS[TOP].Count == 1)

Continue = 1;

else

Continue = 0;

```

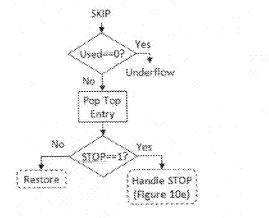

Fig.10E

Fig.10F

Fig.10G

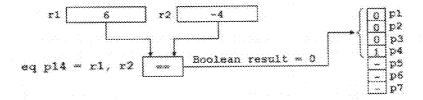

| Target ptiptf | Description                                                                                                                                                                                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p0            | Predicate p0 is always 5200 and cannot be written. Zero predicates are written. The Boolean result and its complement are discarded.                                                                                                                                     |

| pt            | This can be predicate p1 thru p7. Only one predicate pt is written. The Boolean result is written to pt, but its complement is discarded.                                                                                                                                |

| ptf Pair      | There are only six adjacent predicate pairs that can be targeted: p12, p23, p34, p45, p56, and p67. The Boolean result is written to pt and its complement is written to pf.                                                                                             |

| ptf Group     | There are fifteen non-adjacent predicate groups that can be targeted: p13, p14, p15, p16, p17, p24, p25, p26, p27, p35, p36, p37, p46, p47, and p57. The Boolean result is written to pt, its complement is written to pf, and all the in-between predicates are zeroed. |

# FIG.11A

# FIG.11B

```

{block1}

if (r1 - r2)

else if (r2 < r3) {block2}

else if (r4 != 0)

{block3}

{block4}

else

eq p14 = r1, r2 // p1=(r1==r2); p4=-p1; p2=p3=0

(p4) lt p24 = r2, r3 // if (p4) (p2-(r2<r3); p4-p2; p3-0)

// if (p4) (p3=(r4!=0); p4=~p3)

(p4) ne p34 = r4, 0

// if (pl) execute block1 instructions

(p1) block1

// if (p2) execute block2 instructions

(p2) block2

// if (p3) execute block3 instructions

(p3) block3

// if (p4) execute block4 instructions

(p4) block4

```

FIG.11C

| Target<br>ptf | 7-bit Pattern<br>tititististists | ptf code<br>x <sub>1</sub> x <sub>2</sub> t <sub>4</sub> x <sub>3</sub> x <sub>4</sub> | Target<br>ptf | 7-bit Pattern<br>tjtjtjtjtgtjt6t7 | ptf code<br>*:xytex;xe |

|---------------|----------------------------------|----------------------------------------------------------------------------------------|---------------|-----------------------------------|------------------------|

| <b>p</b> 0    | 0000000                          | 00000                                                                                  | p4            | 0001000                           | 00100                  |

| pl            | 1000000                          | 10000                                                                                  | p34           | 0011000                           | 01100                  |

| <b>p</b> 2    | 0100000                          | 01000                                                                                  | p45           | 0001100                           | 00110                  |

| р3            | 0010000                          | 00010                                                                                  | p24           | 0111000                           | 10100                  |

| p5            | 0000100                          | 10001                                                                                  | p35           | 0011100                           | 01110                  |

| p6            | 0000010                          | 01001                                                                                  | p46           | 0001110                           | 00101                  |

| <b>p</b> 7    | 0000001                          | 00011                                                                                  | p14           | 1111000                           | 11100                  |

| p12           | 1100000                          | 11000                                                                                  | p25           | 0111100                           | 10110                  |

| p23           | 0110000                          | 01010                                                                                  | p36           | 0011110                           | 01101                  |

| p56           | 0000110                          | 11001                                                                                  | p47           | 0001111                           | 00111                  |

| p67           | 0000011                          | 01011                                                                                  | p15           | 1111100                           | 11110                  |

| p13           | 1110000                          | 11010                                                                                  | p26           | 0111110                           | 10101                  |

| p57           | 0000111                          | 11011                                                                                  | p37           | 0011111                           | 01111                  |

| *******       |                                  |                                                                                        | p16           | 1111110                           | 11101                  |

|               |                                  |                                                                                        | p27           | 0111111                           | 10111                  |

|               |                                  |                                                                                        | p17           | 1111111                           | 11111                  |

|               |                                  |                                                                                        |               |                                   |                        |

Fig.12A

```

t_1=x_1 if (t_1x_1==00); t_1=0 if (t_1x_1==01); t_1=x_1x_2

t2=X2 if (t:X: == 00); t2=0 if (t:X: == 01); t2=X:

if (t; == 1)

t_{3=x_3} if \{t_{4x_4} == 00\}; t_{3=0} if \{t_{4x_4} == 01\}; t_{3=x_1+x_2} if \{t_{4} == 1\}

t_{3}=x_{1} if \{t_{4}x_{4}==01\}; t_{5}=0 if \{t_{4}x_{4}==00\}; t_{5}=x_{3}+x_{4} if \{t_{4}==1\}

t_{6}=x_{2} if \{t_{4}x_{4}==01\}; t_{6}=0 if \{t_{4}x_{4}==00\}; t_{6}=x_{4}

if (t4 == 1)

ty=x3 if (t4x4 == 01); ty=0 if (t4x4 == 00); ty=x3x4 if (t4 == 1)

t_1 = x_1 t_4 x_4 + x_1 x_2 t_4

t_2 = x_2 t_4 x_4 + x_1 t_4

t_3 = x_3 t_4 x_4 + (x_1 + x_2) t_4

t: = x3tixi + x3xiti = x3xi

t_5 = x_1 t_4 x_4 + (x_3 + x_4) t_4

t_6 = x_2 t_4 x_4 + x_4 t_4

```

Fig.12B

Fig.12C

### STOP BITS AND PREDICATION FOR ENHANCED INSTRUCTION STREAM CONTROL

#### BACKGROUND

[0001] 1. Field of the Disclosure

[0002] The exemplary embodiments described herein relate to an instruction set architecture, a microprocessor containing the instruction set architecture, and a computer processor or system using the instruction set architecture, for example in data processing systems.

[0003] 2. Description of the Related Art

[0004] In data processing systems, control instructions alter the fetching and sequencing of instructions. Conditional branch (or jump) instructions are heavily used to control loops and if-else structures. They constitute about 17% of the dynamic instruction mix in many integer benchmarks. Procedure call and return instructions are about 3% of the dynamic instruction mix as described in Hennessy et al., ("Computer Architecture: A Quantitative Approach", 5<sup>th</sup> edition, Morgan Kaufmann publishers, 2012—incorporated herein by reference).

[0005] Conditional branch instructions are used heavily for instruction stream control. They appear at the end of loop blocks and branch backwards to control the execution of loops. They also appear inside if-else structures and branch forward to skip instruction blocks. Conditional branch instructions are used differently in different architecture as described in Intel, ("Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture, Volume 2A, 2B: Instruction Set Reference, Volume 3A, 3B: System Programming Guide", November 2007—incorporated herein by reference), ARM, ("ARM Developer Suite", Version 1.2, Assembler Guide, November 2001,—incorporated herein by reference), IBM, ("Power ISA", Version 2.05, October 2007—incorporated herein by reference), Sun Microsystems, ("UltraSPARC Architecture, One Architecture Multiple Innovative Implementations", Draft D0.9.3b, 20 Oct. 2009—incorporated herein by reference), MIPS Technologies, ("MIPS64 Architecture for Programmers, Vol 1: Introduction, Vol 2: MIPS64 Instruction Set, Vol 3: Privileged Resource Architecture", Revision 3.02, Mar. 21, 2011—incorporated herein by reference) and Intel, ("Intel Itanium Architecture: Software Developer's Manual", revision 2.3, May 2010—incorporated herein by reference). Many architectures, such as Intel x86 as described in Intel, ("Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture, Volume 2A, 2B: Instruction Set Reference, Volume 3A, 3B: System Programming Guide", November 2007—incorporated herein by reference), ARM, ("ARM Developer Suite", Version 1.2, Assembler Guide, November 2001,—incorporated herein by reference), IBM Power, ("Power ISA", Version 2.05, October 2007—incorporated herein by reference), and Sun SPARC ("UltraSPARC Architecture, One Architecture Multiple Innovative Implementations", Draft D0.9.3b, 20 Oct. 2009incorporated herein by reference), use condition codes or flags (such as Zero, Negative, Carry, and Overflow) for conditional branching. Other architectures, such as MIPS ("MIPS64 Architecture for Programmers, Vol 1: Introduction, Vol 2: MIPS64 Instruction Set, Vol 3: Privileged Resource Architecture", Revision 3.02, Mar. 21, 2011—incorporated herein by reference), use conditional compare and branch instructions for control, in which general-purpose registers are compared. Few others, such as Intel Itanium, ("Intel Itanium Architecture: Software Developer's Manual", revision 2.3, May 2010—incorporated herein by reference), use predicate bits for conditional branching.

[0006] In addition, all architectures provide instructions for procedure call and return. The CALL instruction in the Intel x86 architecture pushes the return address in memory on the stack as described in Intel, ("Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture, Volume 2A, 2B: Instruction Set Reference, Volume 3A, 3B: System Programming Guide", November 2007-incorporated herein by reference). On the other hand, the JAL instruction in the MIPS architecture saves the return address in the general-purpose register R31 as described in MIPS Technologies, ("MIPS64 Architecture for Programmers, Vol 1: Introduction, Vol 2: MIPS64 Instruction Set, Vol 3: Privileged Resource Architecture", Revision 3.02, Mar. 21, 2011—incorporated herein by reference). The IBM Power ("Power ISA", Version 2.05, October 2007—incorporated herein by reference) and Intel Itanium ("Intel Itanium Architecture: Software Developer's Manual", revision 2.3, May 2010incorporated herein by reference) architectures use a specialpurpose link register to save the return address.

[0007] The return instruction has also different names in different instructions set architectures. For example, the Intel x86 architecture calls it RET as described in Intel, ("Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture, Volume 2A, 2B: Instruction Set Reference, Volume 3A, 3B: System Programming Guide", November 2007—incorporated herein by reference). When executing this instruction, the processor pops the return address from the memory stack segment into the instruction pointer. The ARM uses the MOV instruction to copy the link register R14 into the program counter register R15 as described in ARM, ("ARM Developer Suite", Version 1.2, Assembler Guide, November 2001,—incorporated herein by reference). The POWER architecture uses BCLR (Branch Conditional to Link Register) as a conditional return instruction, where the return address is stored in the link register LR as described in IBM, ("Power ISA", Version 2.05, October 2007—incorporated herein by reference). The MIPS architecture uses JR (Jump Register) as the return instruction, where register R31 contains the return address as described in MIPS Technologies, ("MIPS64 Architecture for Programmers, Vol 1: Introduction, Vol 2: MIPS64 Instruction Set, Vol 3: Privileged Resource Architecture", Revision 3.02, Mar. 21, 2011—incorporated herein by reference).

[0008] The conditional branch instruction, regardless of its name, has a high frequency that cannot be ignored. This instruction occupies space in the instruction cache, and consumes cycles and energy to execute. Branches decrease performance and consume hardware resources for dynamic branch prediction. They also restrict instruction scheduling by the compiler. This invention shows that conditional branch instructions can be eliminated in most situations. In addition, the return instruction can also be eliminated.

[0009] Some conditional branch instructions used in if-else structures can be eliminated with predication. Predication is not a new idea. It has been used in two prominent architectures: the ARM ("ARM Developer Suite", Version 1.2, Assembler Guide, November 2001,—incorporated herein by reference), and the Intel Itanium architecture ("Intel Itanium Architecture: Software Developer's Manual", revision 2.3, May 2010—incorporated herein by reference). Predication

allows the tagging of all instructions with a qualifying predicate. If the value of the qualifying predicate is false at execution time, the predicated instruction behaves like a NOP. The ARM architecture uses condition codes (Zero, Negative, Carry, Overflow) to achieve conditional execution. On the other hand, the Itanium architecture uses qualifying predicate registers to achieve conditional execution. Predication helps in reducing the number of conditional branches, especially those used in nested if-else structures. However, it cannot eliminate backward conditional branches that appear at the end of loop structures.

[0010] Another drawback of instruction set architectures is that return addresses are saved on a stack segment in memory, especially for nested procedure calls. Because return addresses can be updated and manipulated like data, attackers can induce arbitrary behavior in a program by diverting the control flow, without injecting code. This technique, called return-oriented programming, was demonstrated in Buchanan et al., ("When Good Instructions Go Bad: Generalizing Return-Oriented Programming to RISC", in Proceedings of the 15th ACM conference on Computer and Communications Security," CCS'08, pages 27-38, October 2008, Virginia, USA—incorporated herein by reference). The authors showed that return-oriented programming is not limited to the x86 ISA, but is widely applicable to many RISC architectures and operating systems (such as Linux and Solaris). Returnoriented programming defeats and bypasses the W\(\pro\)X protections, developed in operating systems, in which memory is either marked as writable or executable, but never both.

#### SUMMARY

[0011] A microprocessor, including: a decode configured to decode instructions of an instruction set architecture; a fetch control unit configured to fetch instructions from a memory; an instruction cache configured to store a plurality of fixed byte-length instructions; a data cache configured to store data; a control stack implemented with high speed control registers and a backing store allocated memory by a system software, and configured as a side effect of control and the stop bits to isolate control stack entries and addresses from direct manipulation from a user program; and an instruction set, including: a stop bit configured to indicate a function return, an indirect function call, or a loop branch, and pop a top address off the control stack and transfer the control back to a caller function, to an indirect function, or to a top of a loop block; a qualifying predicate configured to allow a compare instruction to target an arbitrary number of predicates; and an opcode configured to specify an operation to be performed.

[0012] In one embodiment, the stop bit eliminates return instructions and conditional branch instructions at an end of a loop block.

[0013] In another embodiment, the qualifying predicate allows a compare instruction to target an arbitrary number of predicates and reduces the conditional branch instructions.

[0014] In another embodiment, the stop bit marked in a conditional compare and return instruction discards a boolean result and triggers a return operation when the qualifying predicate and the boolean result are both true.

[0015] In another embodiment, the control stack replaces return instructions with the stop bit when performing loop iterates, function returns and indirect function calls.

[0016] In another embodiment, the instruction set includes a register and an immediate operand.

[0017] In another embodiment, the instruction set includes a register.

[0018] In another embodiment, the instruction set includes an immediate operand.

[0019] In a second aspect the present disclosure includes a data processing method, including:

fetching, with processing circuitry, instructions encoded with a stop bit from an instruction set architecture of the microprocessor; popping, with processing circuitry, a top address off a control stack and transfer control back to a caller function, to an indirect function, or to a top of a loop block when the stop bit indicate a function return, an indirect function call, or a loop branch;

saving, with processing circuitry, control stack registers on a backing store after the stop bit indicate the function return, the indirect function call, or the loop branch when a number of used control stack registers exceeds a HI threshold; overflowing, with processing circuitry, a control stack signal when the number of the used and the saved entries exceeds the backing store size; allocating, with processing circuitry, more memory to increase a size of the backing store from a data cache or terminating the execution; restoring, with processing circuitry, the control stack registers from the data cache when the number of the used control stack registers drops below a LO threshold.

[0020] In one embodiment, the control stack implemented with high speed control registers and a backing store allocated memory by system software, and configured as a side effect of control and the stop bits to isolate control stack entries and addresses from direct manipulation from a user program.

[0021] In another embodiment, the stop bit eliminates return instructions and conditional branch instructions at an end of a loop block.

[0022] In another embodiment, the qualifying predicate allows a compare instruction to target an arbitrary number of predicates and reduces the conditional branch instructions.

[0023] In another embodiment, the stop bit marked in a conditional compare & return instruction discards a boolean result and triggers a return operation when the qualifying predicate and the boolean result are both true.

[0024] In a further aspect the present disclosure includes a non-transitory computer-readable medium storing executable instructions, which when executed by a computer processor, cause the computer processor to execute a method including: fetching, with processing circuitry, instructions encoded with a stop bit from an instruction set architecture of the microprocessor:

popping, with processing circuitry, a top address off a control stack and transfer control back to a caller function, to an indirect function, or to a top of a loop block when the stop bit indicate a function return, an indirect function call, or a loop branch; saving, with processing circuitry, control stack registers on a backing store after the stop bit indicate the function return, the indirect function call, or the loop branch when a number of used control stack registers exceeds a HI threshold; overflowing, with processing circuitry, a control stack signal when the number of the used and the saved entries exceeds the backing store size; allocating, with processing circuitry, more memory to increase a size of the backing store from a data cache or terminating the execution; restoring, with processing circuitry, the control stack registers from the data cache when the number of the used control stack registers drops below a LO threshold.

#### BRIEF DESCRIPTION OF THE DRAWINGS

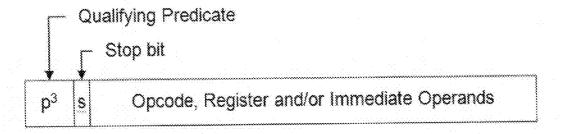

[0025] FIG. 1A depicts a block diagram of an instruction format for providing instructions in accordance with the present embodiment.

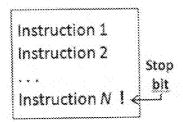

[0026] FIG. 1B depicts a block diagram of an instruction block terminated with a stop bit in accordance with the present embodiment.

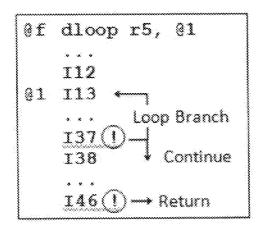

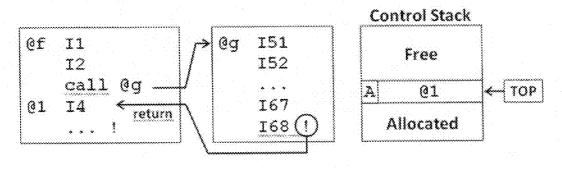

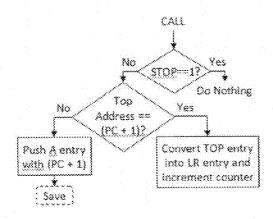

[0027] FIG. 2A depicts Call/Return Sequence when the stop bit is used as a function return in accordance with the present embodiment.

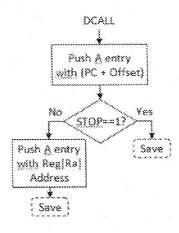

[0028] FIG. 2B depicts a block diagram of a Call/Branch instruction format in accordance with the present embodiment.

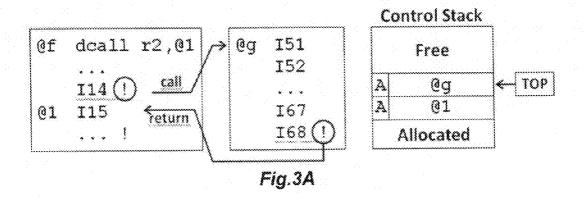

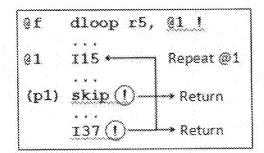

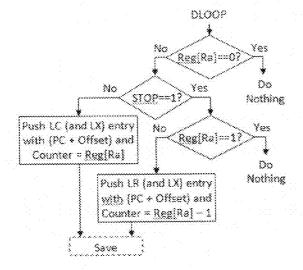

[0029] FIG. 3A depicts Deferred Call/Return Sequence when the stop bits are used for function call and return in accordance with the present embodiment.

[0030] FIG. 3B depicts a DCALL Instruction Format in accordance with the present embodiment.

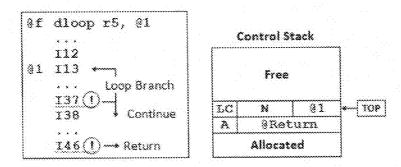

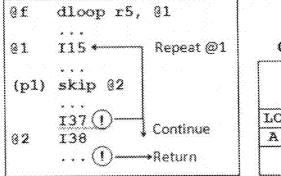

[0031] FIG. 4A depicts the stop bit used as a loop branch and a continuation signal in accordance with the present embodiment.

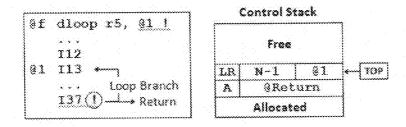

[0032] FIG. 4B depicts the stop bit used as a loop branch and a function return in accordance with the present embodiment.

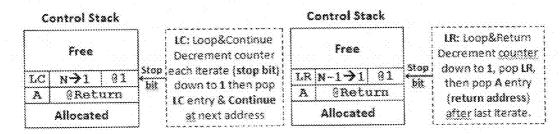

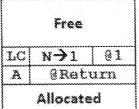

[0033] FIG. 4C depicts an operation of Loop & Continue (LC) and Loop & Return (LR) entries on control stack with the present embodiment.

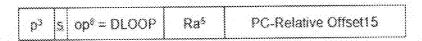

[0034] FIG. 4D depicts a DLOOP Instruction Format in accordance with the present embodiment.

[0035] FIG. 5A depicts a Skip& Continue that pops the top entry off the control stack and branches to a PC-relative in accordance with the present embodiment.

[0036] FIG. 5B depicts a Skip & Return marked with a stop bit stop bit that pops two entries off the control stack in accordance with the present embodiment.

[0037] FIG. 5C depicts a Skip Instruction Format in accordance with the present embodiment.

[0038] FIG.  $\hat{6}A$  depicts an R-type instruction format in accordance with the present embodiment.

[0039] FIG. 6B depicts an I-type instruction format in accordance with the present embodiment.

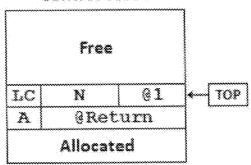

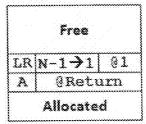

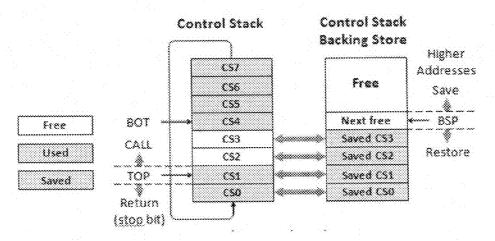

[0040] FIG. 7A depicts a control stack and a control stack backing store in accordance with the present embodiment.

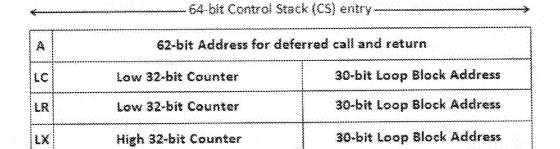

[0041] FIG. 7B depicts a format of various code segment (CS) entries in accordance with the present embodiment.

[0042] FIG. 7C depicts a block diagram of a Control Stack Status Register (CSSR) in accordance with the present embodiment.

[0043] FIG. 8A depicts an example of a recursive call to function in accordance with the present embodiment.

[0044] FIG. 8B depicts recursive calls push A-entries on the control stack having identical return addresses in accordance with the present embodiment.

[0045] FIG. 8C depicts identical Address (A) entries merged into one Loop & Return (LR) entry in accordance with the present embodiment.

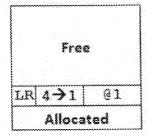

[0046] FIG. 8D depicts the returning from recursive calls reduces the Loop & Return (LR) counter when the stop bit is encountered in accordance with the present embodiment.

[0047] FIG. 9 depicts a block diagram of a control stack interface in accordance with the present embodiment.

[0048] FIG. 10A depicts a flow chart of a CALL instruction in accordance with the present embodiment.

[0049] FIG. 10B depicts a flow chart of a DCALL instruction in accordance with the present embodiment.

[0050] FIG. 10C depicts a flow chart of a DLOOP instruction in accordance with the present embodiment.

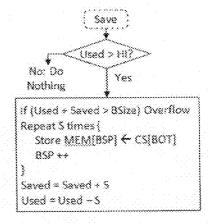

[0051] FIG. 10D depicts a flow chart of a save operation of Code Segment (CS) registers on the backing store when the number of Used CS registers exceeds a HI threshold in accordance with the present embodiment.

[0052] FIG. 10E depicts a flow chart of a processing of STOP bits for non-control instructions in accordance with the present embodiment.

[0053] FIG. 10F depicts a flow chart of a SKIP instruction in accordance with the present embodiment.

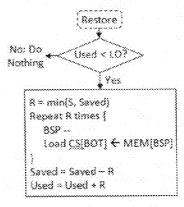

[0054] FIG. 10G depicts a flow chart of restore operations of Code Segment (CS) registers from the backing store when the number of Used CS registers drops below a LO threshold in accordance with the present embodiment.

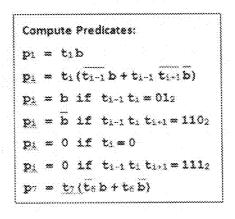

[0055] FIG. 11A depicts targeting predicates in the PR register in accordance with the present embodiment.

[0056] FIG. 11B depicts an example of targeting a group of predicates in accordance with the present embodiment.

[0057] FIG. 11C depicts an example of using a group of predicates to translate a nested IF-ELSE structure in accordance with the present embodiment.

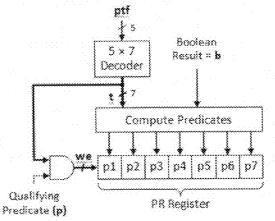

[0058] FIG. 12A depicts an encoding scheme of encoding 7-bit pattern t for targeting predicates as a 5-bit target ptf in an instruction format in accordance with the present embodiment.

[0059] FIG. 12B depicts a derivation of the logic equations for decoding the 5-bit target ptf into a 7-bit pattern t in accordance with the present embodiment.

[0060] FIG.  $\widehat{12}$ C depicts logic equations for computing all the seven predicate bits in the PR register in accordance with the present embodiment.

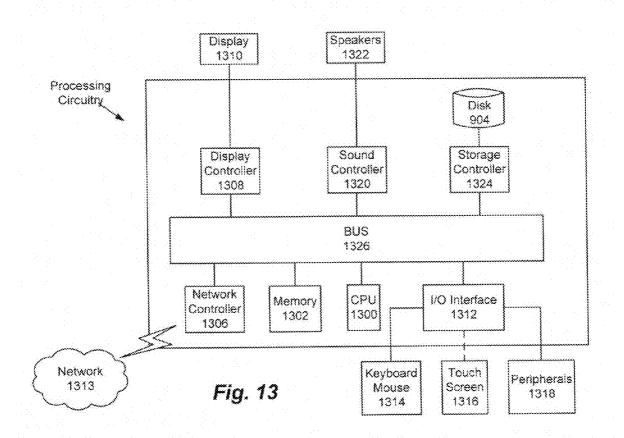

[0061] FIG. 13 shows a schematic diagram of an exemplary processing system.

#### DETAILED DESCRIPTION

[0062] The proposed embodiment uses a new instruction set architecture that features stop bits and predication. It associates a qualifying predicate and a stop bit with each instruction in the instruction set.