# King Fahd University of Petroleum and Minerals College of Computer Science and Engineering Computer Engineering Department

COE 202: Digital Logic Design (3-0-3) Term 141 (Fall 2014) Major Exam II Saturday November 29, 2014

Time: 150 minutes, Total Pages: 11

| Name:_KEY | ID: | Section: |

|-----------|-----|----------|

|           |     |          |

| Notes:    |     |          |

- Do not open the exam book until instructed

- Calculators are not allowed (basic, advanced, cell phones, etc.)

- Answer all questions

- All steps must be shown

- Any assumptions made must be clearly stated

| Question | <b>Maximum Points</b> | <b>Your Points</b> |

|----------|-----------------------|--------------------|

| 1        | 17                    |                    |

| 2        | 14                    |                    |

| 3        | 10                    |                    |

| 4        | 12                    |                    |

| 5        | 12                    |                    |

| Total    | 65                    |                    |

Question 1 (17 Points)

For the given K-map representing the Boolean function F, answer the following questions:

(i) Which one of the following is an Implicant of F:

| Term               | A'C' | A'BD | AC | A'B'C' | BCD' |

|--------------------|------|------|----|--------|------|

| Implicant<br>(Y/N) | N    | Υ    | N  | N      | Υ    |

| AB/CD | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    |    | 1  |    |    |

| 01    |    | 1  | 1  | 1  |

| 11    | 1  | 1  |    | 1  |

| 10    | 1  | 1  |    | 1  |

(ii) Which one of the following is a Prime Implicant (PI) of F:

| Term        | AC' | A'BC | BC'D | C'D | AD' |

|-------------|-----|------|------|-----|-----|

| PI<br>(Y/N) | Υ   | Υ    | N    | Υ   | Υ   |

(iii) Which one of the following is an Essential Prime Implicant (EPI) of F:

|              | C'D | A'BC | A'C' | BC'D | AD' |

|--------------|-----|------|------|------|-----|

| EPI<br>(Y/N) | Y   | N    | Z    | N    | Υ   |

(iv) Obtain a simplified sum-of-product (SOP) expression for F.

$$F = AD' + C'D + A'BC$$

(v) The following Boolean expression F = AD + A'C'D' is a simplified version of the expression F = A'B'C'D' + ABCD + AB'C'D. Are there any don't care conditions? If so, what are they?

The don't care conditions are: A'BC'D'. ABC'D, AB'CD

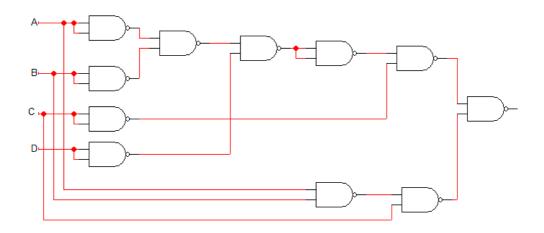

(vi) Implement the circuit given below <u>using only 2-input</u>

<u>NAND gates</u>. Redraw the circuit to obtain a multi-level

NAND circuit implementation. Assume that only the true

form of each input variable is available.

| AB/CD | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    | 1  |    |    |    |

| 01    | X  |    |    |    |

| 11    |    | X  | 1  |    |

| 10    |    | 1  | X  |    |

| A |  |

|---|--|

| В |  |

| C |  |

|   |  |

| D |  |

|   |  |

|   |  |

|   |  |

The implementation using only 2-input NAND gates is:

Question 2. (14 Points)

(i) Fill in all blank cells in the two tables below.

|          |          | Equivalent decimal v | value with the binary in | terpreted as:         |

|----------|----------|----------------------|--------------------------|-----------------------|

| Binary   | Unsigned | Signed-magnitude     | Signed-1's               | Signed-2's complement |

|          | number   | number               | complement number        | number                |

| 10110110 | 182      | -54                  | -73                      | -74                   |

|         |                  | Binary representation in 8 bits: |                       |

|---------|------------------|----------------------------------|-----------------------|

| Decimal | Signed-magnitude | Signed-1's complement            | Signed-2's complement |

|         | representation   | representation                   | representation        |

| + 100   | 01100100         | 01100100                         | 01100100              |

| - 100   | 11100100         | 10011011                         | 10011100              |

(ii) Show how the following arithmetic operations are performed using 5-bit signed 2's-complement system. Check for overflow and mark clearly any overflow occurrences.

Question 3. (10 points)

(i) It is required to design a combinational circuit that receives a 4-bit input number, X3X2X1X0, and computes the number of leading zero's in the input. For example, if the input X3X2X1X0=0111 or X3X2X1X0=0100, the output should produce a result indicating that there is a single leading zero. Construct the truth table of the circuit. You do not need to derive the Boolean expressions of the outputs. (5 points)

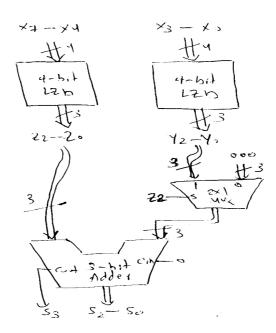

(ii) Using a block diagram of the design of the 4-bit leading-zero detector circuit in (i) and any other needed MSI blocks (e.g. Adder, Comparator, Multiplexer, Decoder, etc.), design a combinational circuit that receives an 8-bit input number, X7X6X5X4X3X2X1X0, and computes the number of leading zero's in the input. (5 points)

(i)

| X3 | X2 | X1 | X0 | <b>Z</b> 2 | <b>Z</b> 1 | <b>Z</b> 0 |

|----|----|----|----|------------|------------|------------|

| 1  | X  | X  | X  | 0          | 0          | 0          |

| 0  | 1  | X  | X  | 0          | 0          | 1          |

| 0  | 0  | 1  | X  | 0          | 1          | 0          |

| 0  | 0  | 0  | 1  | 0          | 1          | 1          |

| 0  | 0  | 0  | 0  | 1          | 0          | 0          |

(ii)

Question 4. (12 Points)

Using *only* the following modules:

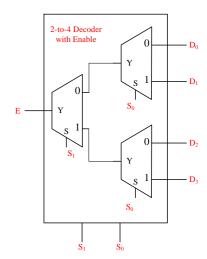

- One 2-to-4 Decoder with enable,

- One 4-to-1 MUX,

- A maximum of five 1-to-2 DeMUXs /Decoders, and

- The minimum number of 2-input NAND gates (If needed)

Implement the following assuming that <u>signals are available only in the "True" but not the complement</u> form:

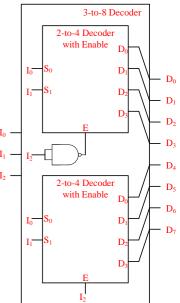

- (i) A 3-to-8 Decoder (you may use this decoder as a black-box in solving (ii) and/or (iii) below)

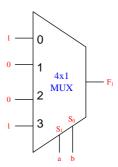

- (ii) F1(a,b) = ab + a'b'

- (iii) F2(a,b,c)=m0+m1+m2+m4+m7

### Label all your signals (inside and outside MSI components).

**(i)**

Knowing how to construct 2-to-4 decoder using 1-to-2 DeMuxs (3 points MAX)::

- Correct general structure (1 point)

- Correct general structure with accurate port labeling (3 points)

Knowing how to construct 3-to-8 decoder using 2-to-4 decoders (3 points MAX):

- Correct general structure (1 point)

- Correct general structure with accurate port labeling (2 points)

- Using NAND in place of inverter (1 point)

(ii)

Knowing how to implement a 2 variable function using 4-to-1 Mux (2 points MAX):

- Correct general structure (1 point)

- Correct general structure with accurate port labeling (2 points)

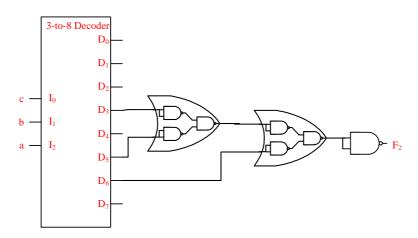

(iii)

Knowing how to implement a 2 variable function using 3-to-8 Decoder (4 points MAX):

- 1. Showing that it is more efficient to use 3-input NOR instead of 5-input OR (1 point)

- 2. Showing the implementation od 3-input NOR using 2-input NANDs (1 point)

- 3. Implementation of F2 (2 points MAX):

- Showing the correct implementation of F2 (1 point)

- Showing the correct implementation of F2 with accurate port labeling (2 point)

Question 5. (12 Points)

It is required to design an n-bit magnitude comparator. The circuit receives two n-bit unsigned numbers A and B and produces two outputs GT and EQ as given in the table to the right.

|            | GT | EQ |

|------------|----|----|

| IF $A > B$ | 1  | 0  |

| IF $A = B$ | 0  | 1  |

| IF A < B   | 0  | 0  |

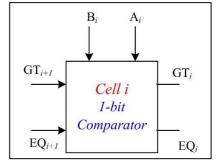

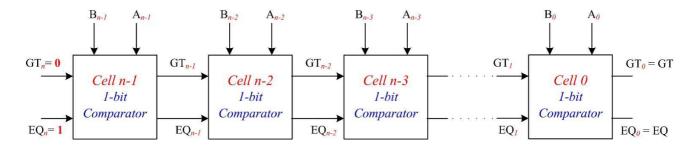

The input operands are processed in a bitwise manner <u>starting with the</u> <u>most significant bit (MSB)</u>. The comparator circuit is constructed using *n identical copies* of the basic 1-bit *cell* shown to the right. Cell **i** processes the **i**<sup>th</sup> input bits ( $A_i$  and  $B_i$ ) together with information passed to it from its predecessor cell ( $GT_{i+1}$  and  $EQ_{i+1}$ ). It produces two output bits ( $GT_i$  and  $EQ_i$ ). The *cell* output  $GT_i = 1$  <u>iff</u> ( $A_{n-1}A_{n-2}...A_{i+1}A_i > B_{n-1}B_{n-2}...B_{i+1}B_i$ ) and  $EQ_i = 1$  iff ( $A_{n-1}A_{n-2}...A_{i+1}A_i = B_{n-1}B_{n-2}...B_{i+1}B_i$ ).

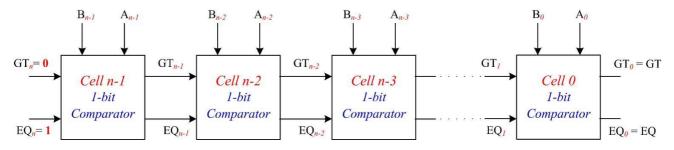

The Figure below shows the *n*-bit comparator circuit implemented using *n* copies of the basic 1-bit cell. The output of the *n*-bit comparator is that of the  $n^{th}$  cell copy (cell 0; the least-significant). Note that the inputs  $GT_n$  and  $EQ_n$  to the <u>first</u> cell (cell *n*-1; the most significant) are set to  $\underline{0}$  and  $\underline{1}$  respectively as there are no more significant bits.

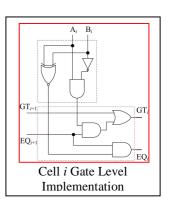

Boolean expressions of the outputs of *cell i* and its gate-level implementation are given below:

$$GT_i = GT_{i+1} + A_i \bar{B}_i EQ_{i+1}$$

, and  $EQ_i = (A_i \odot B_i) \cdot EQ_{i+1}$

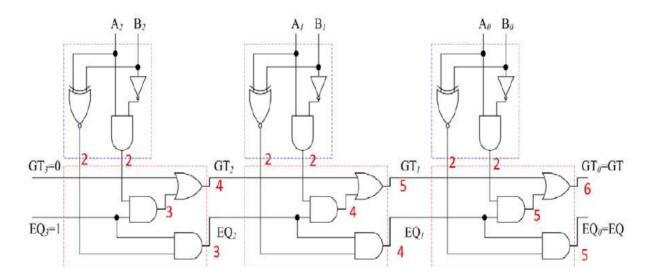

Assuming that the **XOR** and **XNOR** gates have a delay of  $2\tau$  while all OTHER gates (including inverters) have a delay of  $1\tau$ , calculate:

(i) The worst case delay of the 3-bit comparator (as a function of  $\tau$ ) shown below (4 Points)

Thus, W. C. Delay =  $6\tau$

(ii) The worst case delay of an n-bit comparator (as a function of n and  $\tau$ ) (3 Points)

## Delay components:

- Delay of the Top Logic (dependent only on Ai & Bi) = 2τ

- 2. EQ Propagation Delay = 1τ\*n

- 3. Delay of GT in the last change =  $1\tau$  (from the last EQ signal)

Total Delay =

$$2\tau + n\tau + 1\tau = (3 + n)\tau$$

(iii) Suggest a design for a cascadeable 3-bit comparator with lookahead capability. What is the worst case delay of this unit (using the same delay model of  $2\tau$  for XOR/XNOR gates and  $1\tau$  for all other gates (irrespective of their fanin)? (5 Points)

For convenience, the comparator circuit and Boolean expressions of the cell are repeated here.

Boolean expressions of the outputs of *cell i* and its gate-level implementation are given below:

$$GT_i = GT_{i+1} + A_i \, \overline{B}_i \, EQ_{i+1}$$

, and  $EQ_i = (A_i \, \Theta \, B_i) \cdot EQ_{i+1}$

$$EQ = EQ_{\theta} = (A_{\theta} \odot B_{\theta}). EQ_{I} = (A_{\theta} \odot B_{\theta}). (A_{I} \odot B_{I}). EQ_{2} = (A_{\theta} \odot B_{\theta}). (A_{I} \odot B_{I}). (A_{2} \odot B_{2}). EQ_{3}$$

$$= (A_{\theta} \odot B_{\theta}). (A_{I} \odot B_{I}). (A_{2} \odot B_{2})$$

#### Total Delay is:

- 1. Delay of the equivalence gates  $\rightarrow 2\tau +$

- 2. Delay of the AND gates to form the product  $\rightarrow 1\tau$ +

- 3. Total Delay of the EQ output = 3τ

$$GT = GT_0 = GT_1 + A_0 \, \bar{B}_0 \, EQ_1 = GT_3 + A_2 \, \bar{B}_2 \, EQ_3 + A_1 \, \bar{B}_1 \, EQ_2 + A_0 \, \bar{B}_0 \, EQ_1$$

$$= A_2 \, \bar{B}_2 + A_1 \, \bar{B}_1 (A_2 \odot B_2) + A_0 \, \bar{B}_0 (A_2 \odot B_2) (A_1 \odot B_1)$$

### Total Delay is:

- Delay of the equivalence gates → 2<sup>t</sup> +

- 2. Delay of the AND gates to form the product terms  $\rightarrow 1\tau$ +

- 3. Delay of the OR gate to form the Sum  $\rightarrow 1\tau$

- Total delay of the GT output = 4τ

Total Delay of the lookahead unit = MAX( $3\tau$ ,  $4\tau$ ) =  $4\tau$