# AUTOTUNING, CODE GENERATION AND OPTIMIZING COMPILER ${\tt TECHNOLOGY\;FOR\;GPUS}$

by

Malik Muhammad Zaki Murtaza Khan

A Dissertation Presented to the

FACULTY OF THE USC GRADUATE SCHOOL

UNIVERSITY OF SOUTHERN CALIFORNIA

In Partial Fulfillment of the

Requirements for the Degree

DOCTOR OF PHILOSOPHY

(COMPUTER SCIENCE)

May 2012

UMI Number: 3513791

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent on the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI 3513791

Copyright 2012 by ProQuest LLC.

All rights reserved. This edition of the work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346 I dedicate this thesis to my loving mother, Mrs. Tanveer Fatima Malik (Late) and to my father Mr. Malik Shahin Murtaza Khan.

## Acknowledgements

I would like to thank The Almighty, for all the blessings throughout my life. I would thank my parents for their unconditional support in every endeavour of my life. A special thanks is to my advisor, Dr. Mary Hall for her guidance and directions in my PhD research. I am fortunate to have Dr. Aiichiro Nakano and Dr. Victor Prasanna as dissertation defence committee members. A special thanks to Dr. Chun Chen, Dr. Jacqueline Chame, Gabe Rudy and Protonu Basu for many fruitful discussions.

I must acknowledge and thank my wife, Wajiha Asad Malik, my son, Muhammad Hadi Abbas, for all the support and wonderful moments we share every day. I also must acknowledge the support of my brothers Muhammad Taqi Murtaza, Muhammad Naqi Murtaza and Muhammad Razi Murtaza. Thank you.

This research was initially funded in part by MS-PhD scholarship(NUST, Pakistan). Later it was funded in part by DARPA contract HR0011-10-9-0008, Department of Energy Office of Science Award DE-FC02-06ER25765, and National Science Foundation award CCF-1018881.

## Table of Contents

| Dedica  | tion                                                     | ii   |

|---------|----------------------------------------------------------|------|

| Acknov  | wledgements                                              | iii  |

| List of | Figures                                                  | vii  |

| List of | Tables                                                   | viii |

| Abstra  | act                                                      | ix   |

| Chapte  | er 1: Introduction                                       | 1    |

| 1.1     | State-of-the-art in GPU Programming Tools                | 2    |

| 1.2     | Research Overview                                        | 3    |

| 1.3     | Example: Matrix-Matrix Multiplication                    | 4    |

|         | 1.3.1 Limitations of Manually-Tuned Libraries            | 5    |

|         | 1.3.2 Matrix-Matrix Multiplication on a GPU              | 6    |

|         | 1.3.3 Computation Partitioning                           | 6    |

|         | 1.3.4 Data Placement                                     | 7    |

|         | 1.3.5 Optimization Parameter Combinations                | 8    |

|         | 1.3.6 Summary                                            | 8    |

| 1.4     | Contributions                                            | 9    |

| 1.5     | Thesis Organization                                      | 10   |

| Chapte  | er 2: Background                                         | 11   |

| 2.1     | GPU Architecture Features                                | 11   |

| 2.2     | Compute $U$ nified $D$ evelopment $A$ rchitecture (CUDA) | 12   |

| 2.3     | Benchmarks and Libraries                                 | 13   |

| 2.4     | Parallelizing Compiler Technology                        | 15   |

|         | 2.4.1 Dependence Analysis                                | 15   |

|         | 2.4.2 Locality Analysis and Optimizations                | 16   |

|         | 2.4.3 Loop Optimizations and Transformations:            | 18   |

|         | 2.4.4 Loop Transformations                               | 18   |

| 2.5     | The Polyhedral Framework                                 | 20   |

| 2.6     | Summary                                                  | 20   |

| Chapte | er 3: System Overview                                              | 22         |

|--------|--------------------------------------------------------------------|------------|

| 3.1    | Main Components of the Compiler System                             | 22         |

|        | 3.1.1 Transformation Strategy Generator (TSG)                      | 23         |

|        | 3.1.2 Autotuning                                                   | 24         |

|        | 3.1.3 Composable High-Level Loopt Transformation Framework (CHiLL) | 24         |

|        | 3.1.4 CUDA-CHiLL                                                   | 24         |

| 3.2    | Transformation Recipe/Strategy                                     | 25         |

|        | 3.2.1 CHiLL Transformations                                        | 25         |

| 3.3    | CUDA-CHiLL: Parallelization and Data Staging                       | 26         |

|        | 3.3.1 High Level CUDA-CHiLL Commands                               | 26         |

| 3.4    | Transformations for GPU Code Generation                            | 27         |

| 0.1    | 3.4.1 Computation Mapping using Tiling                             | 28         |

|        | 3.4.2 Data Staging in Memory Hierarchy using Data Copy             | 29         |

| 3.5    | Integration Interface for TSG and CUDA-CHiLL                       | 31         |

| 3.6    | Summary                                                            | 32         |

| 3.0    |                                                                    | ٠ <b>-</b> |

| Chapte | er 4: Optimization Heuristics, Search Space and Constraints        | 33         |

| 4.1    | Optimization Strategy                                              | 33         |

| 4.2    | Optimization Heuristics                                            | 34         |

|        | 4.2.1 Computation Partitioning Heurisitics                         | 34         |

|        | 4.2.2 Data Placement Heuristics                                    | 34         |

|        | 4.2.3 Code Transformation Heuristics                               | 35         |

| 4.3    | Defining the Search Space                                          | 36         |

|        | 4.3.1 Optimization Decisions                                       | 36         |

|        | 4.3.2 Optimization Parameters                                      | 39         |

| 4.4    | Case Study: Matrix-Matrix Multiplication                           | 40         |

| 4.5    | Summary                                                            | 41         |

|        |                                                                    |            |

| Chapte | er 5: Transformation Strategy Generator                            | 43         |

| 5.1    | TSG Overview                                                       | 43         |

| 5.2    | Preprocessing of the Loop Order                                    | 45         |

| 5.3    | Phase I: Computation Partitioning Analysis                         | 45         |

|        | 5.3.1 Kernel-Level Partitioning at the Host                        | 46         |

|        | 5.3.2 Block-Level Partitioning                                     | 48         |

|        | 5.3.3 Thread level partitioning                                    | 49         |

| 5.4    | Phase II: Data Placement Analysis                                  | 49         |

| 5.5    | Phase III: Generating and Autotuning Variants                      | 51         |

| 5.6    | Phase IV: Autotuning Optimization Parameter Values                 | 54         |

| 5.7    | Selecting Parameter Values: Tile Sizes                             | 56         |

|        | 5.7.1 Understanding Features and Constraints                       | 56         |

|        | 5.7.2 Efficient Workload Management: Experimental Methodology      | 58         |

|        | 5.7.3 Selecting Tile Sizes to Maximize Device Occupancy            | 58         |

| 5.8    | Summary                                                            | 59         |

|        |                                                                    |            |

| 6.1                        | Experimental Methodology                                        |

|----------------------------|-----------------------------------------------------------------|

| 6.2                        | Performance Comparison: Manually-Tuned BLAS                     |

| 0.2                        | 6.2.1 Matrix-Matrix Multiplication                              |

|                            | 6.2.2 Matrix-Vector and Transposed Matrix-Vector Multiplication |

| 6.3                        | Performance Comparison with State-of-the-Art GPU Compiler       |

| 6.4                        | Performance Comparison of MRIQ and 2D Convolution               |

|                            |                                                                 |

| 6.5                        | Impact of Optimizations on Performance                          |

| 6.6                        | Size of Optimization Search Space                               |

| 6.7                        | Summary                                                         |

| Chapt                      | er 7: Related Work                                              |

| 7.1                        | Manually Tuned Computations                                     |

| 7.2                        | Transformation Recipe Mechanism                                 |

| 7.3                        | Annotation-Based Compiler Frameworks                            |

|                            | Automatic Parallelization for GPUs                              |

| 7.4                        |                                                                 |

| 7.4                        |                                                                 |

| 7.4<br>7.5                 | Autotuning Systems                                              |

| 7.4                        | Autotuning Systems                                              |

| 7.4<br>7.5<br>7.6          | Autotuning Systems                                              |

| 7.4<br>7.5<br>7.6          | Autotuning Systems                                              |

| 7.4<br>7.5<br>7.6<br>Chapt | Autotuning Systems                                              |

# List of Figures

| 1.1  | Matrix-matrix multiplication source code (BLAS)                                                                                          |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

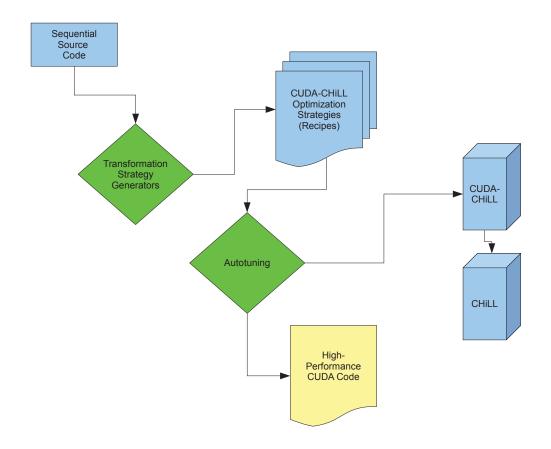

| 3.1  | Overview of system for high performance GPU (CUDA) code generation.                                                                      | 23 |

| 3.2  | A simple tiled and CUDAized 2D Convolution                                                                                               | 29 |

| 4.1  | Compiler generated transformation recipe and automatically generated code for DGEMM                                                      | 42 |

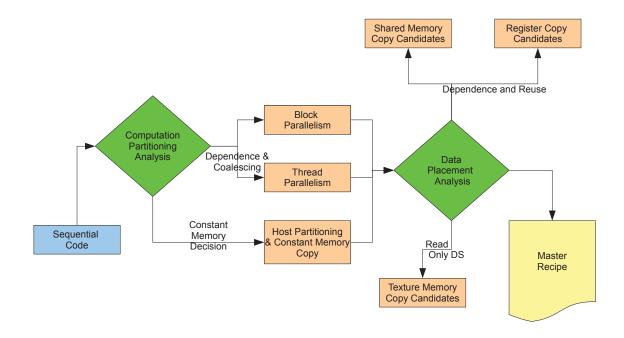

| 5.1  | Overview of the first phase of TSG, resulting in master recipe                                                                           | 44 |

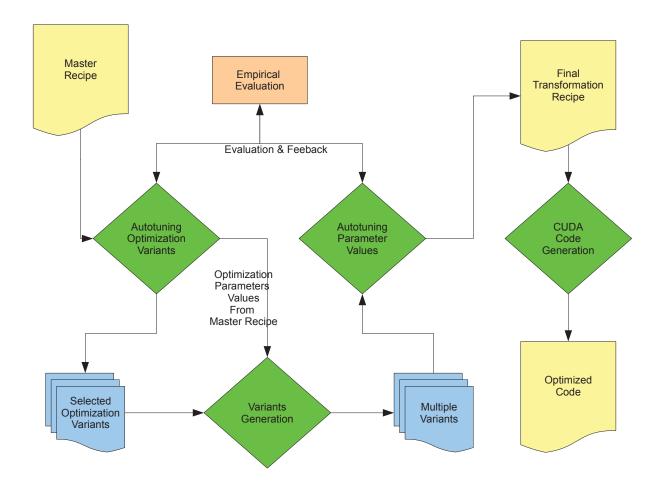

| 5.2  | Overview of the autotuning and empirical evaluation phases of the TSG                                                                    | 52 |

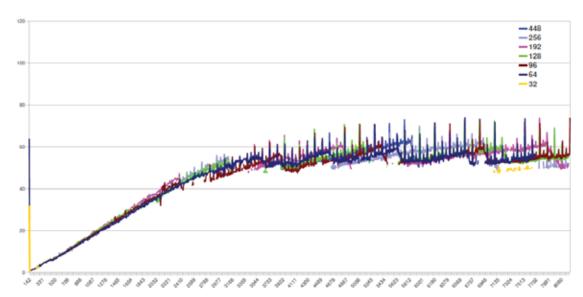

| 5.3  | Experimental evaluation of the most profitable tile sizes for matrix-vector multiplication over a range of matrix problem sizes (128-8K) | 57 |

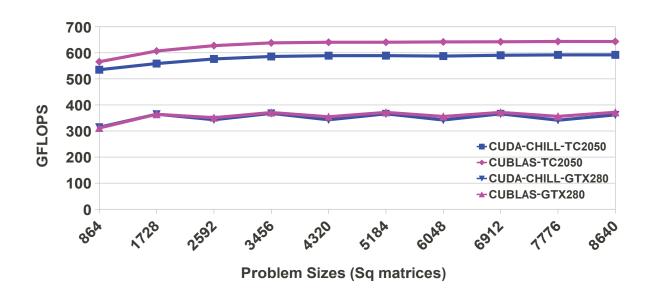

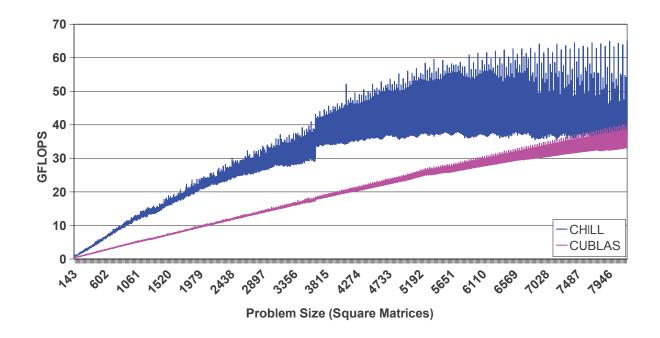

| 6.1  | SGEMM GFLOPS (vs CUBLAS 3.2)                                                                                                             | 61 |

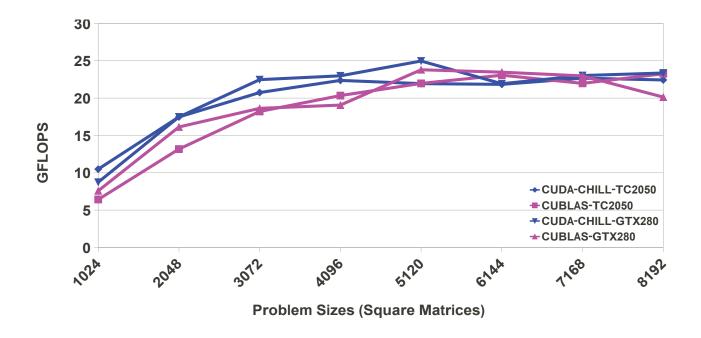

| 6.2  | SGEMM GFLOPS (vs CUBLAS 2.2 for GTX-280)                                                                                                 | 61 |

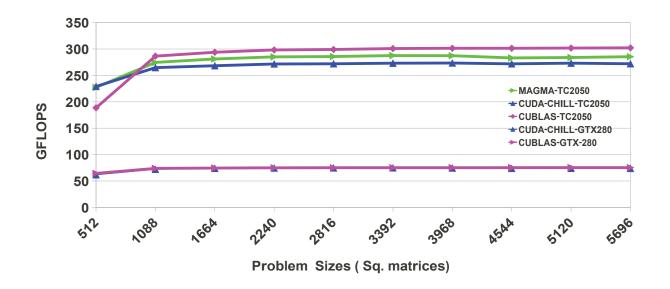

| 6.3  | DGEMM GFLOPS (vs CUBLAS 3.2)                                                                                                             | 62 |

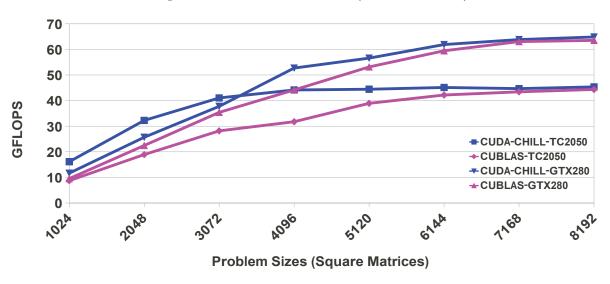

| 6.4  | SGEMV GFLOPS (vs CUBLAS 3.2)                                                                                                             | 62 |

| 6.5  | SGEMV GFLOPS (vs CUBLAS 2.2 for GTX-280)                                                                                                 | 63 |

| 6.6  | DGEMV GFLOPS (vs CUBLAS 3.2)                                                                                                             | 64 |

| 6.7  | SGETMV GFLOPS (vs CUBLAS 3.2)                                                                                                            | 65 |

| 6.8  | DGETMV GFLOPS (vs CUBLAS 3.2)                                                                                                            | 66 |

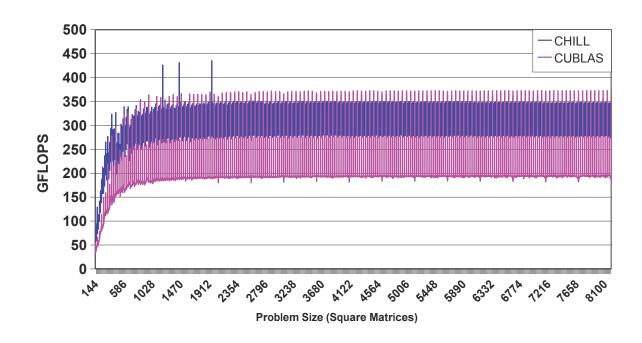

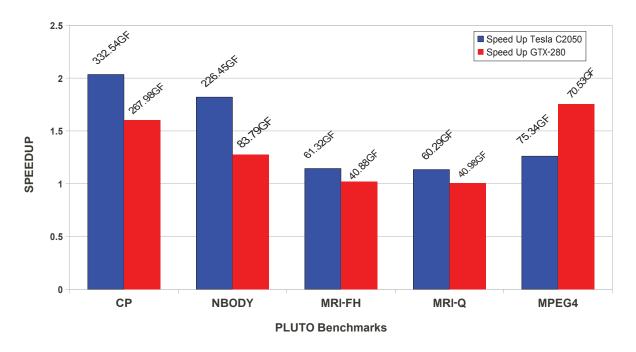

| 6.9  | Performance comparison with state-of-the-art GPU compiler in $[{\tt BRS10}]$ .                                                           | 67 |

| 6.10 | MRIQ: Sequential code and transformation strategy for C2050                                                                              | 68 |

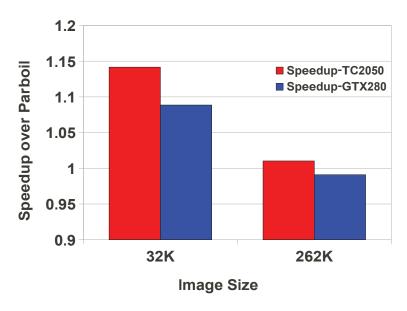

| 6.11 | MRIQ GFLOPS                                                                                                                              | 69 |

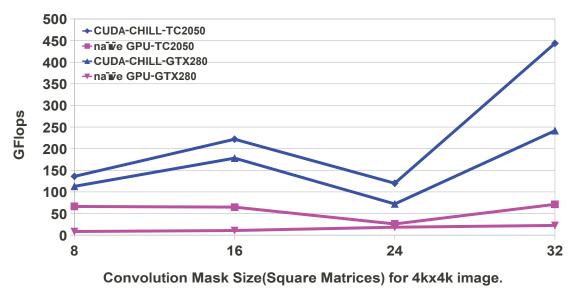

| 6.12 | 2D Convolution GFLOPS.                                                                                                                   | 69 |

## List of Tables

| 2.1 | GPU target architectures                                                       | 11 |

|-----|--------------------------------------------------------------------------------|----|

| 2.2 | Benchmarks set evaluated by CUDA-CHiLL based system                            | 14 |

| 3.1 | Description of common CHiLL commands matching higher level CUDA-CHiLL commands | 26 |

| 3.2 | Description of important high level commands in CUDA-CHiLL                     | 27 |

| 6.1 | Performance percentage loss, resulting from disabling individual optimizations | 71 |

| 6.2 | Search space pruning results for computation partitioning phase                | 72 |

| 7.1 | A comparison of GPU automatic parallelization systems                          | 76 |

### Abstract

Graphics Processing Units (GPUs) have evolved to devices with teraflop-level performance potential. Application developers have a tedious task in developing GPU software by correctly identifying parallel computation and optimizing placement of data for the parallel processors in such architectures. Further, code optimized for one architecture may not perform well on different generations of even the same processor family. Many manually tuned GPU solutions would need a complete rewrite on a different architecture, hence more programmer time and effort. High-performance computing on GPUs can be facilitated by programming models and programming frameworks that attempt to reduce the amount of time and effort needed to develop GPU applications.

This thesis describes a compiler framework for automatically generating and optimizing parallel code for GPUs (CUDA code for Nvidia GPUs), relieving programmers of the tedious work of parallelizing sequential code. The framework describes a script-based compiler for CUDA code generation combining:

- a Transformation Strategy Generator (TSG), which automatically generates multiple scripts representing different optimization strategies;

- an Autotuning System that automatically generates a set of code variants and selects the best among them through empirical evaluation.

An underlying loop transformation and code generation framework takes TSG-generated scripts as input and generates CUDA code; thus enabling an end-to-end system to produce high performance solutions for scientific computations on a given GPU architecture.

This flexible organization enables the system to explore a large optimization search space, simultaneously targeting different architecture features, but constrained by data dependences and guided by data reuse and the best heuristics from manual tuning. The system tailors the generated code to yield high-performance results for different GPU generations, data types and data sets.

The key contributions of this thesis include:

- (1) the meta-optimizer, TSG,

- (2) a search and autotuning mechanism,

- (3) integration with a script-based compiler framework, resulting in an end-to-end automatic parallelization system.

- (4) performance-portable code generation for the Nvidia GTX-280 and Nvidia Tesla C2050 Fermi architectures, and

- (5) performance gains of up to 1.84x over linear algebra kernels in the manually-tuned Nvidia CUBLAS library, and up to 2.03x for a set of scientific, multimedia and imaging kernels over a state-of-the-art GPU compiler.

### Chapter 1

### Introduction

Peak performance of graphics processors (GPUs) is now in the Teraflop range for a single device, and general purpose code on GPUs has demonstrated up to two orders of magnitude performance gains as compared to conventional CPUs [VD08a, Wol08, DMV<sup>+</sup>08, BG09]. In spite of this enormous potential, it is very difficult to develop GPU applications that make efficient use of all the architectural features and achieve high performance, particularly given the significant architectural changes across GPU generations. For example, consider Nvidia GPUs.

- Nvidia GPU chips are partitioned into multiple streaming multiprocessors (SMs),

each of which have multiple cores. Details of how a computation gets mapped to

these SMs affects the performance enormously.

- Explicit data movement from the CPU address space to the GPU memory hierarchy is needed.

- The GPU memory hierarchy must be managed explicitly in software to hide memory latency.

- Improving memory bandwidth must also be managed explicitly using memory operations supported in software, and dedicated hardware mechanisms.

- Maximum performance on a GPU may depend on tuning multiple parameters in the application.

Thus the programmer must explicitly manage available parallelism and the heterogeneous memory hierarchy. Failing to address any of these aspects appropriately may change the mapping of the computation onto the physical resources and thus may severely affect performance. Tools to simplify the programming and performance tuning process have the potential to increase the accessibility of this important technology and improve performance of the resulting code.

#### 1.1 State-of-the-art in GPU Programming Tools

Nvidia has introduced their parallel programming extension called CUDA (Compute Unified Device Architecture), which has demonstrated high performance for many scientific applications [Nvi08a, Wol08]. The CUDA parallel programming model tries to provide programmers with a modest set of language extensions to exploit the parallelism and effectively use the memory hierarchy of the Nvidia GPU devices [Nvi08a]. As previously stated, multiple aspects of programming Nvidia GPUs must be explicitly managed to maximize the performance gain. Researchers have reported days of effort to program high performing solutions for well understood problems like matrix-matrix multiplication [Wol08]. In addition to that, the portability of solutions on devices from different vendors or different generation of devices from the same vendor is also a challenging issue.

Contemporary GPU compiler solutions have tried to reduce the complexities of writing low level CUDA code. hiCUDA [HA09] and OpenMPC [LME09] are pragma-based compilers which map the parallelism expressed by the application developer to CUDA programs. These approaches are limited in what can be expressed, and may still require significant work by the programmer to partially optimize code. Compilers that optimize CUDA code [ULBmWH08, YXKZ10] can be quite effective, but require that the initial CUDA kernel be properly parallelized in a way that will facilitate optimizations.

In contrast, this thesis describes *automatic parallelization*, from sequential C code, typically with subscripts restricted to an affine domain. When applicable, automatic parallelization enables programmers with no GPU programming expertise to use GPUs.

Compared to prior compiler research on automatic parallelization for GPUs, which use a fixed optimization strategy [BBK+08b, BRS10, LVM+10], our autotuning compiler can generate multiple code variants that can be evaluated empirically. We use compiler concepts of dependence and reuse to guide transformations, rather than trying a fixed collection of optimizations that may not be suitable for a computation [CWX+11].

#### 1.2 Research Overview

In this thesis, we focus on developing a set of tools, which work in tandem to come up with high performance solutions for loop nest computations, forming a system which

- 1. Automatically analyzes a sequential code, expressed in C,

- 2. Automatically identifies the optimization opportunities in the computation,

- 3. Proposes multiple optimization strategies, and

- 4. Employs autotuning to explore a potentially large space of solutions and selects the best implementation.

The first three goals, as mentioned above, rely on extensive compiler analysis of the sequential code and strategic decisions about the optimization strategies based on architecture properties such as capacity limitations of faster memories. Compiler abstractions such as data dependences, data reuse patterns and potential constraints of the hardware and software model of the GPUs help to come up with potential computation decompositions and data placement strategies. There are two major parts of our system, focused on achieving the first three goals:

- (1) a Transformation Strategy Generator (TSG), which automatically generates multiple optimization strategies, and is the main focus of this thesis;

- (2) an underlying polyhedral loop transformation and code generation framework called CUDA-CHiLL, which takes TSG generated strategies as input and produces CUDA code;

TSG is the most important product of this research work. TSG is able to explore a large optimization space, simultaneously targeting different architecture features, but constrained by data dependences and guided by data reuse and the best heuristics from manual tuning. Additionally, this thesis describes the system which uses TSG capability with an underlying framework for composing high level loop transformations and CUDA code generation.

The complexity of mapping the computation to modern uniprocessor and multi-core architectures has been managed by *autotuning*, that employs empirical techniques to evaluate a set of alternative mappings of computation kernels to an architecture and select the mapping that obtains the best performance. The third part of the system, that addresses the last goal is:

(3) autotuning mechanism, which describes employing empirical techniques to evaluate multiple strategies and derive optimization parameter values, exploring a search space of possible implementations.

This thesis introduces a two level autotuning process which is based on separate search strategies at each level to keep the search efficient. Our system first searches for the best combination of computation decomposition and data placement choices. In the second stage we consider load balancing and resource utilization.

This thesis describes an end-to-end system producing optimized solutions for different computation kernels on two different generation GPUs. The results presented in the thesis demonstrate that the overall compiler approach is powerful, yielding performance results comparable to and sometimes exceeding the manually and automatically generated code.

#### 1.3 Example: Matrix-Matrix Multiplication

Consider the example of matrix-matrix multiplication in Figure 1.1, an important kernel used in many scientific computations. The computation is a simple triply-nested

```

for (i = 0; i < n; i++)

for (j = 0; j < n; j++)

for (k = 0; k < n; k++)

c[j][i] = c[j][i] + a[k][i] * b[j][k];</pre>

```

Figure 1.1: Matrix-matrix multiplication source code (BLAS)

loop with one computation statement. Many researchers [Che07, BBK<sup>+</sup>08a, BRS10, YXKZ10] have shown that this simple computation performs well below peak if generated automatically by a compiler. For this reason application developers often prefer to use manually-tuned BLAS libraries for matrix-matrix multiplication to speed up their application.

#### 1.3.1 Limitations of Manually-Tuned Libraries

Manually tuned libraries provide high performance routines for a set of widely used computations, which speed up parts of the application, improving the overall performance of the applications.

There are some limitations with such libraries.

- Many problems require dedicated and exclusive programming effort to devise solutions for GPUs. This approach cannot be extended to cater to the needs of the scientific community to generate general application code. Every different application needs the same amount of time and effort on the part of developers to achieve a high performance solution.

- There are only so many different solution strategies that can be explored if done manually. There is a good chance that for a certain problem, the programmer may only explore a few possible solutions in a potentially large search space of possibilities, as *it is too hard* to evaluate all of them. Thus, developers tend to settle for local maxima, ignoring the large picture due to inability to look through a large search space.

• Different versions of these libraries are needed for different platforms and may need to be modified with every new generation of a specific architecture. Thus *portability* is a major concern in developing GPU specific applications.

#### 1.3.2 Matrix-Matrix Multiplication on a GPU

We continue with the example of matrix-matrix multiplication and in light of the major goals of our system. First of all, our system analyzes the triply-nested loop computation (Figure 1.1) and comes up with a computation partitioning strategy. The system follows the computation partitioning analysis with analysis regarding the efficient use of the memory hierarchy. Multiple parallelism and data staging options are pruned out due to these analyzes, leaving a small set to be searched for a high performance solution.

#### 1.3.3 Computation Partitioning

The sequential code can be mapped to the parallel architecture in a variety of ways. There are two main factors which define the computation partitioning on a GPU.

Computation Decomposition is the logical representation of the sub-computations such as 1D, 2D etc layouts.

Computation Partitioning Parameters are the variables which may decide the size of the sub-computations and the number of blocks and number of threads per block.

A minor variation in the computation partitioning parameters or decomposition can lead to significant performance changes. Thus, achieving high performance is partly dependent on efficiently mapping the sub-computations on the available resources like the number of parallel blocks that compute parts of computation, and the number of threads per block doing the amount of work per thread and sub-computations independently. The number of threads per block dictates the number of blocks there are and thus the sub-computations to run concurrently. A minimum number of threads is necessary to

hide the latencies associated with the execution unit. An appropriate number of blocks is also necessary to balance the workload on a given set of resources.

#### 1.3.4 Data Placement

In the second stage, we decide where in the memory hierarchy each data structure will be stored. In Nvidia GPUs, the memory hierarchy consists of registers, shared memory, global memory; designated portions of global memory may have different usage and caching behavior.

**Data Placement Decisions** are made by the system after it analyzes the reuse of data in the computation for possible opportunities of using faster memory in the hierarchy [AK02]. Data reuse patterns are analyzed through the access expressions of the arrays in the computation.

For data reused across threads in a block, the data structure is identified as a candidate for shared memory. Data with an access expression that indicates reuse within a thread are selected for local storage i.e. registers. In our case study of GEMM, the input arrays are identified for shared memory, and the result array uses a register.

Data Partitioning Parameters are used to control the data footprint in the target memory, limited by the size of target storage.

The size, layout and accessing mechanism of the data from the global memory to faster but smaller memories, is crucial in achieving high performance. Some problems require the data to be read in a completely different way than they are going to be eventually accessed by the threads. Such subtleties, if ignored may lead to a crucial drop in performance. Equally important is to make decisions about the footprint of the data structures in a specific level of memory hierarchy; sometimes multiple data structures share a portion of the memory hierarchy. The overall footprint is dictated by the choices made with the data partitioning parameters.

#### 1.3.5 Optimization Parameter Combinations

In matrix-matrix multiplication, there are three optimization parameters which define the computation partitioning and data placement. There are multiple possible values that can be bound to these variables. The important considerations, while choosing a particular value for a computation partitioning parameter, are load balancing, parallelism granularity, hiding memory latency and efficient use of registers for thread-specific data. In term of CUDA execution model, these concepts are controlled by to number of parallel blocks handling sub-computations and number of threads per block. The key trade-off here is between the number of threads in a block which can become large enough to limit the number of blocks mapped to an execution unit and can be set to small enough number, where it fails to hide the latencies. Thus our system evaluates all the different valid computation partitioning options both in terms of the computation partitioning parameter values and the layout of the computation. In the case of matrix multiplication, multiple parameter values are tested and the layout of the distribution of the computation is set as 2D, given the 2-dimensional layout of the data structures involved.

Similarly, the data partitioning parameters balance maximizing reuse, minimizing overhead and staying within capacity constraints. Data partitioning is also a tiling problem, like computation partitioning. Tiling commands control the data footprint in faster memory, through tile parameters. Efficient data footprint management through tiling parameter values is coupled with the computation management parameters to obtain high performance code.

#### 1.3.6 Summary

The discussion above has focused on the problem of generating high performance code, for sequential computations, without spending huge time or human effort. We have addressed this problem by presenting a system which transforms sequential code to parallel code by deciding on a set of optimizations leading to code variants and searching a large set of different code variants to identify the best performing code. We believe the

uniquely flexible organization of our compiler provides an advantage that yields performance comparable to manually-tuned code, and this advantage is particularly on display when optimizing in the presence of the idiosyncrasies of different GPU architecture generations.

#### 1.4 Contributions

The thesis makes several key contributions, listed as follows:

- Automatic Code Transformation: A meta-optimzer called the Transformation Strategy Generator (TSG), automatically generates a collection of code transformation strategies that derive the best-performing implementations of a computation.

- Autotuning: It describes an efficient search and autotuning mechanism to derive a single high performing solution from a large search space of possible candidates.

- Integration with Script-Based Compiler Framework: It demonstrates an end-toend system, developing interfaces for integration of the TSG with an underlying script-based compiler framework for code generation.

- Performance Portability: It demonstrates an approach that selects customized implementations depending upon problem size or data type (i.e., single vs. double precision) for two Nvidia architectures (GTX-280 and Tesla C2050 Fermi).

- Experimental Evaluation: It presents automatically generated code which achieves performance of up to 1.84x over linear algebra kernels in manually-tuned Nvidia CUBLAS library; and up to 2.03x for set of scientific, multimedia and imaging kernels over a state-of-the-art GPU compiler [BUH+08, YXKZ10].

#### 1.5 Thesis Organization

The remainder of the thesis is organized as follows. Chapter 2 gives a background on GPU and CUDA. Chapter 3 describes our CUDA-CHiLL code transformation and generation compiler system. Optimization heuristics and their impact on performance, along with the search space of possible solutions and the pruning criteria is explained in Chapter 4. The core algorithms of the TSG are presented in Chapter 5. Chapter 6 presents performance results for three BLAS functions (matrix-matrix multiply, matrix-vector multiply and transposed-matrix-vector multiply), along with five other scientific and imaging kernels. Finally we discuss related work in Chapter 7 and conclude the thesis in Chapter 8.

### Chapter 2

## Background

This chapter provides background on the target architectures, benchmarks and compiler transformations that will be discussed in the remainder of the thesis.

#### 2.1 GPU Architecture Features

The two architectures for this work are the older Nvidia GeForce GTX 280, and the newer Nvidia Tesla C2050 Fermi, described in Table 2.1. Both architectures are organized in a two-level parallelism hierarchy, with a number of streaming multiprocessors (SMs), each of which has a SIMD unit comprised of several cores. Synchronization between threads in an SM is supported by a barrier; synchronization between threads mapped to different SMs typically relies on atomic operations or a return to the host processor.

The GPU devices have a heterogeneous, and mostly software controlled, memory hierarchy. Both devices have a global memory that can be accessed by all cores on the

|                         | GTX280              | C2050         |

|-------------------------|---------------------|---------------|

| #SMs                    | 30                  | 14            |

| cores/SM                | 8                   | 32            |

| Total cores             | 240                 | 448           |

| Peak (single precision) | 933  GF/s           | 1.03 TF/s     |

| Peak (double precision) | $87 \mathrm{GF/s}$  | 515  GF/s     |

| Global memory           | 1 GB                | 3 GB          |

| Bandwidth               | $142~\mathrm{GB/s}$ | 144 GB/s      |

| Shared memory/SM        | 16 KB               | (up to) 48 KB |

| Registers/SM            | 16 K                | 32 K          |

| "Texture" accesses      | yes                 | yes           |

| Constant memory         | 64 KB               | 64 KB         |

| Data cache              | 0                   | (up to) 48 KB |

Table 2.1: GPU target architectures .

device. Both devices also have a large register file consisting of 16K/32K registers, and each SM has a shared memory that threads in a block mapped to that SM can freely access. Read-only constant and texture data in global memory are cached for low-latency average access time. A data cache for global memory accesses is available on the C2050, but on the GTX280, the bulk of global memory accesses are typically not cached, with latencies on the order of hundreds of cycles.

A new architecture often requires a complete rewriting of the code, particularly if the new architecture is significantly different from previous targets for the software. While the fundamental execution model, memory structures and processor organization are similar for the two GPU devices discussed above, there are a few key differences highlighted in Table 2.1 that affect the code generation strategy.

The most significant difference is the presence of a data cache in the C2050. Further, the balance of the architectures is different. SMs in a C2050 have four times more cores than in the GTX280, which suggests that the number of threads per block should perhaps be larger on a C2050, in context of achieving higher performance. The configurable shared memory on the C2050 can be up to 3 times larger than the shared memory on the GTX280, which is consistent with being able to support more threads per block. The size of the register file per SM is also double in C2050 compared to the GTX-280 architecture. These architectural differences suggest that the optimization trade-offs may lead to different implementations for the same code, targeting the two platforms, which will be demonstrated in the performance results.

### 2.2 Compute Unified Development Architecture (CUDA)

A CUDA program describes a computation decomposition into a one or two-dimensional space of thread blocks called a *grid*, where a block is indivisibly mapped to one of the SMs. Each thread block defines a multi-dimensional space with up to three dimensions and maximum of 512 threads. A *kernel* code is executed for each point in the grid, providing a

two-level parallelism hierarchy represented by this 5-dimensional space. Threads within a block run concurrently on the same SM in batches, called *warps*, under a SIMT<sup>1</sup>execution model.

With so many parallel threads simultaneously accessing memory hierarchy, effective utilization of the memory hierarchy has significant impact on performance. The programmer or compiler can reduce memory latency through locality optimizations that copy data into lower-latency portions of the memory hierarchy as compared to global memory on data that has temporal or spatial reuse. Whenever possible, registers provide the most ready low-latency access and the register file on the GPU is large (16K/32K registers per SM, on GTX-280 and C2050, respectively). By copying data into a threadlocal variable and aggressive unrolling of loop nests, the high-level source code can expose reuse of local data that can be mapped to registers. Shared memory has latency comparable to registers (as long as there are no memory bank conflicts) for data that can be shared by all threads in a block. To maximize memory bandwidth, the memory controller will coalesce accesses to multiple data into a single memory transfer if the accessed data has spatial reuse within the size of a memory transfer [ULBmWH08]. Therefore, the programmer/compiler can order data accesses across neighboring threads (at least a half-warp in GTX-280 and a warp in Fermi architectures) so that global memory accesses are coalesced whenever possible. Another bandwidth optimization sequences shared memory accesses to avoid bank conflicts.

#### 2.3 Benchmarks and Libraries

This thesis compares performance of automatically generated code by our system with implementations from manually tuned library and state-of-the-art compiler benchmark suites for BLAS, scientific, imaging and multimedia kernel domains. Our goal is to achieve performance, comparable to these manually tuned and automatically generated

<sup>&</sup>lt;sup>1</sup>Single-instruction, multiple-thread (SIMT) is the name given to the Nvidia execution model where multiple threads in a SM execute concurrently in a lock-step manner.

benchmarks by the library and contemporary state-of-the-art compiler systems, respectively. This section provides an overview of these codes to be used throughout the thesis as examples, and in the performance evaluation of Chapter 6.

CUBLAS. CUBLAS is a basic linear algebra subprograms (BLAS) implementation from Nvidia running over Nvidia's CUDA runtime [Nvi08b]. It provides manually-tuned solutions for different linear algebra kernels, which provides us with a clean, self-contained computational resource to compare against. Over the course of this study, multiple versions of CUBLAS were released. The performance of the CUBLAS also stabilized and improved with time. We will present results from CUBLAS 2.2 and CUBLAS 3.2 to emphasize the need of systems like ours that can automatically generate optimized code and can consistently match or outperform the manually tuned code. We have compared against matrix-matrix multiplication, matrix-vector multiplication and transpose matrix-vector multiplication routines from CUBLAS, explained in detail in Chapter 6.

| Benchmarks                                   | Domain                 | Benchmark Source/       |

|----------------------------------------------|------------------------|-------------------------|

|                                              |                        | Performance Compared to |

| Matrix-Matrix Multiplication (GEMM)          | Linear Algebra         | CUBLAS                  |

| Matrix-Vector Multiplication (GEMV)          | Linear Algebra         | CUBLAS                  |

| Transpose Matrix-Vector Multiplication (TMV) | Linear Algebra         | CUBLAS                  |

| NBody                                        | Scientific Computation | PLUTO                   |

| Coulombic Potential (CP)                     | Scientific Computation | PLUTO                   |

| MPEG4                                        | Multimedia Kernel      | PLUTO                   |

| MRI-FH                                       | Imaging Kernel         | PLUTO                   |

| MRIQ                                         | Imaging Kernel         | PLUTO/PARBOIL           |

| 2D-Convolution (2D-Conv.)                    | Imaging Kernel         | Compiler by [YXKZ10]    |

Table 2.2: Benchmarks set evaluated by CUDA-CHiLL based system.

**PLUTO compiler benchmarks.** We have also compared against a state-of-the-art contemporary compiler, PLUTO [BBK<sup>+</sup>08a, BRS10, LVM<sup>+</sup>10] by using the set of benchmarks that were provided to us by the group. These include, MRIQ, MRIQ-FH, NBody, MPEG4 and CP.

PARBOIL Benchmarks. The PARBOIL benchmark suite contains many applications which are better suited to performance measurement on a massively parallel platforms. The suite is provided by IMPACT Research Group at University of Illinois, Urbana Champaign as open source software [IMP07]. We have tested the MRIQ kernel from the suite and compared the performance with the solutions provided by the suite.

In addition to these benchmarks, we also compare against an imaging benchmark, 2D convolution, from [YXKZ10], which adds to the kernels from imaging domain we compared from PLUTO and Parboil benchmark suites.

#### 2.4 Parallelizing Compiler Technology

This section presents well known compiler analyzes, used by traditional compilers for uniprocessors, shared-memory multiprocessors, vector architectures and memory hierarchy optimization. These analyzes lay the groundwork to generate GPU code by constraining computation decomposition possibilities and capturing memory access patterns.

#### 2.4.1 Dependence Analysis

In any compiler system which modifies code structure and generates transformed code, dependence analysis needs to done to ensure the correctness of the transformed code. A fundamental approach to achieve correctness in the generated code is to create a dependence graph between different statements of a sequential program. In a dependence graph, any pair of statements is called a *dependence*. Dependences ensure that that the order of the memory read and write operations is preserved [AK02].

To analyze loop nest computations, we reason about the dependences within the iteration space of the loop nest. We use dependence distances to decide about the presence of dependences.

• If all distances are zero, then the dependence is within the same iteration of the loop nest (it is loop independent).

• If at least one distance is non-zero, it is a loop carried dependence.

We use dependence analysis within our GPU compiler for the following purposes:

- identifying loop transformation opportunities

- identifying opportunities for block-level and thread-level parallelism

- identifying constraints and opportunities for loop nest transformations.

In our compiler, the presence or absence of dependences determines safety of parallelism and other reordering transformations.

There are four basic types of dependences between two operations [AK02].

- Flow (True) dependence: A statement S2 is flow dependent on S1 (written) if and only if S1 modifies a resource that S2 reads and S1 precedes S2 in execution.

- Antidependence: A statement S2 is antidependent on S1 (written) if and only if S2 modifies a resource that S1 reads and S1 precedes S2 in execution.

- Output dependence: A statement S2 is output dependent on S1 (written) if and only if S1 and S2 modify the same resource and S1 precedes S2 in execution.

- Input dependence: A statement S2 is input dependent on S1 (written) if and only if S1 and S2 read the same resource and S1 precedes S2 in execution. It is not required for safety, but is helpful for locality.

#### 2.4.2 Locality Analysis and Optimizations

Locality refers to accessing the same or nearby data close together in time, in fast memory. Many scientific applications access data in a certain pattern, which may allow for certain optimizations to improve performance.

Locality within a loop nest. A data reference is said to have *locality* if the same data or nearby stored data are accessed from the memory hierarchy level of interest by multiple iterations of a loop nest.

#### Types of Locality.

- Spatial Locality: the increased probability of accessing a nearby memory location after a certain memory access. Moving a chunk of data, including the required value along with some of the neighbors to a faster memory in the hierarchy, may help in achieving high performance.

- Temporal Locality: a special case of spatial locality, where the same memory location might be accessed again in the near future, following an access. This property allows the executing program to keep the accessed data in a faster memory in the hierarchy for a longer stretch of time, to achieve high performance.

**Locality Optimization.** In our system, we analyze the array references to identify reuse patterns, among threads and across threads. High performance can be achieved by copying data reused across threads into shared memory and reused inside threads, into registers.

The tiling transformation has been used in our system as a technique for achieving parallelism and locality optimization. Other contemporary systems [BBK<sup>+</sup>08a] have also demonstrated the use of tiling for both purposes. For data locality, tiling helps divide the iteration space into tiles which can be copied into smaller but faster memory.

An important feature of CUDA execution model is the ability to batch a number of memory accesses from global memory together in a single memory read, called *global memory coalescing*. This feature in GPUs can be exploited to bring in spatially local data from the global memory in as few as a single memory operation, for a set of threads called *warps* (16 (half-warp) or 32 threads, depending on the compute capability of the CUDA device) [Nvi08a]. Memory coalescing is probably the single most important memory access optimization, that needs to be exploited to achieve high performance and is discussed in Chapter 4.

#### 2.4.3 Loop Optimizations and Transformations:

Loop optimization enables compilers to identify parallel computations, enabling code optimizations and improved cache performance. Loop nests take much of the execution time in many computations. Optimizing loop nests to take advantage of parallelization opportunities and exploit locality results in faster execution.

#### 2.4.4 Loop Transformations

A loop transformation reorders the execution of statements in a loop. A loop transformation is said to be safe if it preserves the dependences of the original program in the modified program. In theory, each transformation is applied to achieve performance improvement, but some transformations may only be performed as a prerequisite to another transformation, which yields benefits. Thus sometimes the individual transformations are beneficial and at other times a combination of multiple transformations is needed.

#### Common loop transformations used in our system.

- Loop permutation: This optimization reorders the loops in a nest, changing the order in which memory is accessed. Such a transformation can improve locality, depending on the array's layout. Different loop orders may also enable other loop transformations or a desired loop transformation may need loop permutation as a prerequisite operation.

- Loop tiling/blocking: Loop tiling reorganizes a loop to iterate over blocks of data sized to fit in the cache. In our system, loop tiling is used to achieve parallelism and locality optimization. A loop nest's iteration space can be tiled into blocks and threads to set up the launch configuration for a kernel. Also, tiling can be used to reduce the data footprint so that it fits into smaller and faster memory in the hierarchy.

• Loop unrolling: Unrolling replicates the body of the loop multiple times, in order to decrease the number of times the loop condition is tested and the number of branches, which may degrade performance by impairing the instruction pipeline. Completely unrolling a loop eliminates all overhead (except multiple instruction fetches and increased program load time), but requires that the number of iterations be known at compile time. We use explicit unrolling of loops in order to have constant indices to the array references which can be mapped to registers. For some kernels, we differentiate ourselves from other contemporary solutions by the use of aggressive unrolling.

**Data Placement Optimizations.** Data related optimizations try to improve chances for locality, by moving data to faster memories or by increasing the memory bandwidth by using parallel hardware to access data in global memory. We target all the memories

- Data Copy (shared memory): We use data copy to move data from a slower memory to a faster one [Che07]. We use it for copying data to shared memory from the slower global memory in the context of a GPU. Data copying to a faster memory helps in improving performance by lowering access times and also by simplifying addressing. Also, it lowers the number of conflict misses in a cached architecture, by copying a tile of data into a faster memory. A copy to shared memory from global memory is available to all threads in a particular block.

- Data Copy Private (register): A specialized data copy is the copy of data to local memory of a thread, which is the register file. We use the fastest memory in the hierarchy to further improve performance.

In addition to local and shared memory, every thread has access to two more read-only spaces. These are texture memory and constant memory. Fermi architectures are also equipped with a data cache of size varying from 16k-48k. Our system targets texture and constant memory spaces too, with similar data copy transformations as to shared memory and registers.

- Data Copy (texture memory): A data copy to texture memory is achieved through a bunch of directives in the generated code, for read-only arrays. It allows for a specific array to be read through a parallel hardware used for texture reads, thus increasing the memory bandwidth.

- Data Copy (constant memory): A data copy to constant memory is a similar process as to texture memory. The size of the array is limited by the maximum constant memory size, as reported in Table 2.1.

#### 2.5 The Polyhedral Framework

The polyhedral model is a geometrical representation for loop nest computations. It uses linear algebra and linear programming techniques to analyze programs and apply code transformations. The polyhedral model [Bas04] handles a wider class of programs and transformations than the uni-modular framework, which uses a single matrix to describe the result of many transformations combined [Ban93, Ban90, WL91]. The executions of a set of statements within a possibly imperfectly nested loops is seen as the union of a set of polytopes representing the executions of the statements. Affine transformations are applied to these polytopes, producing a description of a new execution order. The boundaries of the polytopes, the data dependences, and the transformations are often described using systems of constraints. This approach is often referred to as a constraint-based approach to loop optimization. For example, a single statement within an outer loop 'for i := 0 to n' and an inner loop 'for j := 0 to i+2' is executed once for each (i, j) pair such that  $0 \le i \le n$  and  $0 \le j \le i+2$ .

#### 2.6 Summary

This chapter outlines the architectural features of the two target GPUs and the characteristics of the programming model used to program them. We focus on two particular

Nvidia GPUs in this study, which belong to two architecturally different generations of Nvidia GPUs. CUDA is the programming framework used to program them. An overview of the benchmarks we have evaluated with our system was presented. We have discussed background of important compiler functions like dependence analysis, locality analysis, and loop transformations and optimization prior to a more detailed discussion in coming chapters of their utilization in our system. Our system uses a code transformation and optimization framework which is based on the polyhedral framework and is explained in detail in the next chapter. This mathematical way of handling code transformation helps in achieving correct code generation for a range of different code variants.

## Chapter 3

## System Overview

In this chapter we present the organization of our compiler system. Figure 3.1 shows the major sub-systems, describing a chain of processes which directs both parallel computation partitioning and data staging, generates transformation strategies, and use autotuning to evaluate these and find a high performance GPU (CUDA) code solution.

#### 3.1 Main Components of the Compiler System

This section presents the overview of the compiler system, shown in Figure 3.1 which includes two components that are focus of this thesis.

- Transformation strategy generator (TSG)

- Autotuning

This core part of the system is the focus of this thesis. However, it does not work as a standalone system. It utilizes important sub-systems which are,

- Composable High-Level Loop Transformation Framework (CHiLL) [Che07]

- CUDA-CHiLL [Rud10]

The input to the compiler system is sequential C code and the output are the best performing transformation strategy along with the best performing GPU (CUDA) code.

Figure 3.1: Overview of system for high performance GPU (CUDA) code generation.

#### 3.1.1 Transformation Strategy Generator (TSG)

The major contribution of this thesis is the Transformation Strategy Generator (TSG) that analyzes the input code, derives a set of different parameterized optimization strategies, and thus logically expresses a search space of possible high performance implementations of a computation. The TSG uses analysis to decide on the code transformations while several features both related to architecture and the computations help cap the size of the possible search space of solutions. The output of the algorithms in TSG is

not code, but rather a transformation recipe that expresses an optimization strategy as a sequence of composable transformations [DBR<sup>+</sup>05, HCS<sup>+</sup>09].

#### 3.1.2 Autotuning

The other important contribution of this thesis is the mechanism of autotuning, which expresses the search space through individual transformation recipes, navigates the search space efficiently and finally finds the best performing solution for a given computation on a given architecture. The strength of this autotuning mechanism is the flexibility of independently autotune for the compiler optimizations and their respective parameters for values, to transform a given computation.

#### 3.1.3 Composable High-Level Loopt Transformation Framework (CHiLL)

CHiLL is a loop transformation framework that efficiently transforms and generates code for complex loop nest applications. We will discuss in the next section the specific CHiLL commands and their use, shown in Table 3.1. CHiLL operates most effectively on sequential code restricted to an affine domain, where loop bounds and subscript expressions are linear functions of the loop index variables. The CHiLL transformation algorithms will generate correct code when dependence conditions are satisfied. Such dependence information is kept updated during each step of the transformation process.

The script interface allows the users to compose and try many different combinations of the transformations, thus providing a flexible platform for tuning transformation solutions [CCH08]. These features make CHiLL a key component of our compiler system, providing the technology to support autotuning. We will discuss in the next section, the specific CHiLL commands and their use, shown in Table 3.1, in our system.

#### 3.1.4 CUDA-CHiLL

CUDA-CHiLL is a source to source compiler transformation and code generation framework for the parallelization and optimization of computations expressed in sequential loop nests for running on many-core GPUs. This system uniquely uses a complete scripting language to describe composable compiler transformations that can be written, shared and reused by non-expert application and library developers. CUDA-CHiLL is built on CHiLL, which is capable of robust composition of transformations while preserving the correctness of the program at each step [Che07, TCC+09, Rud10].

The rest of the chapter first explains the concept of transformation recipes, CHiLL commands constituing the low level recipes and CUDA-CHiLL followed by an overview of the core components TSG and autotuning, explained in detail in Chapter 5.

#### 3.2 Transformation Recipe/Strategy

The composition of the CUDA-CHiLL commands is called a transformation recipe or transformation strategy. It lists high level transformations in CUDA-CHiLL which may be accompanied by low level CHiLL commands. Thus a recipe is an individual strategy to modify the code structure. The transformation recipe also is the interface for application or library developers, to interact with the system directly. We use the terms transformation recipe and transformation strategy interchangeably in the rest of this thesis.

#### 3.2.1 CHiLL Transformations

Each line in a transformation recipe is a single transformation to be applied to the input code. We call each of these transformation commands. Table 3.1 describes the relation of several low level CHiLL commands to the high level CUDA-CHiLL transformation commands. The table also shows how different CHiLL commands are composed to form higher-level CUDA-CHiLL commands. However, in the implementation of these interfaces, many of the constituent transformations were used multiple times, to achieve the effect of one correct high level transformation operation. For example, the CHiLL

| CHiLL       | Used by                                                                                | Description                                                                         |  |

|-------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| Command     | CUDA-CHiLL                                                                             |                                                                                     |  |

|             | Command                                                                                |                                                                                     |  |

| tile        | tile_by_index,                                                                         | Tile a loop with a given tile size. Specify an index variable for the new           |  |

|             | copy_to_shared                                                                         | control loop and a second index variable to optionally rename the                   |  |

|             | copy_to_registers                                                                      | original index variable of the tiled loop.                                          |  |

| permute     | nute permute For a specified statement, reorder loops in a loop nest (the iteration sp |                                                                                     |  |

|             |                                                                                        | statement.) The permutation order is specified by a list of loop index variables.   |  |

| datacopy    | copy_to_shared                                                                         | For a specified statement, starting loop level and array variable, copy array data  |  |

|             |                                                                                        | that is accessed within the starting loop level to a smaller dimensional structure. |  |

|             |                                                                                        | Optionally annotate the new data structure withshared to specify a copy             |  |

|             |                                                                                        | to shared memory.                                                                   |  |

| datacopy    | copy_to                                                                                | Similar to datacopy but used to copy data private to a thread and thus              |  |

| _privatized | _registers                                                                             | does not have an option to flag for shared memory.                                  |  |

| unroll      | unroll_to                                                                              | Exposes ILP and register reuse                                                      |  |

|             | _depth                                                                                 | to the backend nvcc compiler, reduces loop overhead and can provide integer         |  |

|             |                                                                                        | speedups on GPUs.                                                                   |  |

Table 3.1: Description of common CHiLL commands matching higher level CUDA-CHiLL commands.

command *tile* is used in the composition of most of the higher level CUDA-CHiLL commands.

# 3.3 CUDA-CHiLL: Parallelization and Data Staging

CUDA-CHiLL, just like CHiLL, provides a powerful scripting interface which allows the users to define transformations at a much more abstract level than CHiLL. Usually, the CUDA-CHiLL abstractions incorporate many CHiLL commands in a single high-level command. Thus, it provides a much more accessible way of programming the GPUs by hiding the low level constructs and details of the GPU programming models. An important feature that CUDA-CHiLL inherits from CHiLL is the capability of the framework to transform sequential code for any given architecture with appropriate modifications to the code generation part of the system. This section will list in detail the CUDA-CHiLL constructs, their individual composition from CHiLL commands and the parameters driving their operations.

#### 3.3.1 High Level CUDA-CHiLL Commands

Our compiler system expresses an optimization strategy as a sequence of composable transformations, which has been followed as a way of laying out the optimization strategy in multiple research works [DBR<sup>+</sup>05, CWX<sup>+</sup>11, HCS<sup>+</sup>09]. Our system expresses the

| Command           | Example Parameter List    | Description                                                               |

|-------------------|---------------------------|---------------------------------------------------------------------------|

| tile_by_index     | {"i","j"}                 | The index variables of the loops that will be tiled.                      |

| tile_by_index     | {TI,TJ}                   | Variables representing the respective tile sizes for each index variable. |

|                   | {l1_control="ii",         | Specifies control loop variable names and                                 |

|                   | 12_control="jj"}          | optionally renames tile loop index variables.                             |

|                   | {"ii", "jj", "i", "j",    | Final order of nested loops with updated loop                             |

|                   | "k", "1"}                 | index names.                                                              |

|                   | "conv_GPU"                | The name of the kernel function                                           |

| cudaize           | ${a=(N+M)*(N+M), b=M*M,}$ | The data sizes of the arrays if not statically                            |

|                   | c=(N+M)*(N+M)             | determinable.                                                             |

|                   | {block={"ii"},            | Specifies block and thread indices. The                                   |

|                   | thread={"jj"}}            | bounds for these loops are used to derive grid                            |

|                   |                           | dimensions.                                                               |

| copy_to_registers | "kk"                      | The loop level, given as an index variable, to                            |

| copy_co_registers |                           | place the copy.                                                           |

|                   | "b"                       | The array variable to be copied.                                          |

|                   | "tx"                      | The loop level, given as an index variable, to                            |

| copy_to_shared    |                           | place the copy.                                                           |

|                   | "b"                       | The array variable to be copied.                                          |

|                   | -16                       | Ensure the last dimension of the temporary                                |

|                   |                           | array are coprime with 16 to pad.                                         |

| copy_to_texture   | "b"                       | The array variable to be accessed from texture                            |

|                   |                           | memory.                                                                   |

| copy_to_constant  | "b"                       | The array variable to be accessed from con-                               |

|                   |                           | stant memory.                                                             |

| unroll_to_level   | 1                         | Unrolls all statements up to specific level from                          |

|                   |                           | innermost loops outwards. Stops unrolling if                              |

|                   |                           | it encounters a CUDA thread index.                                        |

Table 3.2: Description of important high level commands in CUDA-CHiLL.

code transformations at a very high level using the CUDA-CHiLL constructs described in Table 3.2. When necessary, slightly lower level CHiLL transformation such as tiling individual loops, unrolling a specific loop and so on, can also be performed. CUDA-CHiLL takes these high level transformation specifications tailored to CUDA code generation and generates the specific set of compiler transformations that must be composed to produce the CUDA code. This abstraction layer is written in the embeddable scripting language Lua [IdFF96], which permits the compiler developer to concisely express the transformation algorithms.

# 3.4 Transformations for GPU Code Generation

In this section, we briefly explain the process of generating optimized CUDA code from sequential code through the high level CUDA-CHiLL commands, as shown in Table 3.2.

#### 3.4.1 Computation Mapping using Tiling

We observe that an Nvidia GPU is a *tiled* architecture, with each streaming multiprocessor (SM) representing a separate tile with its own private memory, similar to RAW [TKM<sup>+</sup>02]. Therefore, to generate code that executes in parallel across SMs, we need a computation decomposition where each SM operates on localized data. Then, each thread also operates on mostly independent data.

Subdividing the iteration space of a loop into blocks or tiles with a fixed maximum size has been widely used when constructing parallel computations [Wol89, KM92]. The shape and size of the tile can be chosen to take advantage of the target parallel hardware and memory architecture, maximizing reuse while maintaining a data footprint that meets memory capacity constraints. Sometimes referred to as loop blocking, tiling involves deconstruction of an iteration space into a control loop and tile loop. Given an iteration space of size N and a tile size of TX the tile loop will iterate over a maximum space defined by the tile size (TX), while the control loop then has N/TX steps (when TX divides N evenly).

Figure 3.2 represents a simple computation partitioning and CUDA code generation for the 2D convolution code shown in Figure 3.2(a). The two tile commands in the recipe of Figure 3.2 (b) result in the tiling of both the i and j loops of the sequential computation, as shown by the automatically generated code of Figure 3.2 (c) resulting from applying the recipe to the sequential code and printing the intermediate result at line 5.

After tiling, the *cudaize* command specifies the name of the generated kernel function, the mapping of one or two loop levels to block indices in the grid dimension, and the mapping of up to three loops to thread indices. The effect of the *cudaize* call on the generated code is to allocate storage and marshal inputs for the CUDA kernel, and select the loops from the transformed loop nest that will be mapped to grid and thread dimensions. These tile controlling loops are effectively removed from the code. The resulting automatically generated CUDA code is shown in Figure 3.2 (d).

```

void seqConv(float c[N+M][N+M], float a[N+M][N+M],float b[M][M])

int i,j,k,l;

for (i = 0; i < N; ++i)

for (j = 0; j < N; ++j)

for (k = 0; k < M; ++k)

for (1 = 0; 1 < M; ++1)

c[i][j] = c[i][j] + a[k+i][l+j] * b[k][l];

(a) The 2D-convolution sequential source code.

1 TI=16

2 TJ=16

3 tile_by_index({"i","j"}, {TI,TJ},

{l1_control="ii", l2_control="jj"},

{"ii", "jj", "i", "j", "k", "l"})

cudaize(''conv_GPU'', a=(N+M)*(N+M), b=M*M, c=(N+M)*(N+M),

block=''ii'',''jj'', thread=''i'',''j'')

(b) A very simple transformation recipe.

for (ii = 0; ii < 64; ii++)

for (jj = 0; jj < 64; jj++)

for (i = 16 * ii; i < 16 * ii + 16; i++)

for (j = 16 * jj; j < 16 * jj + 16; j++)

for (k = 0; k < M; ++k)

for (1 = 0; 1 < M; ++1)

c[i][j] = c[i][j] + a[k+i][l+j] * b[k][1];

(c) The results of tiling the sequential code.

__global__ void conv_GPU(float (*c)[1024], float (*a)[1024],

float (*b)[16])

int bx = blockIdx.x; int tx = bx*blockDim.x+threadIdx.x;

int by = blockIdx.y; int ty = by*blockDim.y+threadIdx.y;

for (k = 0; k < M; ++k)

for (1 = 0; 1 < M; ++1)

c[tx][ty] = c[tx][ty] + a[k+tx][1+ty] * b[k][1];

(d) The resulting CUDA kernel, invoked as gpuConv\langle\langle\langle 64, 64\rangle\rangle\rangle\langle\ldots\rangle

```

Figure 3.2: A simple tiled and CUDAized 2D Convolution.

#### 3.4.2 Data Staging in Memory Hierarchy using Data Copy

Multiple transformations are used for the complex data copy operations, to enable movement of data to faster memory levels of the hierarchy. We present them in the following subsections, to individually study their role and effects on data staging operations. Data Copy. The main operation for data staging is the copying of data into different levels of memory hierarchy. CUDA-CHiLL specifies separate data copy commands, specifying copy of data in register, shared memory, texture memory and constant memory. All of these copy commands work on the name of the data structure given as parameter, but only two, the copy to registers and copy to shared memory are supplied with the intended loop level positions for the copy loops. For texture memory and constant memory copies, only the names of the data structures is enough to use the respective memories. To support CUDA code generation, we augment pre-existing data copy with a new capability that supports parallel code generation and GPU-specific memory structures.

When copying into shared memory, the copy must be properly synchronized to avoid race conditions with other threads. Further, a private copy into registers copies a data footprint that is private to individual threads. The code generator must also use the right type annotation, \_\_shared\_\_ for shared memory and a local variable declaration for registers. Because of their robust underlying implementation in a polyhedral framework, these datacopy transformations ensure correctness by understanding the data dependences between loop statements, deriving conservative data footprints automatically for a specific loop nest level, and handling cases of unevenly divisible loop ranges. This again simplifies an error prone optimization step in achieving high performance CUDA kernels.

Tiling for Data Copy. In addition to its role in setting up parallelization, tiling also reorganizes computation within or across threads in the program so that the data footprint fits within a specific level of the memory hierarchy. Data destined for shared memory must be explicitly copied to/from the device global memory. Similarly, data locally declared within a thread program will usually be placed in registers by the nvcc backend compiler, but such data may require explicit copies to/from global or shared

memory. Therefore, we couple tiling with explicit copying of data and associated synchronization to perform the *data staging* into shared memory or registers.

When managing registers, we must also explicitly unroll the tiled loops so that accesses to local array data will have constant indices that can be mapped to specific registers. CHiLL supports loop unrolling through a combination of iteration space transformations and statement rewriting.

### 3.5 Integration Interface for TSG and CUDA-CHiLL

We have integrated the sub-systems described in this chapter to form an end-to-end system. There are two separate interfaces we have developed as part of this work. The core part of the CUDA-CHiLL interface to CHiLL, is written in C++, and provides the CHiLL transformations, the data structures representing the current state and GPU related transformation and code generation capabilities.

The main contribution of our work to the Lua interface is limited to the handling of data copy operations for registers and shared memory and unroll to a certain depth level for the whole code structure. The goal, in the case of data staging operations for registers and shared memory, is to create data copy loops at the correct locations in the generated code.

- (1) Computation Partitioning: The computation partitioning interface (added in this list for completion purposes) remains the same as was provided by CUDA-CHiLL, with its basic functionality of applying tiling transformation to modify loop nests to create loops carrying parallelism.

- (2) Data Copy Interfaces: The data copy interfaces were the major contribution of the integration code. The interfaces initially provided for the shared memory copy and register copy were basic and limited to a few BLAS computations only. The shared memory data copy interface had to be re-written to incorporate the scenarios which arose from new computations. New code structures were written