# A Hardware Model of an Expandable RSA Cryptographic System

by

Adnan Abdul-Aziz M.S. Gutub

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

**MASTER OF SCIENCE**

In

**COMPUTER ENGINEERING**

December, 1998

**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company

300 North Zeeb Road, Ann Arbor MI 48106-1346 USA

313/761-4700 800/521-0600

## **NOTE TO USERS**

The original document received by UMI contains pages with indistinct print. Pages were microfilmed as received.

This reproduction is the best copy available

**UMI**

# A Hardware Model of an Expandable RSA Cryptographic System

Adnan Abdul-Aziz M.S. Gutub

A Thesis Presented to the FACULTY OF THE COLLEGE OF GRADUATE STUDIES KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN, SAUDI ARABIA

> in Partial Fulfillment of the Requirements for the Degree of

# MASTER OF SCIENCE

Computer Engineering

December 1998

UMI Number: 1393212

UMI Microform 1393212 Copyright 1999, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

# بسم الله الرحمن الرحيم

هِ قُلْ اللهِ اللهِ اللهِ اللهُ الل

سليمان عليه السلام القرآن الكريم: سورة النمل

This is of the bounty of my Lord, to test me as to weather I am grateful or ungrateful. He who is grateful is but grateful for his own good; and he who is ungrateful, verily, my Lord is self-sufficient, most generous.

#### Prophet Solomon

Quran 27:40

#### KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN 31261, SAUDI ARABIA

#### COLLEGE OF GRADUATE STUDIES

The Thesis, written by

#### Adnan Abdul-Aziz M. S. Gutub

under the direction of his Thesis advisor and approved by his Thesis Committee, has been presented to and accepted by the Dean of the College of Graduate Studies, in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee:

10 1.

27.12.98

Dr. Alaaeldin Amin (Chairman)

Dr. Khalid Elleithy (Member)

28/1294

Dr. Khalid Al-Tawil (Member)

Department Chairman

Dean, College of Graduate Studies

<u>30-12-98</u> Date **Dedicated**

To

My Parents

#### **Acknowledgments**

First and foremost, all praise to the Almighty ALLAH who gave me the courage and patience to carry out this work.

Acknowledgment is due to King Fahd University of Petroleum and Minerals for providing support to do this work.

My deep appreciation goes to Dr. Alaaeldin Amin, who served as my Thesis advisor. I also wish to thank the other members of my Thesis Committee Dr. Khalid Elleithy and Dr. Khalid Al-Tawil.

Thanks are due to my Professors: Dr. Sadiq Sait, Dr. Mostafa Abd-El-Barr and Dr. Atif Al-Najjar, for their encouragement and valuable advises.

I am very grateful to my wonderful wife (Manal M. Fattani) and children (Muna and Alaa), without their patience and sacrifices such a major undertaking and its completion would have not been possible.

Finally, my profound gratitude and appreciation go to the rosy part of my life, to my mother (Amnah S. Sait) and father (Dr. Abdul-Aziz M.S. Kutub), for their continuos prayers, encouragement and moral support.

# Contents

|   | List | of Figu  | res                                    | ix   |

|---|------|----------|----------------------------------------|------|

|   | List | of Tabl  | les                                    | хi   |

|   | Abst | ract (E  | English)                               | xii  |

|   | Abst | ract (A  | Arabic)                                | xiii |

| i | Intr | oducti   | ion                                    | 1    |

| • | 1.1  |          | Objective                              | 2    |

|   | 1.2  |          | Outline                                | 2    |

|   | 1.2  | 1 116212 | Outilie.                               | _    |

| 2 | Cry  | ptogra   | aphic Systems                          | 4    |

|   | 2.1  | Introd   | uction                                 | 4    |

|   |      | 2.1.1    | Substitution                           | 5    |

|   |      | 2.1.2    | Transposition                          | 6    |

|   | 2.2  | Public   | : Key Cryptosystems                    | 6    |

|   |      | 2.2.1    | Fundamental Operators                  | 7    |

|   |      | 2.2.2    | Historical Background                  | 8    |

|   | 2.3  | The R    | SA System                              | 9    |

|   |      | 2.3.1    | RSA Encryption                         | 10   |

|   |      | 2.3.2    | Generation of the RSA Keys             | 10   |

|   |      | 2.3.3    | Example on Encryption Using RSA System | 10   |

|   |      | 2.3.4    | The RSA Digital Signature Scheme       | 11   |

|   |      | 2.3.5    | Security of the RSA Cryptosystem       | 12   |

|   |      | 2.3.6    | RSA Speed                              |      |

|   | 2.4 | Summ                                         | ary                                                | 12 |

|---|-----|----------------------------------------------|----------------------------------------------------|----|

| 3 | Rev | view of                                      | RSA Hardware Implementations                       | 13 |

|   | 3.1 | Introd                                       | uction                                             | 13 |

|   | 3.2 | Gener                                        | al Techniques for Modular Operations               | 14 |

|   |     | 3.2.1                                        | The Repeated Squaring Algorithm                    | 14 |

|   |     | 3.2.2                                        | General Modular Multiplication Techniques          | 15 |

|   | 3.3 | Logari                                       | thmic Speed Implementation                         | 17 |

|   |     | 3.3.1                                        | The Algorithm                                      | 17 |

|   |     | 3.3.2                                        | The Implementation                                 | 18 |

|   | 3.4 | Imple                                        | mentations of Montgomery's Algorithm               | 18 |

|   |     | 3.4.1                                        | Montgomery's Algorithm For Exponentiation          | 18 |

|   |     | 3.4.2                                        | Montgomery's Algorithm Hardware Designs            | 19 |

|   | 3.5 | Full R                                       | SA Implementations                                 | 20 |

|   | 3.6 | 6 Systolic Arrays for Modular Exponentiation |                                                    |    |

|   |     | 3.6.1                                        | Systolic Array for Multiplication                  | 21 |

|   |     | 3.6.2                                        | Montgomery Reduction by the Systolic Multiplier    | 22 |

|   | 3.7 | Summ                                         | ary                                                | 24 |

| 4 | A E | Hardwa                                       | re Model of an Expandable RSA Cryptographic System | 26 |

|   | 4.1 | Introd                                       | uction                                             | 26 |

|   | 4.2 | The S                                        | ystolic Multiplier                                 | 27 |

|   |     | 4.2.1                                        | The Basic Cell of The Systolic Multiplier          | 28 |

|   |     | 4.2.2                                        | The b-bit Parallel Multiplier                      | 29 |

|   | 4.3 | Montg                                        | gomery Product Design                              | 29 |

|   |     | 4.3.1                                        | Montgomery Product Implementation                  | 3  |

|   |     | 4.3.2                                        | Expandability of the parallel MP Implementation    | 32 |

|   |     | 4.3.3                                        | The Expandable MP Design                           | 33 |

|   | 4.4 | The M                                        | Modular Exponentiation System                      | 38 |

|   |     | 441                                          | The Basic Exponentiation Processor                 | 36 |

|   |      | 4.4.2  | The Expansion hardware                                 | 37 |

|---|------|--------|--------------------------------------------------------|----|

|   |      | 4.4.3  | The Expandable MP Module                               | 37 |

|   | 4.5  | Summ   | ary                                                    | 37 |

| 5 | Oth  | er Imp | olementations                                          | 39 |

|   | .5.1 | Introd | uction                                                 | 39 |

|   | 5.2  | The M  | lerged Exponentiation Hardware                         | 39 |

|   |      | 5.2.1  | The Merged Montgomery Product Algorithm                | 4( |

|   |      | 5.2.2  | The Merged MP Implementation                           | 4  |

|   |      | 5.2.3  | The Multiplication Loop Implementation                 | 43 |

|   |      | 5.2.4  | The Reduction Loop Implementation                      | 44 |

|   |      | 5.2.5  | The Merged Exponentiation Implementation               | 46 |

|   | 5.3  | The A  | dd/Subtract Exponentiation Design                      | 46 |

|   |      | 5.3.1  | The Add/Subtract Reduction Unit Implementation         | 47 |

|   |      | 5.3.2  | The Add/Subtract Multiplication Implementation         | 47 |

|   |      | 5.3.3  | The Modular Add/Subtract Exponentiation Implementation | 49 |

|   | 5.4  | Summ   | ary                                                    | 5( |

| 6 | Mo   | deling | and Analysis                                           | 5] |

|   | 6.1  | Introd | uction                                                 | 5  |

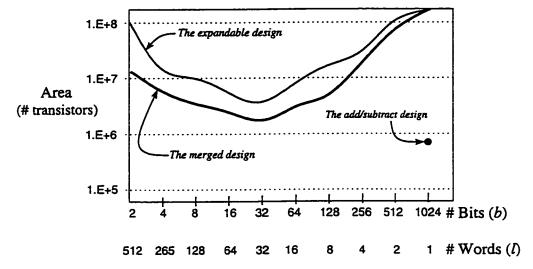

|   | 6.2  | Impler | nentation Area                                         | 5  |

|   |      | 6.2.1  | Area of The RSA Implementations                        | 54 |

|   | 6.3  | Speed  | and Cost                                               | 5  |

|   |      | 6.3.1  | The Expandable Hardware Cost                           | 56 |

|   |      | 6.3.2  | The Merged Exponentiation Design Cost                  | 56 |

|   |      | 6.3.3  | The Add/Subtract Exponentiation Design Cost            | 5  |

|   | 6.4  | VHDL   | Modeling                                               | 5  |

|   | 6.5  | Analys | sis                                                    | 59 |

|   |      | 6.5.1  | Area and Delay                                         | 59 |

|   |      | 652    | The Implementations Cost                               | 60 |

|   | 6.6  | Summary                 | 62 |

|---|------|-------------------------|----|

| 7 | Cor  | clusion and Future Work | 64 |

|   | 7.1  | Conclusion              | 64 |

|   | 7.2  | Future Work             | 65 |

|   | Bibl | ·<br>iography           | 66 |

|   | Vita |                         | 70 |

# List of Figures

| 2.1  | The information flow in a classical cryptographic system        | 4  |

|------|-----------------------------------------------------------------|----|

| 2.2  | Public key cryptographic system (general concept)               | 8  |

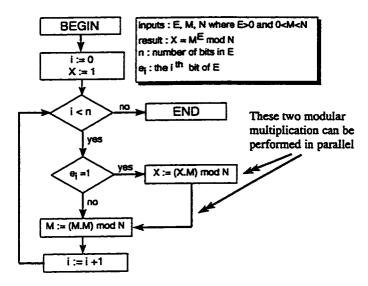

| 3.1  | The repeated squaring algorithm                                 | 14 |

| 3.2  | The improved repeated squaring algorithm                        | 15 |

| 3.3  | The multiplication with reduction modified algorithm            | 16 |

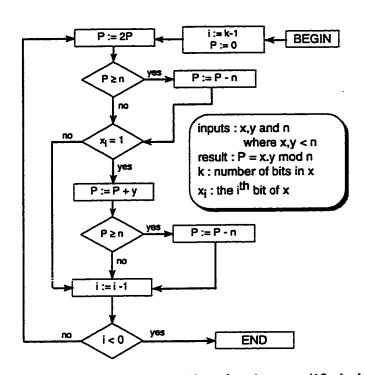

| 3.4  | Montgomery's algorithm for modular exponentiation               | 18 |

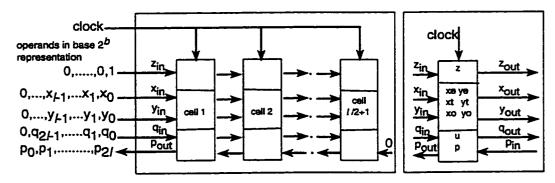

| 3.5  | The systolic array                                              | 21 |

| 3.6  | The algorithm for a cell behavior                               | 22 |

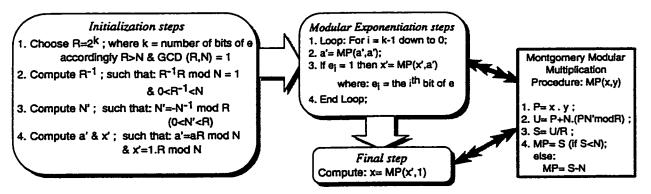

| 3.7  | The systolic Montgomery reduction                               | 23 |

| 3.8  | Sauerbrey's implementation of Montgomery modular multiplication | 24 |

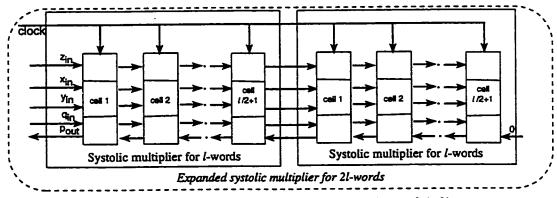

| 4.1  | The word-serial multiplier (systolic array)                     | 27 |

| 4.2  | Expandability of the systolic multiplier                        | 27 |

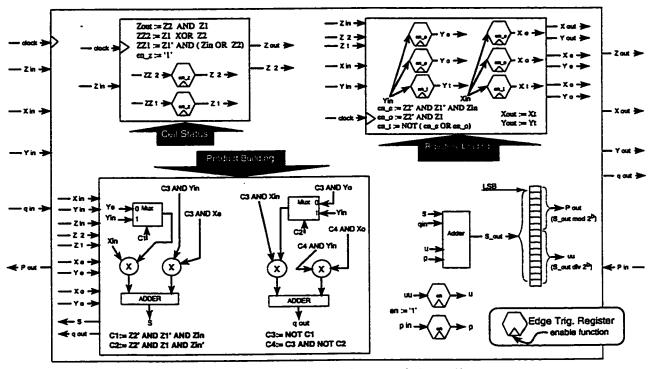

| 4.3  | Hardware design of the cell                                     | 28 |

| 4.4  | Hardware design of 4-bits parallel multiplier                   | 30 |

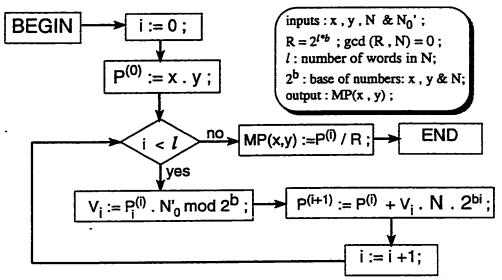

| 4.5  | The MP-algorithm (Montgomery Product)                           | 31 |

| 4.6  | The signal flow graph                                           | 31 |

| 4.7  | The signal flow graph MP implementation (parallel hardware)     | 32 |

| 4.8  | Expandability of the parallel implementation                    | 33 |

| 4.9  | Projecting all parallel and systolic multipliers into one       | 33 |

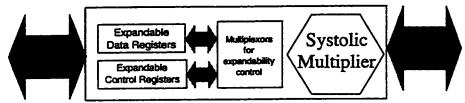

| 4.10 | The expandable serial MP implementation                         | 34 |

| 4.11 | Expandable shift registers design                               | 34 |

| 4.12 | The expandable MP system                                        | 35 |

|------|-----------------------------------------------------------------|----|

| 4.13 | The Montgomery modular exponentiation algorithm                 | 36 |

| 4.14 | The basic exponentiation processor                              | 36 |

| 4.15 | The expansion hardware                                          | 37 |

| 4.16 | The expanded MP module                                          | 38 |

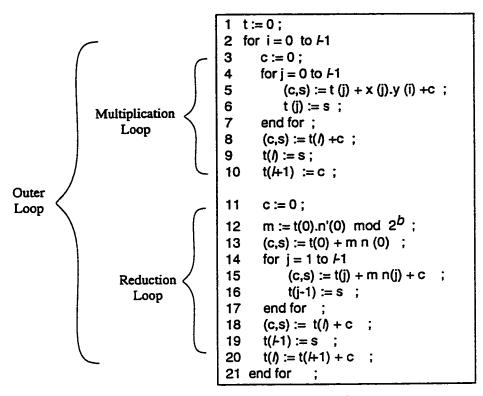

| 5.1  | The MP merged algorithm                                         | 40 |

| 5.2  | The reorganized MP merged algorithm                             | 41 |

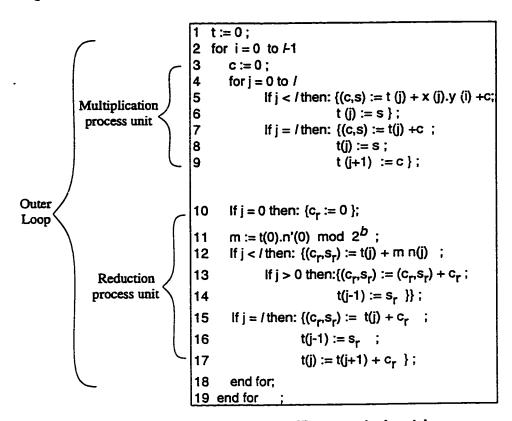

| 5.3  | The MP merged algorithm implementation model                    | 42 |

| 5.4  | The merged MP multiplier implementation                         | 43 |

| 5.5  | The multiplication process implementation outline               | 43 |

| 5.6  | The multiplication process implementation                       | 44 |

| 5.7  | The reduction process implementation                            | 45 |

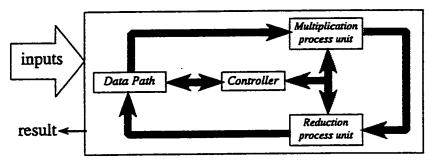

| 5.8  | The merged modular exponentiation hardware                      | 46 |

| 5.9  | The add/subtract modular multiplication hardware                | 47 |

| 5.10 | The add/subtract multiplication algorithm                       | 48 |

| 5.11 | The modular add/subtract reduction implementation               | 48 |

| 5.12 | The modular add/subtract multiplication implementation          | 49 |

| 5.13 | The modular exponentiation outline                              | 49 |

| 5.14 | The modular add/subtract exponentiation implementation          | 50 |

| 6.1  | The area of the designs for key size of 1024-bits               | 54 |

| 6.2  | The VHDL code of the parallel multiplier model                  | 58 |

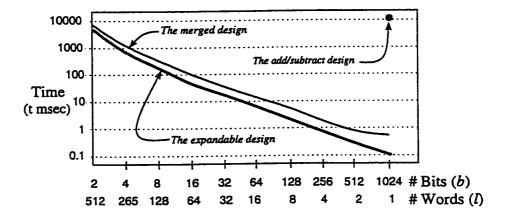

| 6.3  | The time vs. number of bits analysis                            | 59 |

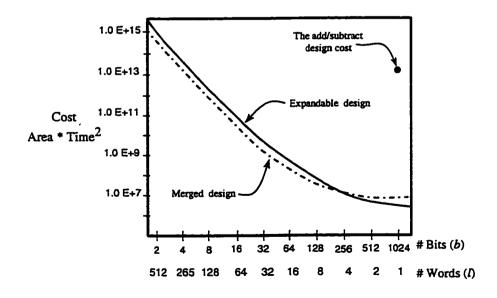

| 6.4  | The Cost (Area * Time²) analysis for key size of 1024-bits      | 61 |

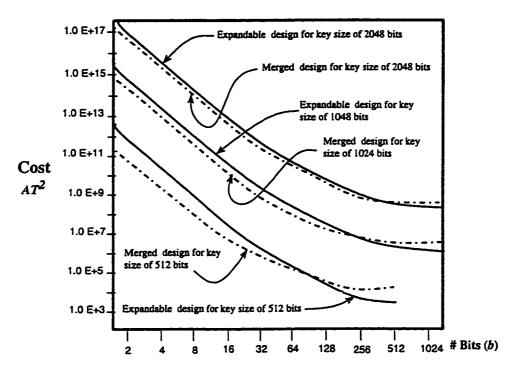

| 6.5  | The expandable and merged designs costs for different key sizes | 62 |

# List of Tables

| 6.1 | The number of transistors building the basic gates                     | 52 |

|-----|------------------------------------------------------------------------|----|

| 6.2 | The number of transistors building the basic components used           | 52 |

| 6.3 | Area (number of transistors) of the expandable RSA implementation .    | 53 |

| 6.4 | Area (number of transistors) of the merged exponentiation hardware     | 55 |

| 6.5 | Area (number of transistors) of the add/subtract exponentiation design | 56 |

| 6.6 | Analysis of the add/subtract modular exponentiation design             | 59 |

| 6.7 | Analysis of the merged Montgomery modular exponentiation design        | 60 |

| 6.8 | Analysis of the expandable modular exponentiation design               | 61 |

#### **Abstract**

Name:

Adnan Abdul-Aziz M. S. Gutub

Title:

A Hardware Model of an Expandable RSA Cryptographic System

Major Field: Computer Engineering

Date of Degree:

December 1998

Data security is an important aspect of information transmission and storage in an electronic form. Cryptographic systems are used to encrypt such information to guarantee its security. To retrieve such information, the encrypted form must be first decrypted. One of the most popular cryptographic systems is the RSA system. The security of the RSAencrypted information largely depends on the size of the used encryption key. The larger the key size is the longer the encryption/decryption time will be. To cope with the continuous demand for larger key sizes, faster hardware implementations of the RSA algorithm has become an active area of research. One disadvantage of hardware implementations is their fixed key sizes. If the key size is to be increased, the hardware design should be fully replaced.

The work reported here proposes an RSA hardware implementation that can be expanded as the key size gets larger. This implementation is modeled using VHDL in a parametrizable manner. Two other parameterized RSA hardware designs have also been VHDL modeled for comparison. The three models are compared for a 1024-bit key size and the results are analyzed. The complexity of the designs are compared and conclusions regarding optimal delay and area parameters are made.

#### Master of Science Degree

King Fahd University of Petroleum and Minerals Dhahran, Saudi Arabia December 1998

## بسو الله الرحمن الرحيم

# خلاصة الرسالة

الاسماعة عدنان بن عبدالعزيز بن محمد صديق قطب

عنوان الرسالة : تصميم دائرة إلكترونية دقيقة قابلة للتطوير حسب الحاجة لعمليـــة

التشفير بنظام RSA

التخصيص: هندسة الحاسب الآلي

تاريخ الشهادة: شعبان ١٩١٤هـ

التشفير (Cryptography) هو الأسلوب الأمثل لحماية المعلومات والحفاظ على سريتها. وأحد أنجح طرق التشفير المستخدمة يعرف بـــ(RSA) ، وهي الطريقة التي تعتمد على حجم مفتاح الشفرة لتعقيد استنباط الرسالة الأساسية في وقت قصير ، وتعاني طريقة (RSA) من سلبية في تصميمها بالدوائر الإلكترونية الدقيقة ، وهـــي أن الدوائر مصممة للتشفير بمفتاح ذو حجم معين ثابت ، لو تغير لأحتاج تغيير التصميم الإلكتروني بالكلية.

وقد تم في هذا البحث تصميم طريقة حديدة مبنية على فكرة تطوير الدائرة الإلكترونية الدقيقة حسب الحاجة، بحيث تم تمثيل هذا التصميم باستعمال نموذج محاكاة التصميم الإلكتروني باستخدام لغة (VHDL)، وقورن هذا النموذج بالتفصيل مع تصميمين آخرين أيضاً باستخدام (VHDL)، وأثبت التصميم المقترح تفوقاً في السرعة بالرغم من أنه يعتبر الأكبر مساحة.

وقد تم إحراء مقارنة بين التصاميم الثلاثة من حيث كفاءة الأداء والسرعة و التكلفة (التكلفة - المساحة × الســرعة)، وأظهر التصميم المقترح نتائج مقاربة لأفضل تصميم. واعتبرت زيادة التكلفة نوع من الثمن مقابل للمرونة المتوفرة في هذا التصميم والتي تجعله قابل للتطوير حسب حاحة المستخدم.

درجة الماجستير في العلوم جامعة الملك فهد للبترول والمعادن الظهران – المملكة العربية السعودية شعبان 1219هـ

# Chapter 1

## Introduction

Encryption is a well recognized technique for information protection. It is used effectively to protect sensitive data such as passwords that are stored in a computer as well as information transmitted through different communication media.

Encryption is the transformation of data into a form which is unreadable without a secret decryption key. Over the years, several encryption (or cryptographic) techniques have been used, however, most of them were not practical [10, 13].

Depending on the encryption/decryption key, cryptographic systems can be classified into two main categories: secret key cryptosystems and public key cryptosystems. The secret key cryptosystems uses one key for both encryption and decryption. Public key cryptosystems, however, use two different keys, one for encryption and the other for decryption.

The most popular public key method is the RSA [1, 6, 10, 11, 12]. The security of this method depends on the size of the key. The larger the key size is, the more secure the system will be [2]. More security, in this context, means that more computation time would be needed to hack the system. This largely depends on the implementation technology which is growing at a very fast rate.

RSA cryptographic systems can either be software or hardware implemented. Software implementations are typically very slow compared to hardware ones. Whereas software implementations are flexible allowing changes in the key size, hardware implementations lack such flexibility. For example, if the RSA key size is to be increased to improve security, the hardware must be redesigned.

#### 1.1 Thesis Objective

The objective of this Thesis is to design an expandable implementation of an RSA processor. The processor is to be designed in a bit-sliced manner, such that larger key sizes can be easily accommodated by merely adding more slices.

For proper evaluation of the proposed expandable implementation, a VHDL structural model is to be developed. This model will be used to verify and simulate the operation of the proposed design. Furthermore, other available RSA implementations are modeled using VHDL as well to be compared to the proposed expandable design in terms of area and speed.

#### 1.2 Thesis Outline

In the next chapter, a general review of cryptographic concepts is given. Some examples of traditional secret key cryptosystems are discussed. The public key RSA cryptosystem has been covered in more depth because of its simplicity and popularity.

In chapter 3, reported RSA hardware implementations are described. The emphasis, however, is on the design of a custom integrated circuit, to achieve the highest performance. Some general techniques for performing modular operations are briefly discussed.

In chapter 4, the design and operation of the proposed expandable RSA hardware is detailed.

Chapter 5, introduces two other hardware implementations. Both of which use the repeated squaring algorithm for modulo-exponentiation. However, the techniques used to compute modular multiplication are different. One implementation is based on Montgomery's method for modulo multiplication, while the other method performs the modulo multiplication through integrated addition and subtraction operations.

In chapter 6, the proposed expandable hardware is compared with the two other implementations on the basis of time, area and  $AT^2$  cost. The three implementations are analyzed for 1024-bit key size, and the results are compared.

Chapter 7, summarizes the results of this thesis work and provides some proposed future work in this area.

# Chapter 2

# Cryptographic Systems

#### 2.1 Introduction

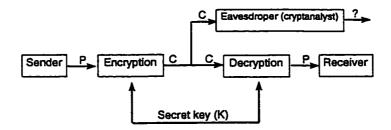

Cryptography is the science concerned with the process of encryption and decryption. The word, cryptography, is taken from the Greek word kryptos meaning hidden, and graphia meaning writing [6]. In data communication, for example, the original message is called the plain text 'P'. If this P is to be sent over an insecure channel it must be encrypted (Figure 2.1). The resulting text is referred to as the cipher text 'C'; sending C over an insecure channel protects the original message P against possible attacks of eavesdroppers. Encryption must be a reversible process, i.e. an inverse operation (decryption or deciphering) must exist to transform the encrypted information back to the original plain text [1].

The encryption algorithm is the procedure followed to encipher the plain text into

Figure 2.1: The information flow in a classical cryptographic system

its cipher form using a special number called the encryption/decryption key. This key is like a password to the encrypted message. Without knowledge of this key and the used algorithm, the cipher text can not be transformed back to the plain text. For this reason, the key must be transmitted to the receiver through a very secure channel (Figure 2.1).

Attempting to decrypt encrypted data without knowledge of the key is called cryptanalysis. A cryptographic system is secure [6], if the plain text "P" can not be obtained from the cipher text "C" through cryptanalysis.

Based on the type of cryptographic key used, cryptographic systems fall into two general categories; namely: secret key cryptography and public key cryptography. While the secret key category depends on using the same key for both encryption and decryption, public key cryptographic systems adopt a two-key system: one for encryption and another for decryption.

In the following, a number of traditional secret cryptographic systems will be briefly described. More detailed information can be found in the literature [4, 5, 8, 19].

#### 2.1.1 Substitution

This type of encryption replaces the actual bits, characters or blocks of characters with substitutes. For example, one letter replaces another, based on a certain rule. The first clearly documented substitution, known as Caesar's cipher [6], simply replaces a given letter from the plain text by the letter three places beyond it. Another substitution approach [1] replaces the letters (BWEKQFMVYALUCONPHSIDXTRGZJ) by the normal alphabet. Using this order of alphabet; say: "A" in the plain text is replaced by "B", "B" in the plain text is replaced by "W", "C" by "E", etc. Thus, if the plain text message is:

THE QUEEN HAS GIVEN BIRTH TO A HEALTHY SIX POUND BOY Then the cipher text [1] will be:

DVQ HXQQO VBI MYTQO WYSDV DN B VQBUDVZ IYG PNXOK WNZ

This type of cryptosystem can be cryptanalyzed by building frequency tables of letters, letter pairs and letter triples in the transmitted encrypted message and then comparing that to the well known English letter frequencies.

#### 2.1.2 Transposition

In this cryptosystem, the letters are permuted according to a certain rule. For example [1], the message:

THE QUEEN HAS GIVEN BIRTH TO A HEALTHY SIX POUND BOY is broken into five character groups (including spaces) and the letters in each group are rearranged according to the permutation:

so the third letter in the plain text is written first, the first letter is written second and the fifth letter is written third, and so on. The cipher text will be:

ETQ HEU NESHG AEI NVRBHTIO A TE LAHYTS H IOPXDUB NXOXXY

While substitution cryptosystems preserve the location of the letter in the message, but changes the letters themselves, transposition cryptosystems preserve the letters but their locations within the message are changed. Transposition can be broken by seeking permutations and rejoining them until the plain text is reconstructed.

### 2.2 Public Key Cryptosystems

Based on the type of cryptographic key used, cryptographic systems fall into two general categories; namely: secret key cryptography and public key cryptography. While the secret key category depends on using the same key for both encryption and decryption, public key cryptographic systems adopt a 2-key system: one for encryption and another for decryption. This method solves the key management and key distribution problems discussed before. Public key systems depend on some basic fundamental operators, two of which are discussed in the following section.

#### 2.2.1 Fundamental Operators

The security of public key cryptographic systems depends basically on the computational complexity of the encryption/decryption operation. With the exception of some assumptions made about the computational difficulty of the used operators, there is no concrete mathematical proof for the security of such systems [1]. These operators are the one-way and the trap-door functions. The existence of these operators is still considered an open research area [8, 9, 11].

#### One Way Functions

One way functions are functions that have no inverse function. For example, if M is a message, and F(M) is a function that generates the cipher text, C. F(M), is called a one-way function if M can not be regenerated from C by the use of the function F while F(M) itself, can be easily computed for any message M.

#### **Trap-Door Functions**

A trap-door function is a one-way function but with a unique inverse function  $F^{-1}$ , the trap-door. This unique inverse function  $F^{-1}$  is the only way to regenerate the function input M, given its output C. For example, the message M is the input to the function F(M), which will generate C. The only way to regenerate M back from C is through the trap-door function  $F^{-1}$ . Thus,

- If M and F are known, then C can be generated  $\Longrightarrow F(M) \equiv (C)$

- If C and  $F^{-1}$  are known, then M can be regenerated  $\Longrightarrow F^{-1}(C) \equiv (M)$

Some restrictions on trap-door functions must be taken into consideration [11]. These restrictions are:

- Both F and  $F^{-1}$  must be easy to compute for all needed values.

- Computing C from M without F is computationally infeasible.

- Computing  $F^{-1}$  from F, or F from  $F^{-1}$ , is computationally infeasible.

- Computing M from C without  $F^{-1}$  is computationally infeasible.

These two operators are the basic building blocks for public key cryptosystems.

#### 2.2.2 Historical Background

Diffie and Hellman in 1976 [12], suggested two solutions for the key distribution problem. These solutions laid the foundation for what is now known as the public key distribution system and the concept of public-key cryptosystems.

The first solution depends on the use of one-way functions. In this case, the sender and receiver exchange some one way function codes through which a secret cipher key is generated. These exchanged codes should prevent eavesdroppers from knowing or computing the secret ciphering key. By this method the key is distributed without a need for secure channels. This method is covered in more detailed fashion in the literature [1, 10, 11, 12].

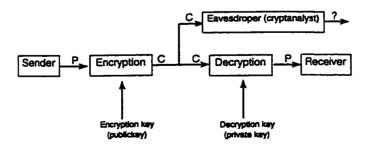

The second proposed solution, was a general conceptual model for general public-key cryptosystems. This model was given [1], without any practical example or implementation as shown in Figure 2.2. The main contribution was the notion that keys could come in pairs, one is a private key and the other is a public one. These keys should not be computable from one another following the trapdoor function. Thus, if any message is encrypted by one of the two keys, it can only be decrypted by the other key.

Figure 2.2: Public key cryptographic system (general concept)

Numerous public-key ciphering algorithms were, thereafter, proposed. However, many have been proven to be either insecure or impractical due to either the large size of the keys or the large size of the generated cipher text [10]. Only a few of these public-key algorithms have so far, been secure and practical. Some are suitable for encryption or key distribution, while others are more suitable for authentication and digital signatures. Three algorithms have been used both for encryption and digital signatures. These are the RSA algorithm, ElGamal algorithm and Rabin algorithm [10].

From a practical point of view, the major drawback of these three algorithms is their slow speed as compared to single key systems. A compromise solution for the speed problem is presented by merging the two methods, the public key cryptosystem for key distribution and the single key cryptosystems (e.g. DES), for message encryption. This hybrid approach has greatly improved system security as well as performance [11]. Hybrid cryptosystems, however, are not useful for all cryptographic applications, e.g. digital signature. Thus, speeding up the public key system is still a vital research area [1, 6, 12].

#### 2.3 The RSA System

In 1978, R. Rivest, A. Shamir and L. Adleman, came up with an algorithm which can be used for both encryption and digital signature. This algorithm was named RSA Cryptographic System [2], and is widely considered as the simplest public key algorithm [10]. This is due to its high security, relative simplicity and good performance. None of the other public key algorithms is as widely used as RSA [1, 10, 17].

RSA's security is based on the difficulty of the integer factoring problem, which is known to be a very hard problem to solve [8, 9]. The popularity of the method is due to the use of the same basic calculations of modular exponentiation for both encryption and decryption [11, 13].

#### 2.3.1 RSA Encryption

This system requires each user to have a public encryption key (e, n), and a private decryption key (d, n). To encrypt a message, it should be represented as a sequence of integers:  $m_1, m_2, m_3, \ldots$ , with each  $m_i$  being an integer in the range [0, n-1]. Each message block  $m_i$  is encrypted into a cipher text  $C_i$ , using the public key: (e, n) as follows:

$$C_i = E(m_i) = m_i^e \mod n$$

In order to retrieve the original message  $m_i$ , the private decryption key: (d, n), is used as follows:

$$m_i = D(C_i) = C_i^d \mod n$$

#### 2.3.2 Generation of the RSA Keys

Choose p and q as two random large primes [2]. Then, compute n as the product of p and q:  $n = p \times q$ . Note that n is made public, but its factors p and q are secret. Hiding p and q, hides the relation between d and e. Next, compute Euler's function:  $\phi(n) = (p-1)(q-1)$ . Then, choose e (the encryption key), such that e and  $\phi(n)$  are relatively prime, i.e.  $\gcd(e,\phi(n)) = 1$ . Finally, d (the decryption key), can be calculated by using the secret number  $\phi(n)$ , such that:

$$e \times d = 1 \mod \phi(n) = 1 \mod (p-1)(q-1)$$

It can be shown that d and n are also relatively prime integers [11].

From these calculations, we can conclude that the public encryption key is: e, n; and the private decryption key is: d, n.

#### 2.3.3 Example on Encryption Using RSA System

In the following example, sender A, wants to send the message: "HELLO" to receiver B. The sender needs to use the receiver's public key:(e, n), for encryption. To decrypt, receiver B, is required to use his private key: (d, n).

Receiver B, needs first to make the initial calculations for his public key: (e, n), and his private key: (d, n), as follows:

Let

$$p = 83$$

and  $q = 37 \implies n = p \times q = 83 \times 37 = 3071$

$$\phi(n) = (p-1)(q-1) = 82 \times 36 = 2952$$

$d = 709 \& e = 229$

such that:

$$e \times d = 229 \times 709 = 162361 \pmod{2952} = 1 \pmod{2952}$$

Accordingly, B's public key is: (229,3071), and his private key is: (709,3071).

Using the convention "A"=00, "B"=01, ...., "Z"=25, and "(blank space)"=26. Then, the message "HELLO" can be represented as: "07, 04, 11, 11, 14, 26". Taking the message blocks as:  $m_1 = 0704$ ,  $m_2 = 1111$ ,  $m_3 = 1426$ .

After that, the encryption key (229,3071) is used to compute:

$$C_1 = E(m_1) = m_1^e \mod n = (0704)^{229} \mod 3071 = 2443.$$

$$C_2 = E(m_2) = m_2^e \mod n = (1111)^{229} \mod 3071 = 1629.$$

$$C_3 = E(m_3) = m_3^e \mod n = (1426)^{229} \mod 3071 = 1556.$$

Thus, the cipher text to be sent by the sender A, will consist of the following sequence: "24, 43, 16, 29, 15, 56".

The receiver's private key: (709,3071), is the only way to retrieve the message from the cipher text. So to regenerate the plain text the receiver B needs to compute:

$$m_1 = D(C_1) = C_1^d \mod n = (2443)^{709} \mod 3071 = 704.$$

$$m_2 = D(C_2) = C_2^d \mod n = (1629)^{709} \mod 3071 = 1111.$$

$$m_3 = D(C_3) = C_3^d \mod n = (1556)^{709} \mod 3071 = 1426.$$

As observed, the plain text "07, 04, 11, 11, 14, 26", is regenerated again representing the message "HELLO".

#### 2.3.4 The RSA Digital Signature Scheme

The RSA algorithm can be used as a digital signature scheme as well. For example, if user A needs to send a signed message to another user B, he (user A) will use his own private key to compute S as follows:

$$S = D(m) = m^d mod n$$

User A will then send S, for B to verify A's signature. To do this he needs to use A's public key; as the following calculation:

$$E(S) = E(D(m)) = (D(m))^e \mod n = (m^d \mod n)^e \mod n = m^{de} \mod n = m$$

This will generate the message m, only if user A has signed it and the message had not been tampered with [2, 10, 11, 12].

#### 2.3.5 Security of the RSA Cryptosystem

Decryption of RSA-encrypted messages by cryptanalsis is as difficult as factoring a large number into its prime factors. An advice by Rivest [2], was to use at least a 100-digit integer for both p and q. This will let n have 200-digits or even more. Large size keys, however, result in slower encryption and decryption.

#### 2.3.6 RSA Speed

Some techniques are proposed to improve the speed of software RSA systems [12]. However, these techniques are still slower than hardware implementations [21]. Compared to private key systems, e.g. DES, the RSA is much slower. The fastest reported hardware has a throughput which is 1000 times slower than what has been reported for the DES system [10]. Hardware speed, however, can be further improved by improvement in the technology used for hardware designs. More information regarding RSA hardware implementations is given in the next chapter.

#### 2.4 Summary

In this chapter, a general review of cryptographic concepts is given. Some examples of traditional secret key cryptosystems are discussed. The public key RSA cryptosystem has been covered in more depth because of its simplicity and popularity.

# Chapter 3

# Review of RSA Hardware Implementations

#### 3.1 Introduction

Efforts to Implement public key systems in hardware began in the late 1970's. These early designs, however, were not practical because of their high cost, low speed and inflexibility. In the past decade, however, implementing public key systems in hardware has changed due to several factors [50, 51]. The most important factor is the tremendous progress in technology. Millions of transistors can now be fit onto a single chip. Another important factor is the tremendous increase in the number of computer communication networks, e.g. the internet. Security of transactions conducted across a network has become a vital issue to the reliability and success of these networks. Public key cryptography plays an important role in this regard.

The RSA encryption algorithm is considered the most practical public key system in use due to its high security and acceptable complexity compared to other public-key techniques [1, 2, 10, 17]. Several hardware approaches for implementing the RSA algorithm have been proposed [21, 23, 25, 29, 31, 42, 43, 44, 46, 47]. One approach uses available digital signal processors (DSP) [25, 26], for this purpose. Another approach

uses several active memory chips programmed to perform the RSA algorithm [22].

An important implementation strategy is the design of custom integrated circuits that are capable of performing the required modular operations. Since this offers the best performance, our work will concentrate on this particular approach.

In 1989, E. Brickell [21], published a survey of hardware implementations of the RSA algorithm. Ten different implementations were covered in this survey and their encryption speeds were compared. However, such comparison is somewhat misleading due to the differences in the fabrication technology of the different implementations.

Since the key RSA operation is the modular multiplication or more accurately the modular exponentiation, different methods were developed to implement these modulo computations. In the following section, some such methods are discussed.

#### 3.2 General Techniques for Modular Operations

#### 3.2.1 The Repeated Squaring Algorithm

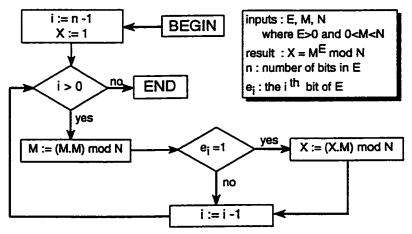

Figure 3.1: The repeated squaring algorithm

Modular exponentiation can be computed through a set of iterative modular multiplications or through a set of repeated squarings [21, 32, 33, 42]. The repeated squaring algorithm is mainly performed by repeating modular multiplication a number of times as the number of bits of the exponent. The bits of the exponent should be scanned

starting with the MSB (most significant bit). Whenever it is '1' a further modular multiplication is to be performed, as illustrated in Figure 3.1.

The bits of the exponent if scanned with the LSB (least significant bit) first, allows for about 30% improvement in the average speed through the use of parallelism of the modular multiplication processes [43, 46, 47]. This improved approach is shown in Figure 3.2.

Figure 3.2: The improved repeated squaring algorithm

#### 3.2.2 General Modular Multiplication Techniques

Modular multiplication can be implemented in different ways. Residue number systems, for example, have been recently receiving more attention [34, 41]. Reported implementations, however, have ignored important hardware implementation issues particularly the need for conversion between binary and residue numbers. This has discouraged researchers from using such an approach [35].

The straight-forward approach to compute modular multiplication is by performing the multiplication and then subtracting the modulus several times until the result is less than the modulus. This approach is inefficient and suffers from low speed. This can, however, be improved by merging the modulo subtraction with the multiplication add operations [43, 46, 47], as outlined in Figure 3.3.

Another approach is based on look-up tables, i.e. ROM-based methods [37]. This method, however, is quite expensive since the required memory space grows exponentially with the word size [35].

Figure 3.3: The multiplication with reduction modified algorithm

In 1991, G. Alia and E. Martinelli [36], came up with a new method to compute modulo multiplication. They found that their method is optimal to implement using few fast VLSI binary-multipliers, compared with ROM-based methods.

An improved look-up table method was proposed by C. Wu and Y. Chon in 1994 [35]. This method depends on the use of look-up tables by specially designed block multipliers, which are designed as a bit-parallel multiplier and a bit-serial one. It is partly parallel and partly serial to get the advantages of both techniques. The parallel multiplier results in high throughput rate and the serial help reduce power consumption. The computing speed and the area of this modular multiplier is dominated by the used adders [35].

In 1994, C. D. Walter [39], proposed a logarithmic speed modular multiplication al-

gorithm. This algorithm and its implementation will be covered briefly in the following section.

In 1985, Peter Montgomery [24], proposed a new method for modular reduction without regular division. His method was found to be fast [23, 24, 28], and suitable for hardware designs [27, 29, 30, 31]. Montgomery's multiplication method has been widely adopted for use in exponential RSA implementation. Elaboration of Montgomery's algorithm will be given later this chapter.

#### 3.3 Logarithmic Speed Implementation

A logarithmic speed modular multiplication hardware is proposed by C. D. Walter [39]. It performs each modular multiplication for n - digit inputs in O(log n) time.

#### 3.3.1 The Algorithm

The algorithm used for this implementation divides the operation of  $(A \times B) \mod N$  into six computational steps as follows:

- 1. compute:  $A \times B$ ;

- 2. compute: 1/N;

- 3. compute:  $(A \times B) \times (1/N)$

- 4. compute:  $fract((A \times B) \times (1/N))$ ; (fract discards the integer part of a real number and returns the non-negative fractional part.)

- 5. compute:  $N \times (fract((A \times B) \times (1/N)));$

- 6. compute:  $rnd[N \times (fract[(A \times B) \times (1/N)])]$ ; (rnd rounds the real number to the nearest integer.)

#### 3.3.2 The Implementation

The three multiplication processes are computed sequentially on the same hardware, with one clock cycle per multiplication process. Each multiplication process is performed as repeated additions using the Wallace tree structure [48]. The reported critical path for a 512-bit multiplication process, contains around 40 XOR-gates. With three required multiplications (steps: 1, 3 and 5 of the algorithm), a total of 120 XOR-gates delay is required for the three clock cycles needed. Note that step-2 of the algorithm, computing (1/N), is assumed to be precomputed by software.

The reported area needed to construct such logarithmic time implementation for 512-bit numbers, is equivalent to  $5 \times 10^6$  XOR gates [39]. In fact, this design stretches current technology to the limit, but provides a great improvement in speed.

#### 3.4 Implementations of Montgomery's Algorithm

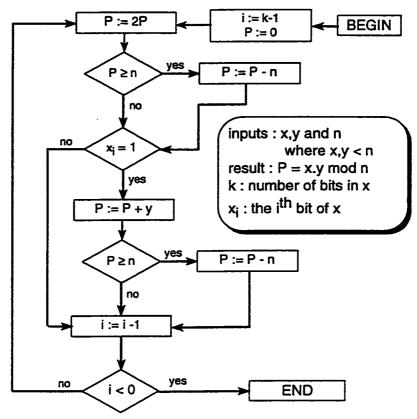

#### 3.4.1 Montgomery's Algorithm For Exponentiation

Figure 3.4: Montgomery's algorithm for modular exponentiation

For the RSA method, the problem to be solved is:  $x = a^e \mod N$ . Montgomery's technique will compute x without trial division. Figure 3.4, shows the steps to be followed to perform this operation. Note that the  $\mod R$  and division by R operations, in the Montgomery modular multiplication procedure, can be inexpensively computed since  $R = 2^k$ .

#### 3.4.2 Montgomery's Algorithm Hardware Designs

S. E. Eldridge and C. D. Walter [29], studied Montgomery's modular multiplication algorithm and proposed a hardware implementation for it. They compared Montgomery's method with earlier reported techniques and concluded that Montgomery's algorithm is better suited for implementation. Based on this, they designed a faster hardware which doubled the overall speed for the same number of clock cycles. Their design, however, is practical only for moduli up to 1000-bits in length which is considered as a design limitation. Their implementation is constructed using a tree structure of repeated units of adders that perform the multiplication process as repeated addition. This hardware model has a bottleneck of broadcasting the quotient digits throughout the design [28].

C. D. Walter [28], further improved the previous design. The limitation on the modulus was completely removed and the critical path was simplified to solve the problem of broadcasting data all-over the hardware. This design [28], performs each modular multiplication process for n-digits in  $O(n + \log n)$  time, which is slower than the logarithmic speed implementation [39], proposed by the same author, as briefly described in the previous section.

A systolic array for modular multiplication using Montgomery's algorithm was described by C. D. Walter in 1993 [27]. For n-digit operands, this implementation requires 2n+2 clock cycles for the first output digit to appear after the first input digit is fed to the systolic array. The implementation is constructed as a two-dimensional array of  $n^2$  cells. All cells are identical except for the cells on the rightmost column which do not generate output digits. Each such cell performs two multiplications and three additions, which required five XOR-gates, seven AND-gates, and two OR-gates, assuming binary numbers representation.

For RSA applications, typical inputs have at least 500-bits. The number of cells required is at least  $500^2$ , or about  $4 \times 10^6$  gates. This large area stretches today's technology to the limit.

#### 3.5 Full RSA Implementations

Many RSA implementations have been proposed in the literature [21, 23, 24, 31, 42, 43, 44, 46, 47]. This is mainly due to the difficulty of obtaining high speeds at reasonably reduced hardware cost. Furthermore, most of the reported implementations do not provide enough information on the design details, e.g. [21, 27, 28, 35, 39, 44, 45].

H. Orup, E. Svendsen and E. Andreasen [47], presented an efficient RSA hardware implementation called VICTOR, where they improved some earlier algorithms. The modular exponentiation technique used is similar to the modified repeated squaring algorithm shown in Figure 3.2.

The hardware processor proposed by F. al-Twaijry and S. Barton [46], describes some techniques to speed-up the central computational process in the RSA algorithm. Assuming that k is the maximum number of bits available for the RSA operations, the time-consuming modular multiplication operation can be performed by a complete integer multiplication of two k-bits numbers followed by modulo reduction of the resulting 2k-bit product. In this design [46], however, modulo reduction is performed at each step of the multiplication process as shown in Figure 3.3, such that the result never grows beyond k + 1 bits. This design modification resulted in a reported 56% increase in speed. The area of this high speed design [46], is the major drawback of such an approach.

Another RSA implementation, proposed by Jorg Sauerbrey [31], uses a systolic hardware for modular exponentiation using Montgomery's algorithm. Since our work targeted the design of an expandable RSA processor, the work of Sauerbrey seemed to be a logical starting model for such a design. Modeling the implementation reported by Sauerbrey has revealed that his design had a major flaw which makes it incorrect. Details of that are clarified in the following section.

#### 3.6 Systolic Arrays for Modular Exponentiation

In 1992, Jorg Sauerbrey [31], reported a systolic array hardware design that performs modular exponentiation. This design uses two identical systolic arrays to build the basic multiplier which can handle multi-bits operands.

#### 3.6.1 Systolic Array for Multiplication

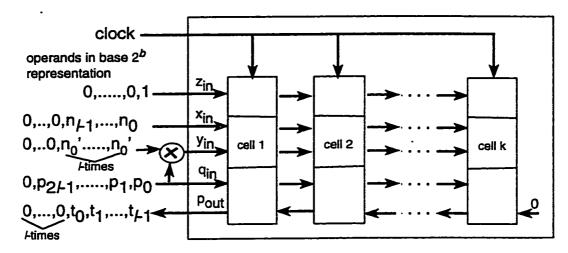

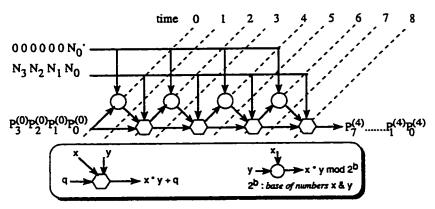

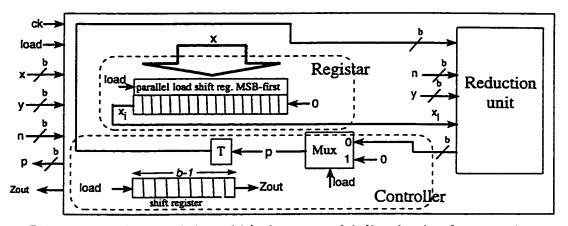

The systolic array consists of a set of identical cells that can process numbers in base  $2^b$ , where b is the number of bits per word. The message M, is divided into l-words, each representing a digit of b-bits. The minimum number of cells required to process the l-digits is  $= \lceil l/2 \rceil + 1$ .

The l-digits of the message M requires 2l-clock cycles to complete the multiplication process. During the first l-clock cycles, digits of the two operands are fed serially to the systolic array with the least significant digit being fed first.

The 2*l*-digits of the product will be produced serially one digit per clock cycle starting with the least significant digit. Accordingly, each multiplication process requires 2*l*-clock cycles. Whereas the *l*-digits of the two input operands are fed during the first *l* clock cycles, zeros are fed in the second *l*-clock cycles.

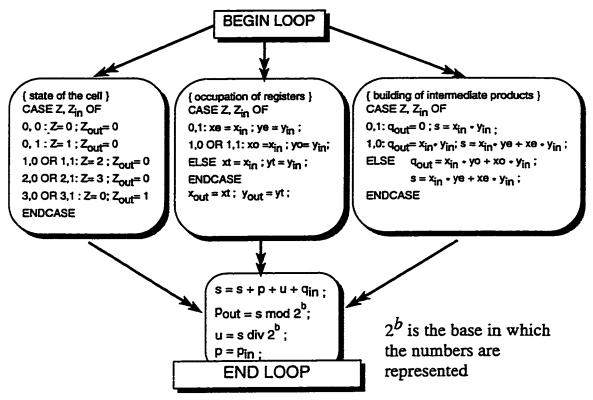

Figure 3.5 shows the interconnection and the input of the array when performing the operation:  $p = x \cdot y + q$ . The control input z signals the start of the multiplication process. The behavior of each cell is described by the algorithm shown in Figure 3.6.

Figure 3.5: The systolic array

Figure 3.6: The algorithm for a cell behavior

#### 3.6.2 Montgomery Reduction by the Systolic Multiplier

Montgomery's reduction algorithm for the modular multiplication is:

$$MP(x,y,n,r) = x.y.r^{-1} \bmod n$$

The algorithm can be rewritten to allow digit-wise processing of large operands as follows:

(Note that x, y < n < r,  $r = 2^{kl}$  and gcd(r, n) = 1)

- 1.  $n'_0 \leftarrow -n^{-1} \mod 2^b$

- 2.  $p \leftarrow x.y$

- 3. for i = 0 to l 1 do

- 4. begin

- 5.  $v_i \leftarrow p_i.n'_0 \mod 2^b \ (p_i \text{ is the } i^{th} \text{ digit of the resulting product } p)$

- 6.  $p \leftarrow p + v_i.n.2^{bi}$

- 7. end

- 8. return p/r; (if p/r < n) else return p/r n

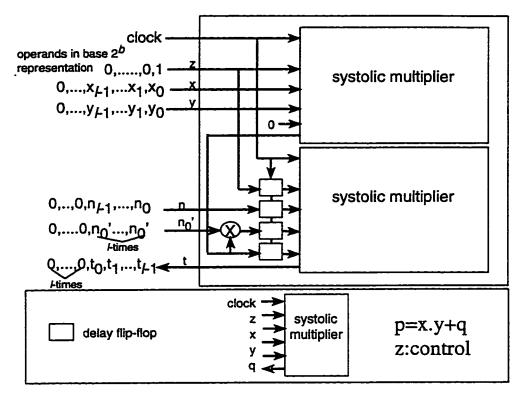

Figure 3.7: The systolic Montgomery reduction

The systolic multiplier performs steps 3 to 7, of the above Montgomery-reduction algorithm. The rest of the algorithm is computed only once, and can thus be computed by a software program. It is assumed that the product digits  $p_i$  are available serially, and that the factor  $n'_0$  has already been calculated. In this case,  $v_i$  is computed by a single multiplier as shown in Figure 3.7. The systolic multiplier receives this product  $(v_i)$  and computes step-6, of the Montgomery-reduction algorithm.

According to the algorithm (step-6), p is modified l-times throughout the for-Loop (steps 3 to 7). The implementation proposed by Sauerbrey [31], which is shown in Figure 3.7, does not allow p to be updated as required by the algorithm, and accordingly does not produce correct results. This has been confirmed by VHDL model simulation.

In conclusion, the output of the systolic hardware as shown in Figure 3.7, does not match the MP-algorithm stated above. Sauerbrey [31], has proposed a complete Montgomery modular multiplier based on the hardware described in Figure 3.7. This design is built from two systolic multipliers as shown in Figure 3.8. The first systolic multiplier computes the product x.y (step 2 of the Montgomery-reduction algorithm). The computed product is delayed by one clock cycle and is used as p in steps 5 and 6 in the Montgomery algorithm.

To get the correct result, the  $p_i$  used in step 5 must be the one computed by step-6 of the previous loop iteration.

Figure 3.8: Sauerbrey's implementation of Montgomery modular multiplication

#### 3.7 Summary

Several reported implementations of RSA-related hardware have been reviewed. Some are for modular exponentiation, e.g.[31, 46, 47], while others are for modular multiplication, e.g.[27, 39], which is the most time consuming process in the RSA algorithm.

The major operation in the RSA method is the modulo exponentiation which is computed by the repeated squaring algorithm. This repeated squaring algorithm can be improved [46, 47], to perform the required two multiplications in parallel.

Different techniques have been used to calculate modular multiplication. One such technique uses standard integer multiplication followed by a modulo reduction, which is a time consuming process [43]. Merging the modulo reduction with the multiplication can speed-up the process, e.g. [43, 46, 47].

Another modular multiplication method has a logarithmic speed [39], but it uses a very costly hardware. The algorithm used for the computation of  $x \times y \pmod{n}$ , is:  $rnd (fract((x \times y) \times (1/n)) \times n)$ . Assuming that (1/n) is precomputed, this implementation must perform three multiplications in sequence; first,  $(x \times y)$ , then  $(x \times y) \times (1/n)$ , and finally  $(fract(x \times y) \times (1/n)) \times n$ . Note that the function: fract discards the integer part of a real number and returns the non-negative fractional part; and the function: rnd rounds the real number to the nearest integer.

A third modular multiplication technique is developed by P. Montgomery [24]. This technique has been widely used for RSA hardware [23, 27, 28, 29, 30, 31], because of its practical speed and relative simplicity for VLSI implementation [24]. The hardware using Montgomery's modular multiplication [27, 31], is required to perform two multiplications and one addition.

Several reported full RSA designs have been introduced. Detailed investigation of the systolic hardware implementation proposed by J. Sauerbrey has found it to be incorrect. Our thesis work is concentrated on finding a way to make an expandable hardware. This seemed to be feasible using systolic arrays, such as the systolic hardware proposed by J. Sauerbrey [31] (using Montgomery's algorithm for modular multiplication). However, Sauerbrey's systolic implementation needs to be corrected and modified for expandability.

# Chapter 4

# A Hardware Model of an Expandable RSA Cryptographic System

#### 4.1 Introduction

The security of the RSA cryptographic system depends on the encryption and decryption key size. As the key size increases the security of the system is improved [2]. All RSA hardware implementations, as reported in the previous chapter, are designed to accommodate fixed key sizes. If larger key sizes are needed the hardware must be redesigned.

One of the goals of this work, is to develop an expandable RSA implementation where duplication of well defined bit-sliced hardware will adapt the system to larger key sizes. To incorporate such flexibility, hardware and performance overheads are expected. The proposed expandable RSA system depends mainly on the systolic multiplier used by Sauerbrey [31]. This model has been redesigned and modified for expandability.

In the following, the basic systolic multiplier is described and the Montgomery product algorithm with its implementation as well as modifications for expandability are detailed. Next, modular exponentiation hardware is described and the architecture of the expandable chip is given.

#### 4.2 The Systolic Multiplier

Figure 4.1: The word-serial multiplier (systolic array)

The systolic multiplier is made of a set of cascaded identical cells connected as shown in Figure 4.1. This systolic multiplier can perform the operation:  $p = x \cdot y + q$ , in a word-serial manner. If x, y and q have l-words, where each word represents a digit in base  $2^b$ , the time required for a complete operation is 2l clock cycles [31]. Note that the base can be any power of 2 number, and b is the number of bits in each word. The input z of the systolic multiplier is a control signal which indicates the beginning of the operation. To multiply two operands of l-words, the number of cells required by the systolic multiplier is  $\lceil l/2 \rceil + 1 \rceil = 1$ .

This systolic multiplier is chosen because of its expandable capability. Figure 4.1, shows a multiplier for *l*-digit numbers. If the numbers to be multiplied are increased in size to 2*l*-digits, the only required modification on the design is to add another identical systolic multiplier in cascade, as shown in Figure 4.2. Clarification and modeling of each cell in the

Figure 4.2: Expandability of the systolic multiplier

systolic multiplier is given in the following subsection.

#### 4.2.1 The Basic Cell of The Systolic Multiplier

Figure 4.3: Hardware design of the cell

The basic cell of the systolic multiplier is designed to perform the algorithm shown in Figure 3.6. This design is mainly built up from the following:

- Four b-bit parallel multipliers.

- Three adders.

- Ten different registers.

- Two multiplexers.

- Some simple gates: ten AND gates, two OR gates and an XOR gate.

The b-bit parallel multipliers are needed to compute the intermediate products required at each cell. More information about the b-bit parallel multiplier is given in the following subsection.

The registers used in the cell are enable-high positive edge triggered, i.e. if the enable function (en) is high, the register will load data at the rising edge of the clock. The registers in the cell (Figure 4.3) are classified into three types according to their size. The first type is single bit registers, e.g. Z2 and Z1, which control the state of the cell. The second type is b-bit registers, where b is the number of bits in each word. There are seven registers of this type: xe, ye, xo, yo, xt, yt and p. The last type of registers has (b+2)-bits, e.g. u. The extra 2-bits are added to account for the carry after addition, e.g. S-out:=S+qin+u+p.

#### 4.2.2 The b-bit Parallel Multiplier

Each cell of the systolic multiplier has four parallel multipliers that perform the required multiplications for that specific cell. Each parallel multiplier is designed to multiply two words, of b-bits each, in parallel. Figure 4.4, shows an example of such parallel multiplier for 4-bit words.

The complexity of the parallel multiplier varies depending on the size of the word (b). In general, the required multiplier hardware can be stated as function of the word size (b), as follows:

- 1.  $b^2$  2-input AND gates.

- b Half-adders.

each half-adder is constructed using an XOR gate and an AND gate.

- 3.  $b^2 2b$  Full-adders. each full-adder is constructed using two XOR gates, two AND gates and an OR gate.

#### 4.3 Montgomery Product Design

Peter Montgomery [24] in 1985, came up with a smart method to compute modular multiplication without trial division. His method to compute: $z = x.y \mod N$ , can be summarized in the following:

1. Choose R > N such that  $R = 2^k$ , where k is the number of bits in N, accordingly R is relatively prime to N.

Figure 4.4: Hardware design of 4-bits parallel multiplier

- 2. Transform x and y to x' and y' (Montgomery's-representation), where  $x' = xR \mod N$  and  $y' = yR \mod N$ .

- 3. Calculate Montgomery-product :  $z' = MP(x', y') = x'y'R^{-1} \mod N$ .

- 4. Transform z' to the normal representation z, i.e.  $z = z'R^{-1} \mod N$ .

Steps 1, 2 and 4 can be calculated through a software program since they need to be computed only once. However, step 3, i.e. MP(x',y') is repeated to perform exponentiation and it can be calculated as follows:

- 1.  $P = x' \times y'$ ;

- 2.  $U = P + N \times (P \times N' \mod R)$ ;

- 3. S = U/R;

- 4.  $MP = S \ (if \ S < N)$  or  $MP = S N \ (if \ S \ge N);$

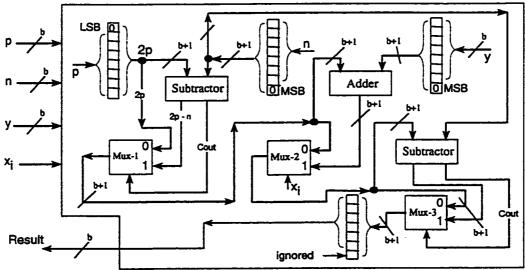

By choosing R to be a power of 2 number  $(R = 2^k)$ ,  $mod\ R$  and division by R operations can be computed inexpensively. This method to compute MP(x',y') can be organized in a serial manner, as shown in Figure 4.5. This algorithm is well-suited for a systolic multiplier implementation similar to the one described in the previous section.

Figure 4.5: The MP-algorithm (Montgomery Product)

#### 4.3.1 Montgomery Product Implementation

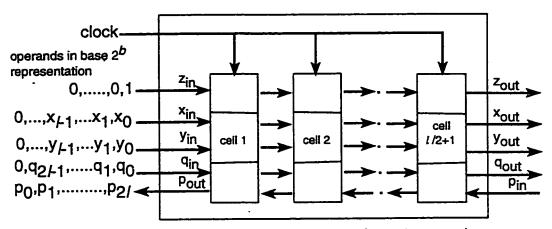

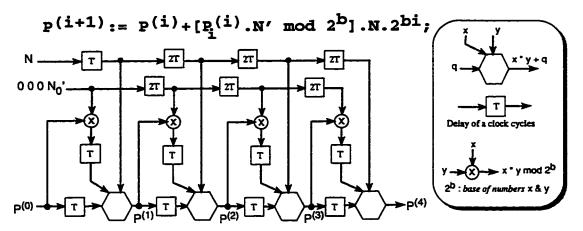

To implement the Montgomery product algorithm (Figure 4.5) using the systolic multiplier shown in Figure 4.1, a signal flow graph is developed to describe the flow of data. The signal flow graph for a 4-word number is shown in Figure 4.6.

Note that two types of processors are required, one is a parallel multiplier, and the other is a systolic multiplier. The output starts coming out after 2l clock cycles. However, the first l-digits of the output will be discarded to account for the division by R, and accordingly the MP result will be serially computed after 3l clock cycles.

The hardware implementation derived from the signal flow graph (for l=4 words) is shown in Figure 4.7. The full MP result will be available after 4l clock cycles. Two types

Figure 4.6: The signal flow graph

of registers are used for proper data synchronization: T and 2T, which delay data by one and two clock cycles respectively. The overall number of registers required for an l-words design is (6l-3). The number of parallel multipliers used is l, while the number of systolic multipliers used is l+1. The extra systolic multiplier is not shown in Figure 4.7, but it is necessary to compute  $p^{(0)}$ .

Figure 4.7: The signal flow graph MP implementation (parallel hardware)

#### 4.3.2 Expandability of the parallel MP Implementation

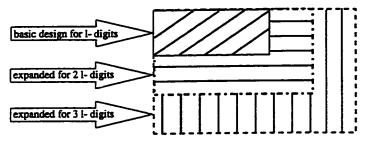

To expand the design shown in Figure 4.7, not only should the number of systolic multipliers be increased, but also the size of each systolic multiplier must increase. This is due to the fact that the number of cascaded stages of the systolic multipliers depends on the number of words (l). Thus, such design does not allow regular linear expandability.

For example, if the design needs to be expanded to handle 2*l*-words, the expansion is performed in both horizontal and vertical directions. The horizontal expansion is to let the number of systolic multipliers increase to 2*l*, while the vertical expansion is to add hardware to each systelic multiplier to accommodate 2*l*-words instead of *l*. Thus, expandability for such architecture is not linear (Figure 4.8). This makes developing a standard expandable chip, using this approach, unachievable.

Figure 4.8: Expandability of the parallel implementation

#### 4.3.3 The Expandable MP Design

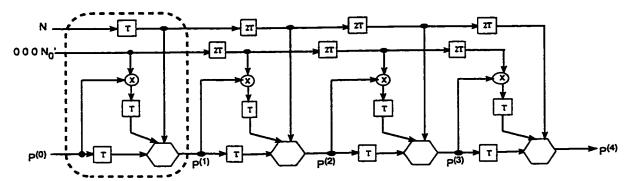

For linear regular expandability of the MP implementation, the design must be reorganized for serial instead of parallel processing. This can be achieved by projecting all systolic multipliers into one and projecting all parallel multipliers into one, i.e. using only one parallel multiplier and one systolic multiplier for the whole process as shown in Figure 4.9.

Figure 4.9: Projecting all parallel and systolic multipliers into one

The following example clarifies this idea. Assuming that l = 4-words, and  $p^{(0)}$  is precomputed, let the words of  $p^{(0)}$  be fed in a word-serial manner to the projected processor and the outputs be saved in an output register, as shown in Figure 4.10. After 2l clock cycles all words of  $p^{(1)}$  will be available in the output register. Then,  $p^{(1)}$  is serially fed to the processor with the other inputs N and  $N'_0$ , properly synchronized. After additional 2l clock cycles, all digits of  $p^{(2)}$  will be available in the output register. Likewise,  $p^{(3)}$  and  $p^{(4)}$  are computed using the same procedure allowing 2l clock cycles for each.

The time required for each  $p^{(i+1)}$  to be available at the output register is 2l+1 clock cycles, including an extra cycle for proper synchronization. The digits of N must be synchronized to those of  $p^{(i)}$  and delayed by two more clock cycles. The single word  $V_i$  (Figure 4.5) is calculated using a parallel multiplier to multiply  $N'_0$  with  $p_i^{(i)}$ , and discarding the most

Figure 4.10: The expandable serial MP implementation

significant word.

Figure 4.10, assumes that p<sup>(0)</sup> is already computed. However, to compute p<sup>(0)</sup> with the same hardware, additional multiplexors should be added in the controller and more time is required to complete the process.

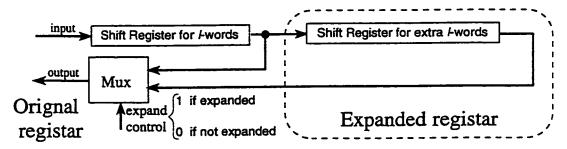

To allow for expandability, the controller is organized using shift registers and multiplexors, to make the registers expandable, as shown in Figure 4.11. The systolic multiplier is made expandable by passing its cascading signals as external interface signals as shown in Figure 4.2.

Figure 4.11: Expandable shift registers design

Note that the basic processor chip differs from its expansion. In the expansion chip, the b-bit parallel multiplier and some registers are not needed. Thus, the complete design can be organized as the basic MP-processor and any number of expanded processors depending on the required key size, as shown in Figure 4.12. The basic MP-processor for a key size of l-digits, consists of the following:

#### • A systolic multiplier

- Ten multiplexers in the data processor

- Three registers of b-bits in the data processor

- A parallel multiplier

- Seven multiplexers in the controller

- Six registers of b-bits in the controller

The expanded MP-hardware for an added l-digits consists of the following:

- A systolic multiplier

- nine multiplexers

- nine registers of b-bits

For a key size of l-digits, the overall time required for completing the MP-process and start getting MP output is:  $(2l+1)(l+1) = 2l^2 + 3l + 1$  clock cycles.

Figure 4.12: The expandable MP system

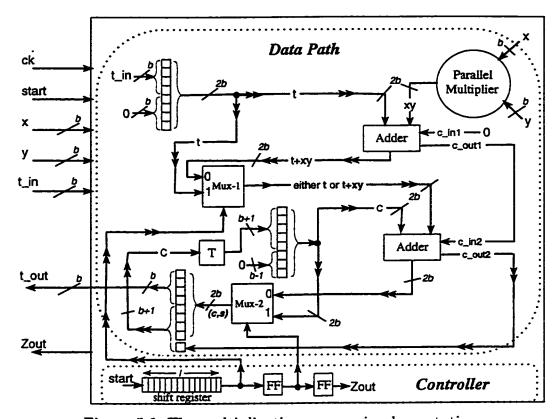

#### 4.4 The Modular Exponentiation System

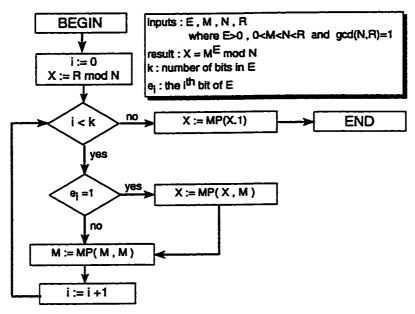

The modular exponentiation system uses the improved repeated squaring algorithm shown in Figure 3.2. This algorithm can perform the two required modular multiplications in parallel. It is also applicable for the Montgomery modular multiplication with some additional pre-computations. These pre-computations transform the numbers from its ordinary representation to Montgomery's representation. The algorithm used for Montgomery modular exponentiation is shown in Figure 4.13. Note that the initial computation of X is to be computed in software. The rest of the algorithm is more efficiently performed in hardware because of the excessive number of required repetitions.

Figure 4.13: The Montgomery modular exponentiation algorithm

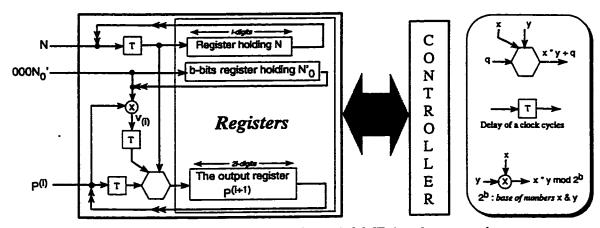

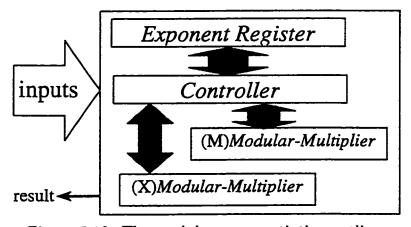

#### 4.4.1 The Basic Exponentiation Processor

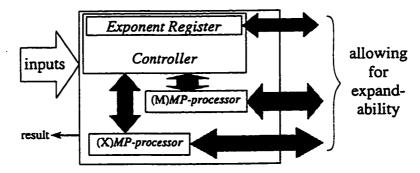

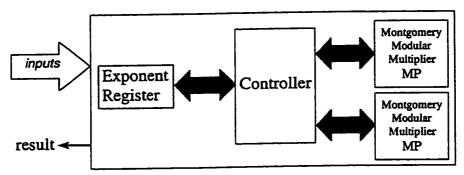

For highest speed, the algorithm shown in Figure 4.13, is implemented using two MP-processors to compute: X and M in parallel. A controller is built up of eleven multiplexers and a register to hold the bits of the exponent E. One multiplexer is used to control the MP-processor updating the X-value, depending on the values of the exponent bits. Nine other multiplexors are used for the reason of loading and processing data. One more multiplexer is needed for allowing expansion of the register holding the exponent E.

The basic blocks of the exponentiation processor are shown in Figure 4.14. If the basic processor is to be expanded, an expansion unit is designed to be connected to it. Note that the controller, of the basic processor, is expanded by only expanding the exponent register.

Figure 4.14: The basic exponentiation processor

#### 4.4.2 The Expansion hardware

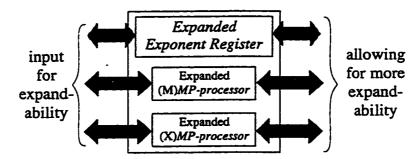

Figure 4.15, shows the proposed expansion chip when the number of digits is to be doubled. For example, if the basic chip can handle *l*-words, adding this expansion hardware will allow processing of 2*l*-words; i.e. each added expanded chip will let the design accommodate an additional *l*-words.

Figure 4.15: The expansion hardware

Each expansion hardware incorporates two expandable MP processors and a register to accommodate the expandability of the exponent, as shown in Figure 4.15. The two expandable MP modules are completely identical and will be clarified in the following subsection.

#### 4.4.3 The Expandable MP Module

The idea of expandability is mainly that of expanding the systolic multiplier and expanding the registers. Expanding the systolic multiplier is performed by adding another systolic multiplier with  $\lceil l/2 \rceil$  cells to accommodate the multiplication of numbers with 2l-words, as shown in Figure 4.2. Expanding the registers is performed by adding more shift registers as shown in Figure 4.11.

For the expandable MP module, four additional registers are required for the data path and five are needed for the controller. These nine registers require nine multiplexors to allow for further expandability, as shown in Figure 4.16.

#### 4.5 Summary

In this chapter, a new hardware model of an expandable RSA cryptographic system is proposed. The new hardware corrects the problem in the design reported by Sauerbrey [31],

Figure 4.16: The expanded MP module

in addition to allowing for its expandability. Targeting the maximum possible speed, the used exponentiation algorithm allows parallel computation of two Montgomery product at the expense of added hardware.

# Chapter 5

# Other Implementations

#### 5.1 Introduction

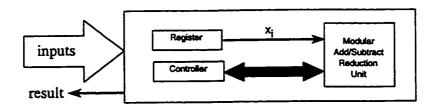

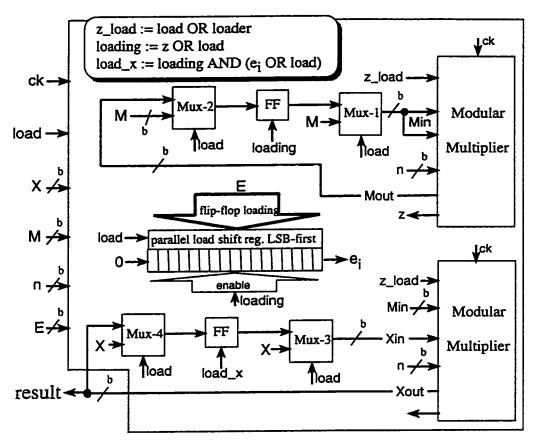

The hardware model of the expandable RSA cryptographic system, as proposed in this Thesis, has been described in the previous chapter. For comparison purposes, two other RSA designs have been modeled. They differ mainly in the techniques used for implementing modular multiplication. In both cases, the modular exponentiation algorithm is the same. These two implementations are the merged exponentiation hardware and the add/subtract exponentiation design [24, 43].

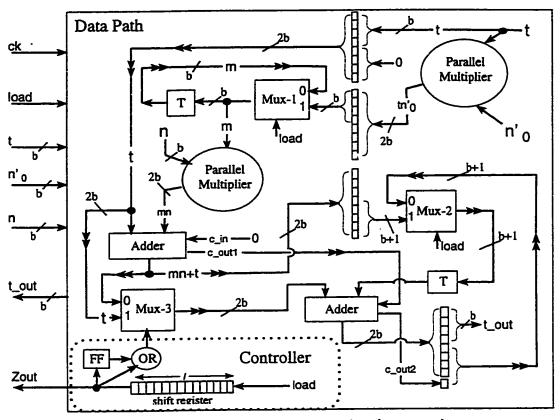

### 5.2 The Merged Exponentiation Hardware

The merged exponentiation hardware depends on Montgomery's technique for modular multiplication. However, Montgomery's multiplication algorithm is reorganized to merge the multiplication with reduction for each digit. This algorithm was found to be the best among several other merged algorithms compared for both speed and hardware complexity, as outlined by C. K. Koc in 1996 [24]. It deals with large numbers by dividing them into *l*-words (digits) with each word having *b*-bits.

#### 5.2.1 The Merged Montgomery Product Algorithm

The merged Montgomery product (MP) algorithm is shown in Figure 5.1 [24]. The algorithm computes:  $MP(x, y) = xyr^{-1} \mod n$ , where: r > n > x, y and gcd(r, n) = 1.

Figure 5.1: The MP merged algorithm

It can be observed (Figure 5.1) that the MP algorithm consists of an outer loop and two inner loops. The outer loop controls the loop-index 'i' which fixes the multiplication operand 'y(i)' for the inner first loop. The two inner loops represent the multiplication and the reduction operations. The multiplication loop performs a digit-wise multiplication of 'y(i)' by 'x'. The MP-algorithm of Figure 5.1 assumes that all digits of 't' will be first computed by the multiplication loop, then these digits are processed by the reduction loop.

Careful study of the above algorithm shows that the reduction process does not need to wait until all digits of the multiplication process are computed. Accordingly, the two inner loops can be merged into one inner loop in such a way that each digit of t computed by the multiplication process is passed to the reduction process in a digit-wise manner. It can also be observed that the multiplication loop runs l times (0 to l-1), while the reduction loop runs l-1 times (1 to l-1). To accommodate this, several conditionals are used within the body of

the merged loop whose index is made to vary from 0 to l. The reorganized MP-algorithm is shown in Figure 5.2.

Figure 5.2: The reorganized MP merged algorithm

In the MP-algorithm shown in Figure 5.1, the same sum and carry (c,s) variables are used for both the multiplication and the reduction loops since both loops are disjoint. However, in the reorganized algorithm (Figure 5.2), different sum and carry variables are used for the multiplication and the reduction processes.

It is to be noted that, the reorganized MP-algorithm shown in Figure 5.2 is more efficient in terms of hardware cost. It does not require registers to hold the intermediate values of t, computed by the multiplication process. A general implementation model of the reorganized MP-algorithm (Figure 5.2) is shown in Figure 5.3.

#### 5.2.2 The Merged MP Implementation

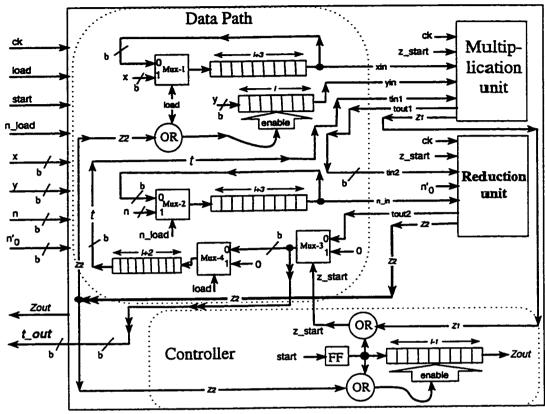

Considering Figure 5.3, the implementations of the multiplication and the reduction units are described in the following subsections. The controller and the data path are shown in

Figure 5.3: The MP merged algorithm implementation model

Figure 5.4 with their connections to the multiplication and reduction units.

The controller consists of a shift register and two OR gates. The data path is mainly made of data registers and multiplexers. Mux-1 and Mux-2 are for loading new values of inputs. Mux-3 resets the register to zero at the beginning of the process. Mux-4 is to perform step 1 of the MP-algorithm (Figure 5.2). The size of the shift register following Mux-4, is one stage less than the shift registers following Mux-1 and Mux-2. This is done to accommodate the loading required in steps 14, 16, and 17, of the MP-algorithm (Figure 5.2).

The signal 'start' triggers the complete MP-process. Loading the values of x, y, is controlled by signal 'load'. Another data loading signal is 'n\_load', which is responsible of loading the modulus n. Although the number of clock cycles required to load the input data x, y and n is the same, two different loading signals are used, namely 'load' and 'n\_load'. This is due to the fact that data values of x and y change depending on the message being encrypted/decrypted, while the value of the modulus n is fixed depending only on the encryption/decryption key.

The multiplication process requires multiplying each digit of y by all the digits of x, as shown in Figure 5.2. Fixing a digit of y (y(i)) for each multiplication process is performed with the use of an enable-shift-register, i.e. shifting the digits of y is enabled only once for each outer loop iteration. The digits of x are fed and rotated through the use of a shift register and Mux-1. The signal ' $z_1$ ' indicates that the output of the multiplication process ( $t_{out1}$ ) is computed for this y-digit. The bus  $t_{out1}$  is passed to the reduction unit as ' $t_{in2}$ '. The reduction unit will process the data values of  $t_{in2}$  as well as the fixed digit of  $n'_0$ . The signal ' $z_2$ ' indicates that the result of the reduction process using this digit of y is available on ' $t_{out2}$ '. This data value ( $t_{out2}$ ) is then fed back to the multiplication process as the bus ' $t_{in1}$ ' to update the value of 't', as required by the MP-algorithm shown in Figure 5.2. The

signal 'z<sub>out</sub>' indicates that the final result value is found at 't\_out' and that will end the MP process.

Figure 5.4: The merged MP multiplier implementation

#### 5.2.3 The Multiplication Loop Implementation

Figure 5.5: The multiplication process implementation outline