# FSM STATE-ASSIGNMENT FOR AREA, POWER AND TESTABILITY USING NON-DETERMINISTIC EVOLUTIONARY HEURISTICS

by

#### FAISAL NAWAZ KHAN

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

In Partial Fulfillment of the Requirements for the degree

#### MASTER OF SCIENCE

IN

#### COMPUTER ENGINEERING

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

Dhahran, Saudi Arabia

May 2005

## KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA

#### DEANSHIP OF GRADUATE STUDIES

This thesis, written by FAISAL NAWAZ KHAN under the direction of his thesis advisor and approved by his thesis committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE IN COMPUTER ENGINEERING.

|                          | Thesis Committee                  |

|--------------------------|-----------------------------------|

|                          | Dr. El – Maleh, Aiman (Chairman)  |

|                          | Dr. Sait, Sadiq Mohammed (Member) |

| Department Chairman      | Dr. Naseer, A.R. (Member)         |

| Dean of Graduate Studies |                                   |

| Date                     |                                   |

## Acknowledgments

All praise be to Allah (s.w.t) for his limitless blessing and guidance. May Allah bestow peace on his prophet, Muhammad (p.b.u.h), his family and his followers.

I would like to express my profound gratitude and appreciation to my thesis committee chairman Dr. Aiman El-Maleh, for his guidance, patience, and sincere advice throughout this thesis. I acknowledge him for his valuable time, constructive criticism, and stimulating discussions. I am also indebted to my thesis committee member and academic advisor, Dr. Sadiq M. Sait for his enduring support and interest throughout my thesis work. Thanks are also due to my thesis committee members, Dr. A. R. Naseer for his comments and critical review of the thesis.

All my family members, especially my parents and aunt Miss Naseem Fatima, were constant source of motivation and support. Their love and care carried me through some difficult moments in my life. Their prayers, guidance and inspiration was invaluable in fulfilling this accomplishment. My sincere appreciation to all the friends and colleagues, in particular Saqib Khursheed, Theeb Al-Ghatani, Louai Al-Awami, Mohammad Omara, who contributed to this achievement in a direct or an indirect way.

I am also thankful for the support and computing facilities provided by King Fahd University of Petroleum & Minerals for this research.

## Dedicated to

My parents and my aunt, Miss Naseem Fatima Jaffery

## Contents

|                   | Ack  | nowledgments                 | iii |

|-------------------|------|------------------------------|-----|

|                   | List | of Tables                    | xii |

|                   | List | of Figures x                 | iii |

|                   | Abs  | stract (English)             | vii |

| Abstract (Arabic) |      | stract (Arabic) xv           | iii |

| 1                 | Intr | roduction and Motivation     | 1   |

|                   | 1.1  | Introduction                 | 1   |

|                   | 1.2  | Motivation                   | 3   |

|                   | 1.3  | FSM State Assignment Problem | 4   |

|                   | 1.4  | Thesis Objective             | 5   |

|                   | 1.5  | Contributions                | 5   |

|                   | 1.6  | Organization of the Thesis   | 7   |

| 2 | Lite | erature Review                            | 8  |

|---|------|-------------------------------------------|----|

|   | 2.1  | Introduction                              | 8  |

|   | 2.2  | Finite State Machine State Assignment     | 9  |

|   |      | 2.2.1 Encoding and Partitioning           | 10 |

|   | 2.3  | FSM Encoding for Area                     | 20 |

|   |      | 2.3.1 Jedi Multilevel Area Measure        | 27 |

|   |      | 2.3.2 Mustang Multilevel Area Measure     | 28 |

|   |      | 2.3.3 Armstrong's Multilevel Area Measure | 30 |

|   |      | 2.3.4 Expand                              | 33 |

|   | 2.4  | FSM Encoding for Low Power                | 34 |

|   | 2.5  | FSM Encoding for Testability              | 46 |

|   |      | 2.5.1 Testability Parameters              | 51 |

|   | 2.6  | Multiobjective Optimization               | 52 |

|   |      | 2.6.1 Search and Decision Making          | 54 |

|   |      | 2.6.2 Goal Programming                    | 55 |

|   |      | 2.6.3 Fuzzy Logic                         | 57 |

|   | 2.7  | Non-Deterministic Iterative Algorithms    | 61 |

|   |      | 2.7.1 Genetic Algorithm (GA)              | 62 |

|   |      | 2.7.2 Tabu Search (TS)                    | 65 |

|   | 2.8  | Summary                                   | 67 |

| 3         | Pro | blem Formulation and Solution Methodology                     | 68  |

|-----------|-----|---------------------------------------------------------------|-----|

|           | 3.1 | Introduction                                                  | 68  |

|           | 3.2 | Problem Statement                                             | 69  |

|           | 3.3 | Cost Functions for Multilevel Area Minimization               | 70  |

|           |     | 3.3.1 Literal Savings - 1                                     | 70  |

|           |     | 3.3.2 Literal Savings - 2                                     | 71  |

|           |     | 3.3.3 Literal Savings - 3                                     | 72  |

|           |     | 3.3.4 Literal Savings - 4                                     | 73  |

|           |     | 3.3.5 Expand                                                  | 74  |

|           | 3.4 | Cost Functions for Power                                      | 79  |

|           | 3.5 | Cost Functions for Testability                                | 83  |

|           | 3.6 | Complementation                                               | 90  |

|           |     | 3.6.1 Formal Complement                                       | 91  |

|           |     | 3.6.2 Quick Complement Check                                  | 93  |

|           | 3.7 | Loops Calculation                                             | 99  |

|           | 3.8 | Fuzzy Goal Based Aggregation for SAP                          | 104 |

|           | 3.9 | Summary                                                       | 106 |

| 4         | Nor | n-Deterministic Evolutionary Heuristics for FSM State Assign- |     |

| <b>-1</b> |     | ·                                                             |     |

|           | mer | lt .                                                          | 107 |

|           | 4.1 | Introduction                                                  | 107 |

|   | 4.2 | SA In  | heritance                             |

|---|-----|--------|---------------------------------------|

|   | 4.3 | Genet  | ic Algorithm                          |

|   |     | 4.3.1  | Chromosome Representation             |

|   |     | 4.3.2  | Crossover                             |

|   |     | 4.3.3  | Mutation                              |

|   |     | 4.3.4  | Parents Selection                     |

|   |     | 4.3.5  | Next Generation Selection             |

|   |     | 4.3.6  | Uniqueness of Offsprings              |

|   | 4.4 | Tabu   | Search                                |

|   |     | 4.4.1  | Tabu Move and Solution Representation |

|   |     | 4.4.2  | Neighborhood Size                     |

|   |     | 4.4.3  | Tabu List Size and Tabu Specification |

|   |     | 4.4.4  | Aspiration Criteria                   |

|   | 4.5 | Summ   | ary                                   |

| 5 | Exp | erime  | ntal Results and Analysis 125         |

|   | 5.1 | Introd | luction                               |

|   | 5.2 | Simula | ation Environment                     |

|   |     | 5.2.1  | Benchmarks                            |

|   | 5.3 | Genet  | ic Algorithm                          |

|   |     | 5.3.1  | Mutation Rate                         |

|   |     | 5.3.2  | Effect of Population Size            | 129 |

|---|-----|--------|--------------------------------------|-----|

|   |     | 5.3.3  | Effect of Generation Size            | 130 |

|   |     | 5.3.4  | Crossover Operators                  | 131 |

|   | 5.4 | Tabu S | Search                               | 138 |

|   |     | 5.4.1  | Neighborhood Size                    | 138 |

|   |     | 5.4.2  | Performance Comparison of TS and GA  | 142 |

|   | 5.5 | Area   |                                      | 144 |

|   |     | 5.5.1  | Tabu Comparison                      | 165 |

|   | 5.6 | Power  |                                      | 168 |

|   |     | 5.6.1  | MWHD                                 | 169 |

|   |     | 5.6.2  | Fanout                               | 170 |

|   |     | 5.6.3  | Power and Area Estimates Integration | 173 |

|   |     | 5.6.4  | Literature Comparison                | 179 |

|   | 5.7 | Testab | pility                               | 185 |

|   |     | 5.7.1  | Literature Comparison                | 191 |

|   | 5.8 | Area,  | Power and Testabilty                 | 193 |

|   |     | 5.8.1  | Literature Comparison                | 199 |

|   | 5.9 | Conclu | ısion                                | 201 |

| 6 | Cor | clusio | n and Future Work                    | 203 |

| Ü |     |        |                                      |     |

|   | 6.1 | Conclu | asion                                | 203 |

|              | 6.2 Future Research                                  | . 205 |

|--------------|------------------------------------------------------|-------|

|              | APPENDICES                                           | 208   |

| $\mathbf{A}$ | Solving Discrete-Time Markov Chains                  | 208   |

| $\mathbf{R}$ | Steady State Probabilities of the Benchmark Circuits | 215   |

## List of Tables

| 2.1 | State Machine - 1                                                    | 10  |

|-----|----------------------------------------------------------------------|-----|

| 2.2 | A sample encoding for State Machine - 1                              | 11  |

| 2.3 | State Machine - 2                                                    | 14  |

| 2.4 | State Machine - 3                                                    | 18  |

| 2.5 | Merging of three symbolic implicants                                 | 24  |

| 2.6 | Using code word covering                                             | 24  |

| 2.7 | Using disjunctive codes                                              | 25  |

| 2.8 | State Machine - 4                                                    | 34  |

| 3.1 | Positional cube notation                                             | 75  |

| 3.2 | Boolean Algebra using 3-valued logic on two-input AND/OR gates. $$ . | 84  |

| 3.3 | Boolean Algebra using 3-valued logic on NOT gate                     | 84  |

| 4.1 | State Machine - 1                                                    | 109 |

| 5 1 | Statistics of benchmarks used [97]                                   | 127 |

| 5.2  | Effect of different mutation rates on solution quality             |

|------|--------------------------------------------------------------------|

| 5.3  | Effect of varying population size (Literals(Time))                 |

| 5.4  | Effect of varying generation size (Literals(Time))                 |

| 5.5  | PMX crossover versus that proposed by Amaral [27]                  |

| 5.6  | Solution quality comparison between the crossovers at similar time |

|      | instants                                                           |

| 5.7  | Comparison of cost functions-1                                     |

| 5.8  | Comparison of cost functions-2                                     |

| 5.9  | Cost functions comparison - I                                      |

| 5.10 | Cost functions comparison - II                                     |

| 5.11 | Literal count comparison between TS and GA                         |

| 5.12 | Literal count comparison between TS and GA by fixing time 167      |

| 5.13 | Power consumption comparison of MWHD with Jedi                     |

| 5.14 | Performance of Fanout measure                                      |

| 5.15 | Product based integration of area and power estimates              |

| 5.16 | Fuzzy based integration of area and power estimates                |

| 5.17 | Comparison between Fanout(Max) and Jedi-Default                    |

| 5.18 | Power consumption when optimizing for area alone                   |

| 5.19 | Power and Area reduction comparison with Pedram et al [63] 182     |

| 5.20 | Power reduction comparison with Ciesielski et al [98]              |

| 5.21 | Power reduction comparison with IITG8 [99]                         |

| 5.22 | Power comparison with Xia and Almaini [65]                              |

|------|-------------------------------------------------------------------------|

| 5.23 | Comparison of fault coverages                                           |

| 5.24 | Comparison of fault efficiencies                                        |

| 5.25 | Comparison of CPU processing times                                      |

| 5.26 | Fault Coverage comparison with Ciesielski et al [98]                    |

| 5.27 | Area comparison for different aggregation mechanisms                    |

| 5.28 | Power dissipation comparison for different aggregation mechanisms . 195 |

| 5.29 | Fault coverage comparison for different aggregation mechanisms 196      |

| 5.30 | Fault efficiency comparison for different aggregation mechanisms 197    |

| 5.31 | CPU processing time comparison for different aggregation mechanisms 198 |

| 5.32 | Integrated power comparison from Ciesielski et al [98] 200              |

| 5.33 | Integrated fault-coverage comparison from Ciesielski et al [98] 200     |

## List of Figures

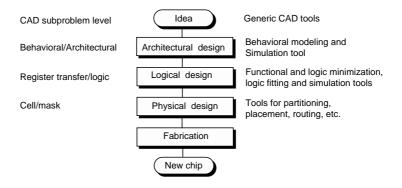

| 1.1 | Levels of abstraction and corresponding design steps [2]       | 2   |

|-----|----------------------------------------------------------------|-----|

| 2.1 | Adjacency Graphs                                               | 34  |

| 2.2 | An example illustrating MWHD formulation                       | 41  |

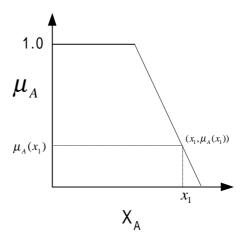

| 2.3 | Membership function of a fuzzy set A                           | 59  |

| 2.4 | Outline of simple Genetic Algorithm [6]                        | 63  |

| 2.5 | Outline of Tabu Search algorithm [6]                           | 66  |

| 3.1 | Example illustrating Expand-function                           | 78  |

| 3.2 | Weighted Graph & State Assignment for Fanout based approach    | 82  |

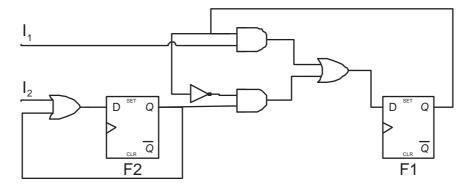

| 3.3 | Flip-flop $F_1$ detected uninitializable due to 3-valued logic | 85  |

| 3.4 | Example illustrating zero initialization sequence              | 86  |

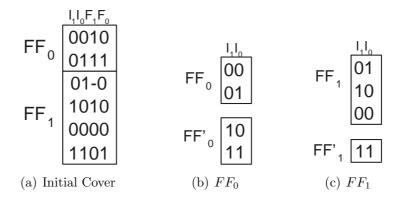

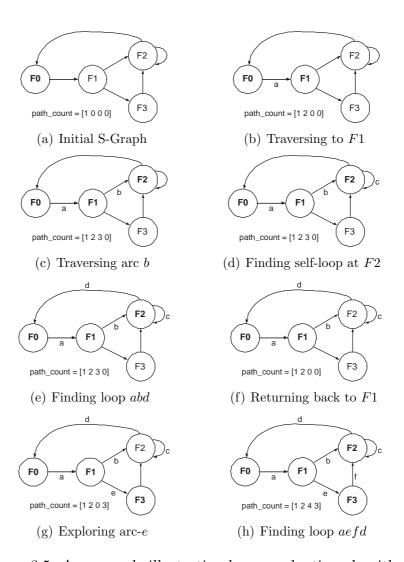

| 3.5 | An example illustrating loops evaluation algorithm             | 100 |

| 3.6 | The loops evaluation algorithm                                 | 101 |

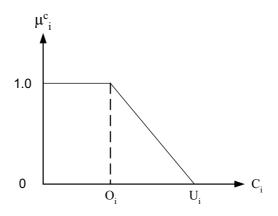

| 3 7 | Membership functions                                           | 105 |

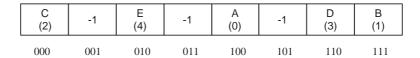

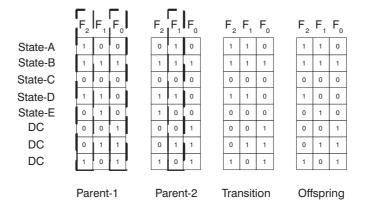

| 4.1  | Chromosome Representation-1 for Code- $\alpha$ in State Machine-1 114          |

|------|--------------------------------------------------------------------------------|

| 4.2  | Chromosome representation-2 for code- $\alpha$ in state machine-1 115          |

| 4.3  | Chromosome Representation-2 for Code- $\alpha$ in State Machine-1 116          |

| 4.4  | Illustrating Amaral Crossover using Code- $\alpha$ and Code- $\gamma$ in State |

|      | Machine-1                                                                      |

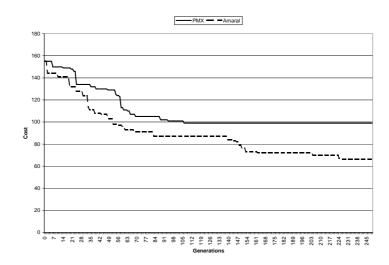

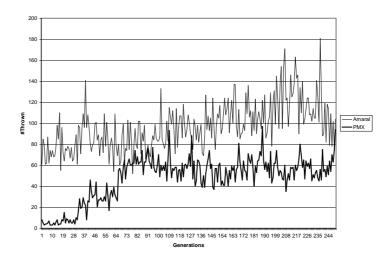

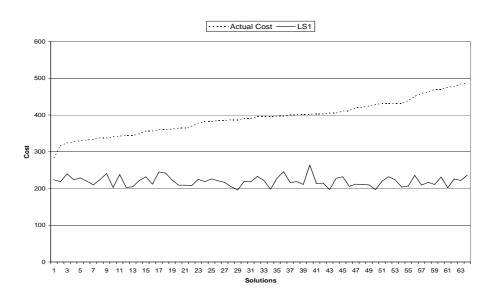

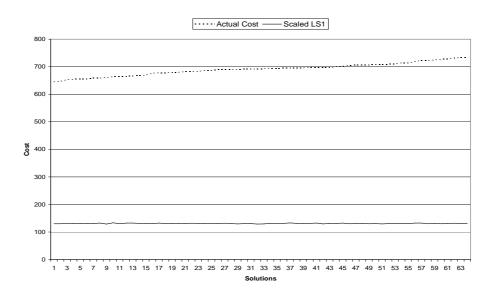

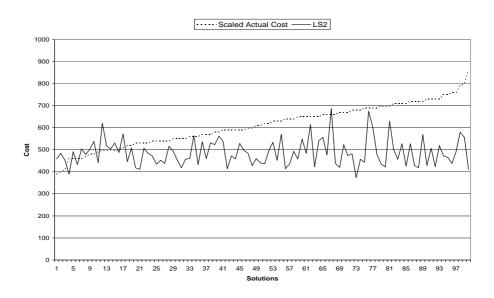

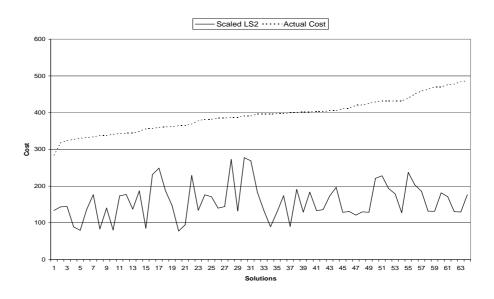

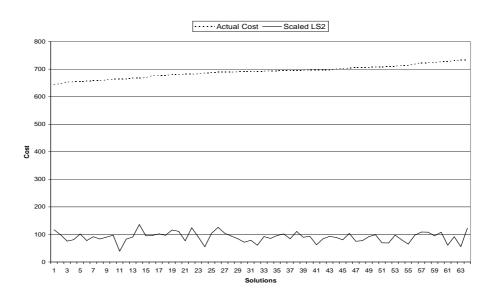

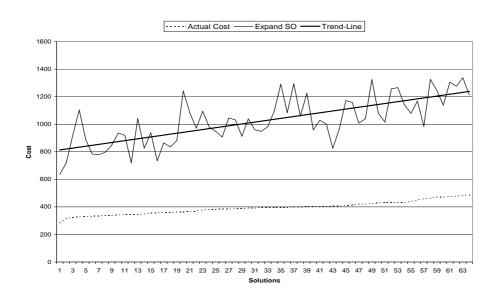

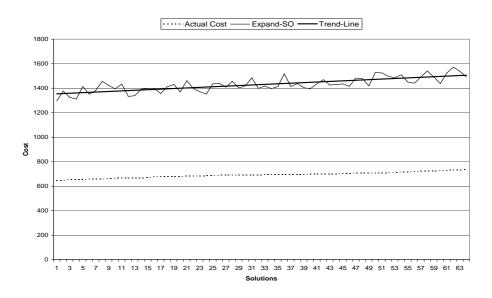

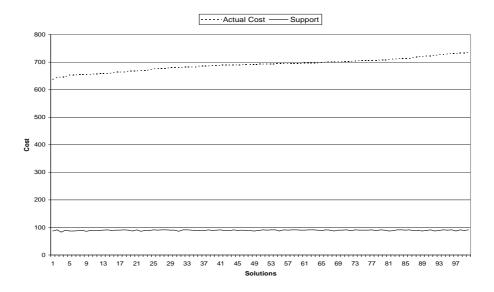

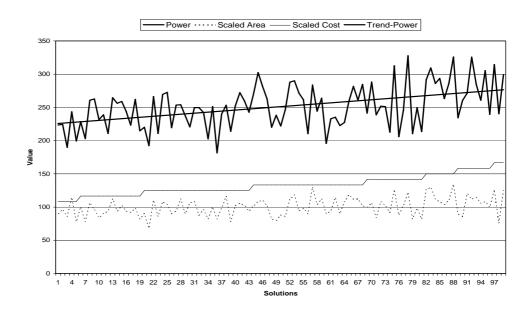

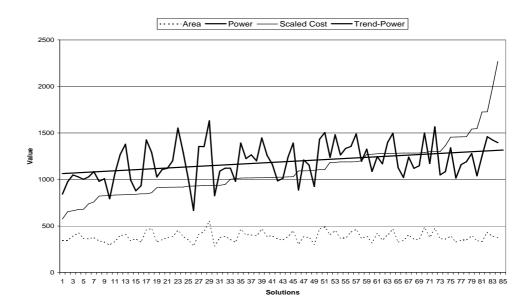

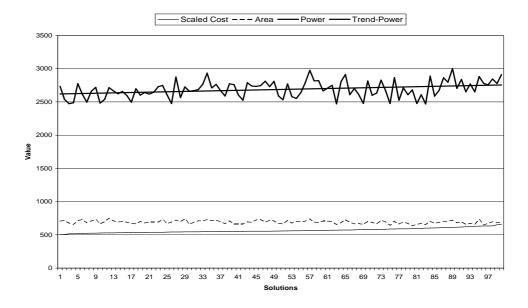

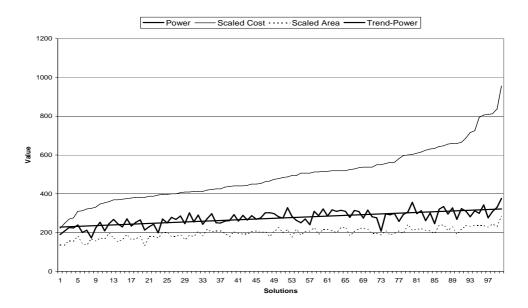

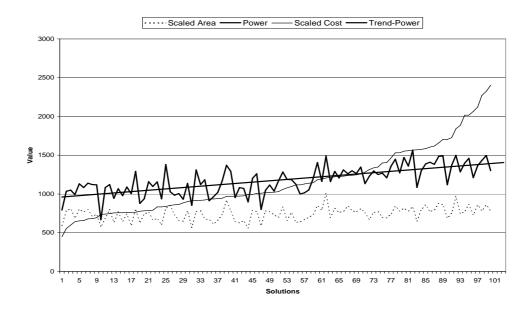

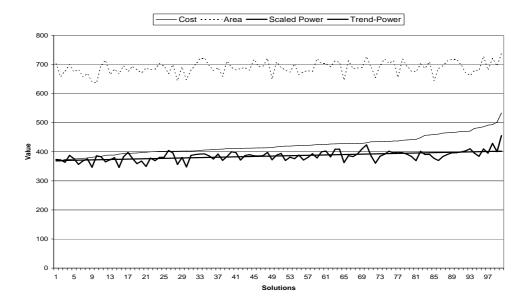

| 5.1  | PMX versus Amaral's crossover on ex2 circuit                                   |

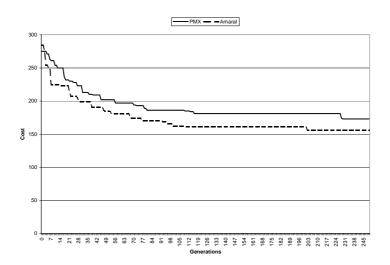

| 5.2  | PMX versus Amaral's crossover on $keyb$ circuit                                |

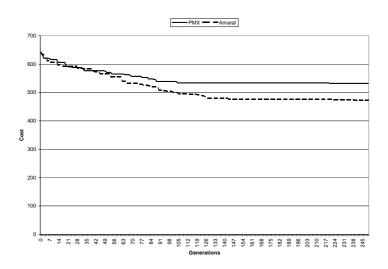

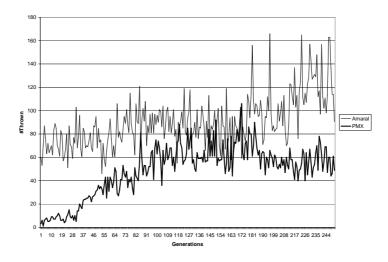

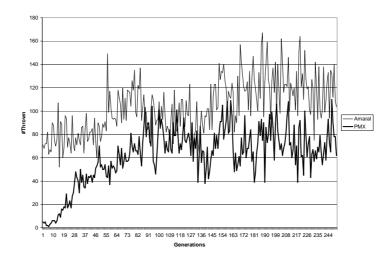

| 5.3  | PMX versus Amaral's crossover on <i>planet</i> circuit                         |

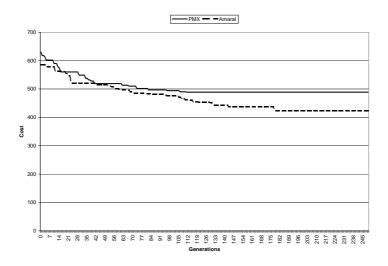

| 5.4  | PMX versus Amaral's crossover on <i>styr</i> circuit                           |

| 5.5  | Crossovers comparison in terms of duplicate offsprings on $ex2$ circuit. 135   |

| 5.6  | Crossovers comparison in terms of duplicate offsprings on $keyb$ circuit. 135  |

| 5.7  | Crossovers comparison in terms of duplicate offsprings on $styr$ circuit. 136  |

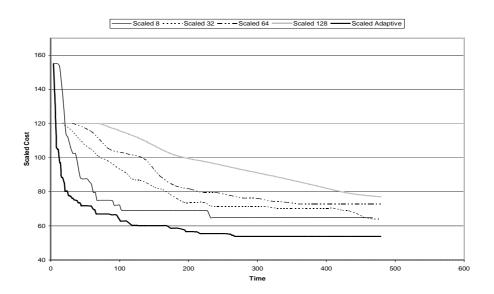

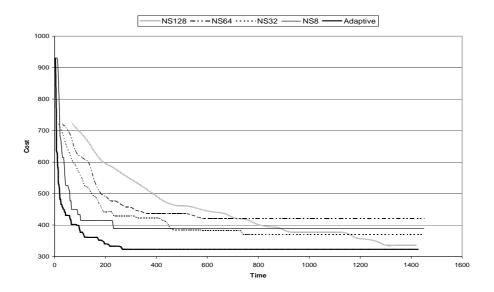

| 5.8  | Effect of different neighborhood sizes on $keyb$ circuit - 1                   |

| 5.9  | Effect of neighborhood sizes on keyb circuit - 2                               |

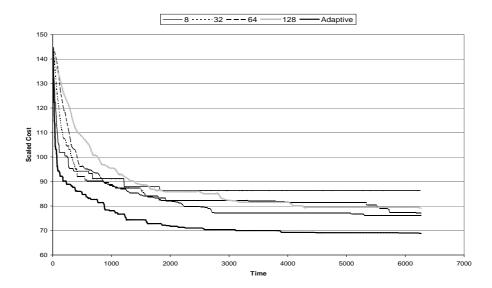

| 5.10 | Effect of different neighborhood sizes on <i>planet</i> circuit                |

| 5.11 | Performance of adaptive NS on <i>keyb</i> circuit                              |

| 5.12 | Performance of adaptive NS on <i>planet</i> circuit                            |

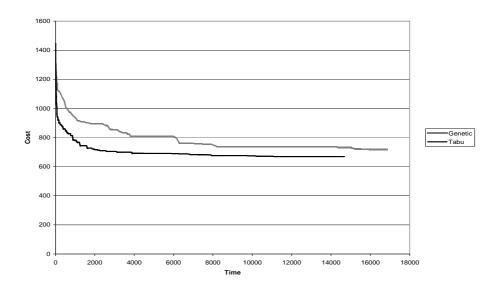

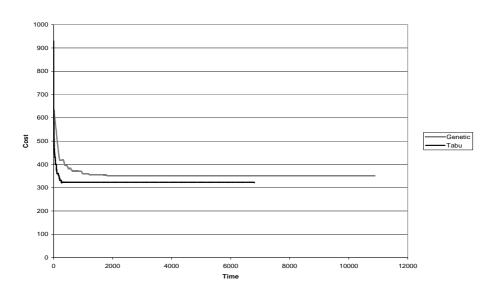

| 5.13 | TS versus GA on <i>planet</i> circuit                                          |

| 5.14 | TS versus GA on <i>keyb</i> circuit                                            |

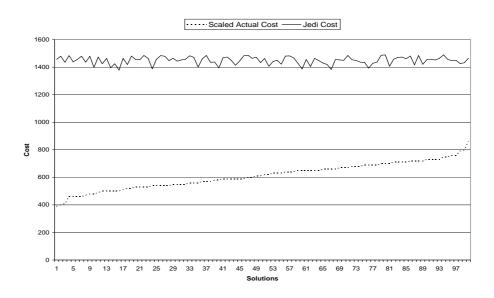

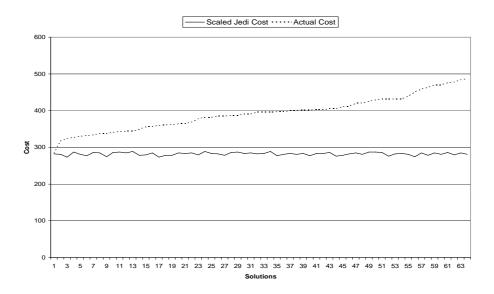

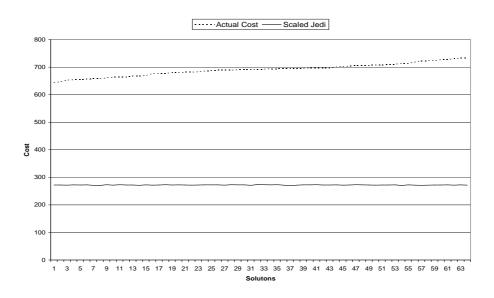

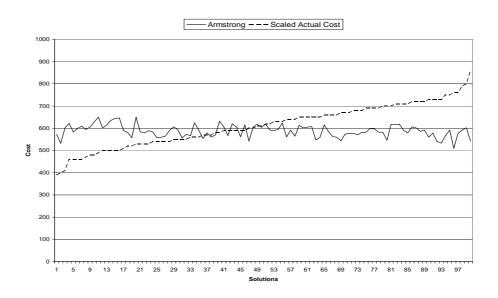

| 5.15 | Jedi correlation on <i>train11</i> circuit                                     |

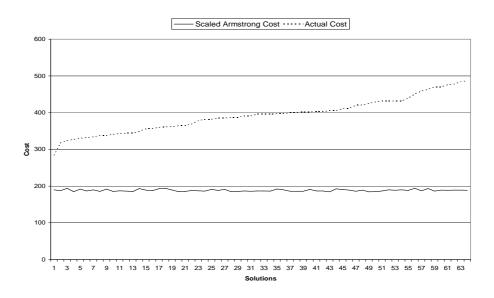

| 5.16 | Jedi correlation on $keyb$ circuit                 | :7 |

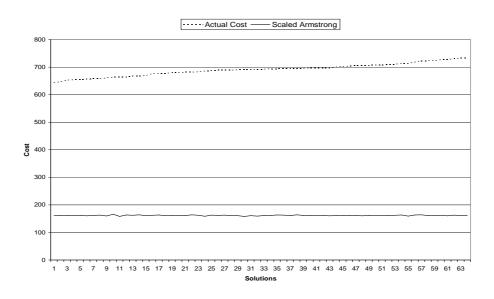

|------|----------------------------------------------------|----|

| 5.17 | Jedi correlation on <i>planet</i> circuit          | 8: |

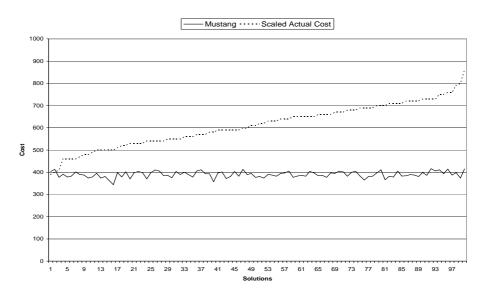

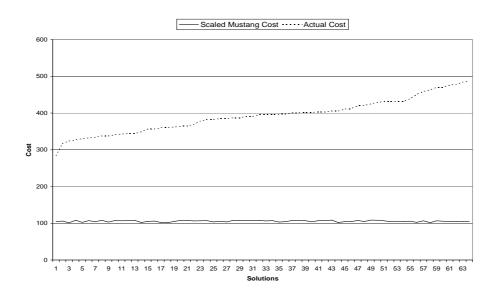

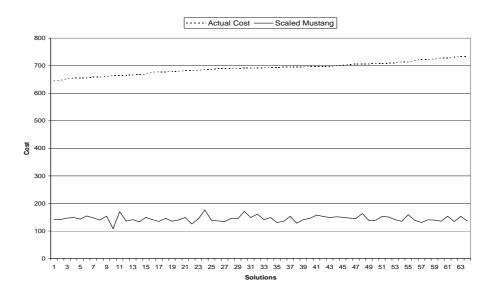

| 5.18 | Mustang correlation on <i>train11</i> circuit      | 8  |

| 5.19 | Mustang correlation on keyb circuit                | .9 |

| 5.20 | Mustang correlation on <i>planet</i> circuit       | .9 |

| 5.21 | Armstrong correlation on <i>train11</i> circuit    | 0  |

| 5.22 | Armstrong correlation on keyb circuit              | 0  |

| 5.23 | Armstrong correlation on <i>planet</i> circuit     | 1  |

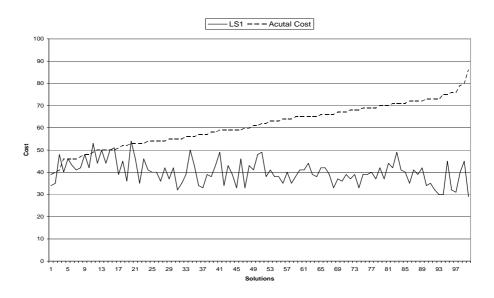

| 5.24 | LS1 correlation on <i>train11</i> circuit          | 1  |

| 5.25 | LS1 correlation on keyb circuit                    | 2  |

| 5.26 | LS1 correlation on <i>planet</i> circuit           | 2  |

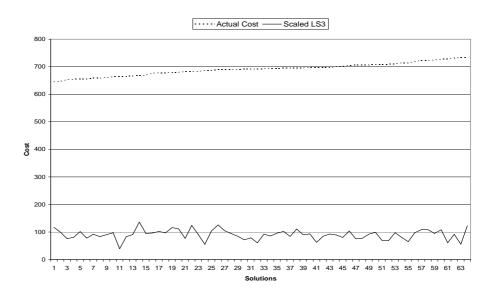

| 5.27 | LS2 correlation on <i>train11</i> circuit          | 3  |

| 5.28 | LS2 correlation on $keyb$ circuit                  | 3  |

| 5.29 | LS2 correlation on <i>planet</i> circuit           | 4  |

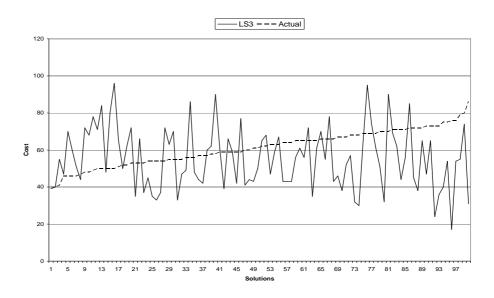

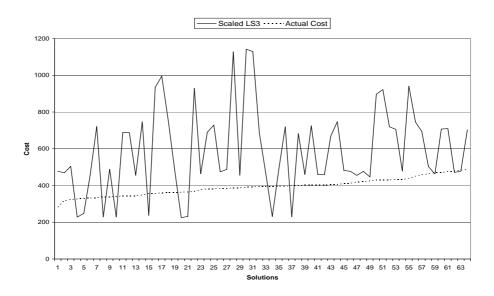

| 5.30 | LS3 correlation on <i>train11</i> circuit          | 4  |

| 5.31 | LS3 correlation on $keyb$ circuit                  | 5  |

| 5.32 | LS3 correlation on <i>planet</i> circuit           | 5  |

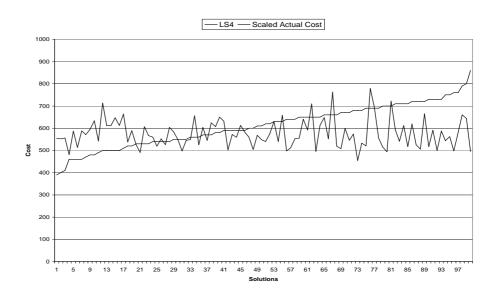

| 5.33 | LS4 correlation on <i>train11</i> circuit          | 6  |

| 5.34 | LS4 correlation on $keyb$ circuit                  | 6  |

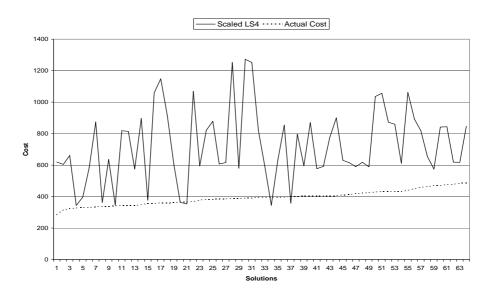

| 5.35 | LS4 correlation on <i>planet</i> circuit           | 7  |

| 5.36 | Expand-SO correlation on <i>train11</i> circuit 15 | 7  |

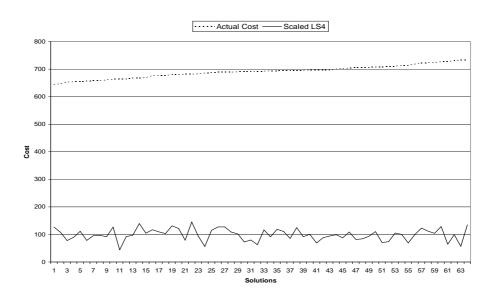

| 5.37 | Expand-SO correlation on $keyb$ circuit                     |

|------|-------------------------------------------------------------|

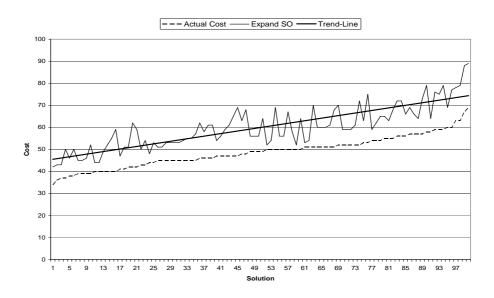

| 5.38 | Expand-SO correlation on <i>planet</i> circuit              |

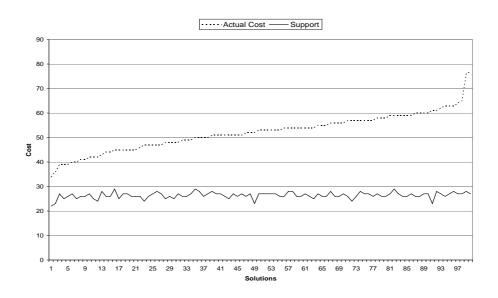

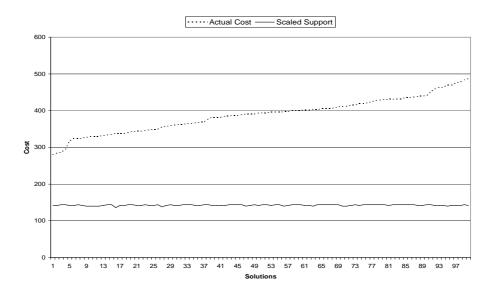

| 5.39 | Support correlation on <i>train11</i> circuit               |

| 5.40 | Support correlation on $keyb$ circuit                       |

| 5.41 | Support correlation on <i>planet</i> circuit                |

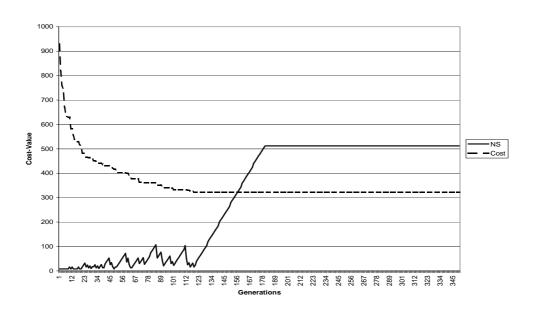

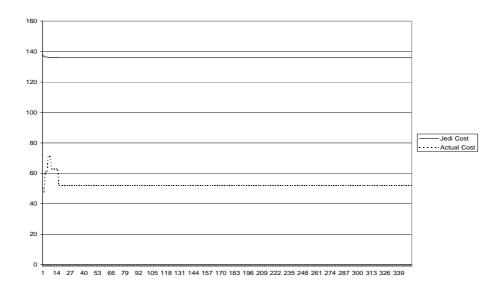

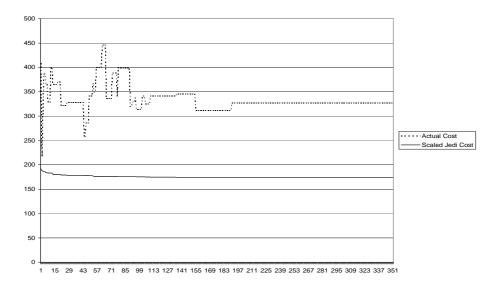

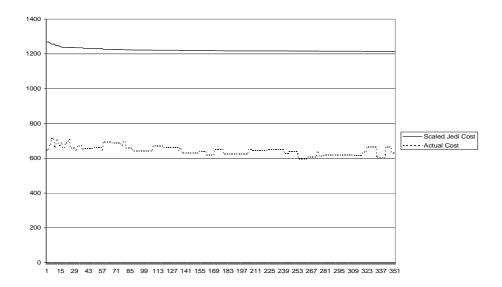

| 5.42 | Jedi generation convergence graph on <i>train11</i> circuit |

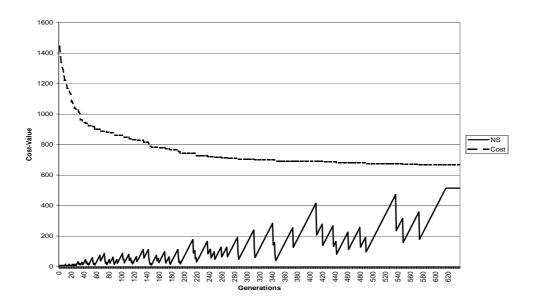

| 5.43 | Jedi generation convergence graph on $keyb$ circuit         |

| 5.44 | Jedi generation convergence graph on <i>planet</i> circuit  |

| 5.45 | Power calculation script                                    |

| 5.46 | MWHD correlation on <i>train11</i> circuit                  |

| 5.47 | MWHD correlation on $keyb$ circuit                          |

| 5.48 | MWHD correlation on <i>planet</i> circuit                   |

| 5.49 | Fanout correlation on <i>train11</i> circuit                |

| 5.50 | Fanout correlation on $keyb$ circuit                        |

| 5.51 | Fanout correlation on <i>planet</i> circuit                 |

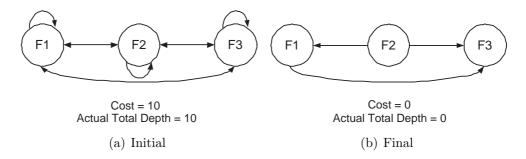

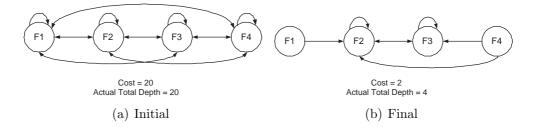

| 5.52 | Loops reduction on <i>shiftreg</i> circuit                  |

| 5.53 | Loops reduction on <i>train11</i> circuit                   |

| A.1  | A state machine                                             |

#### THESIS ABSTRACT

Name: FAISAL NAWAZ KHAN

Title: FSM STATE-ASSIGNMENT FOR AREA, POWER AND

TESTABILITY USING NON-DETERMINISTIC

**EVOLUTIONARY HEURISTICS**

Major Field: COMPUTER ENGINEERING

Date of Degree: MAY 2005

The rapid increase in complexity of VLSI circuits along with their proliferation in new domains has posed new challenges to the VLSI CAD industry. Mobile devices have added low power computation paradigm in VLSI design process along with conventional area (size) and performance (timing) goals. Similarly, increasing chip complexities (size) have further amplified the difficulty in VLSI testing with the focus now shifting towards efficient design techniques to ease in the device testability. With shrinking time to market windows, the need for efficient tools that can automate such multiobjective design processes at abstract levels has significantly increased.

A central problem in the synthesis of VLSI digital systems is controller synthesis which has traditionally been accomplished using Finite State Machines (FSMs). The complexity of FSM implementation depends on its state assignment. State assignment of FSMs for efficient area implementation alone is an NP-hard problem. The problem gets further involved if additional objectives such as low-power and ease of testability are considered. Non-deterministic evolutionary heuristics such as Genetic-Algorithms (GA) and Tabu-Search (TS) have shown to yield good results in solving such multiobjective hard combinatorial optimization problems in other areas of design automation.

In this thesis, the FSM state assignment problem (SAP) for area, power and testability as single as well as multiobjective optimization (MOP) is investigated. The work employs non-deterministic heuristics, GA and TS, in developing efficient design automation for search space exploration. New methods for estimating area, power and testability of a state assignment are presented. Experimental results compared with previous measures demonstrate the effectiveness of the proposed techniques.

#### MASTER OF SCIENCE DEGREE

King Fahd University of Petroleum and Minerals, Dhahran.

May 2005

#### ملخص الرسالة

الاسم: فيصل نواز خان

عنوان الدراسة: تعي ي ن المراحل للآلة منتهية الحالة للمساحة, إستهلاك الطاقة , و قابلية الإختبار باستخدام الخوارزميات التكرارية الغير تقديرية

التخصص: هندسة الحاسب الآلي

سنة التخرج: ربيع الثاني 1426هـ

إن ازدياد تعقيد الدوائر المتكاملة ذات الكثافة العالية و الإطراد في عدد التطبيقات الجديدة لها جلبت تحديات كثيرة لصناعة البرمجيات المستخدمة في تصميمها. فمثلاً حاجة الأجهزة المحمولة إلى انخفاض استهلاك الطاقة أضاف أطوار جديدة إلى عملية التصميم إضافة إلى الاطوار السابقة التي تركز على تقليل مساحة الشرائح و تحسين أدائها . كما أدت زيادة التعقيد في الرقاقة إلى صعوبة إجراء الأختبارات للتأكد من عملها في وقت زاد فيه التركيز على أساليب ال تصميم ذات الكفاءة العالية التي تسهل عملية الاختبار . كما أن الفترة الزمنية لخروج المنتج الى السوق أصبح مطلوباً أن تكون قصيرة جداً وكل ذلك أدى إلى إزدياد الحاجة لوجود أدوات و برامج تسهل وتسرع هذه العملية .

إن أحد أهم التحديات في عملية بناء الدوائر المتكاملة ذات الكثافة العالية هي تصميم دائرة التحكم التي عادة ما تتم باستخدام الآلة منتهية المراحل. إن التعقيد في استخدام الآلة منتهية المراحل يكمن في عملية تعيين المراحل و التي تعتبر مستحيلة الحل في وقت معقول خصوصاً عند أخذ المساحة و سهولة الأختبار بعين الإعتبار و لقد حققت الخوارزميات التكرارية الغير تقديرية مثل الخوارزميات الجيني ة و بحث تابو نتائج جيدة في حل المشاكل المتعددة الأهداف في مجالات أخرى في أتممة التصاميم.

في هذا الرسالة تتم دراسة مشكلة تعيين المراحل لآلة منتهية المراحل للمساحة, إستهلاك الطاقة و قابلية الإختبار كل على حدة بالإضافة إلى حالة تعدد الأهداف. كما و أن الرسالة تناقش استخدام الخوارزميات الجينية و بحث تابو لتتمية أتممة تصاميم ذات كفائة عالية لاستخدامها في استكشاف الفضاء للبحث عن الحلول بالإضافة إلى تقديم سبل جديدة لتقدير المساحة, إستهلاك الطاقة و قابلية الإختبار لعملية تعيين المراحل. و أخيرا تعرض الرسالة مقارنة بين الأساليب المطروحة و المقترحات السابقة بما يثبت فاعلية الأسلوب المطروح.

#### درجة الماجستير في العلوم

جامعة الملك فهد للبترول و المعادن, الظهران ربيع الثاني 1426هـ

## Chapter 1

## Introduction and Motivation

#### 1.1 Introduction

Technological advancements in Very Large Scale Integration (VLSI) have empowered the industry to integrate millions of transistors on a single chip. The contemporary approach adopted to address design of such high complexity devices is by utilizing techniques of structured designing and design abstraction [1]. Structured designing, also known as hierarchical or divide-and-conquer designing, breaks down a task into smaller operations until each step is refined into a a procedure simple enough to be written directly. Design abstraction abstracts complex low-level details of a design to allow the efforts of a designer to be focused at higher levels. This allows fast initial prototyping with refinements left to be added at lower stages using detailed circuit information. Typical levels of abstraction, together with their

corresponding functionalities, are illustrated in Figure 1.1. Fundamental to the use of design abstraction are Computer Aided Design (CAD) tools that automate the seamless flow and management of design information at all levels of VLSI design process.

Figure 1.1: Levels of abstraction and corresponding design steps [2].

The rapid increase in device sizes have enhanced system functionalities, giving rise to new paradigms such as mobile computing. With battery capacities predicted to lag behind power requirements for mobile devices, mobile computing has added a new facet of power efficiency in the complexity of VLSI design process [3]. At the same time, the increasingly chip complexities are proving more and more difficult to test. Efficient testing is no longer the sole responsibility of test engineers and the focus is now on better design strategies to make the device more easily testable [4]. Thus, testability adds up another aspect to ever more complex task of designing VLSI circuits.

#### 1.2 Motivation

The complexity of today's digital systems is tackled by partitioning and automating the design process using CAD tools. Digital systems are broadly composed of two subcomponents namely a *controller* and a *datapath*. The datapath performs all the arithmetic and logical operations required on the data while the controller handles proper sequencing of those operations. The design of controller has traditionally been achieved using Finite State Machines (FSMs) or Microprograms.

The complex task of designing VLSI systems, augmented by increasing number of issues and device complexities along with shrinking design times, is posing all the time more challenges for CAD industry to automate the tasks for a VLSI designer. Synthesis of FSMs is one VLSI design area that has gained considerable interest for efficient automation. There has been rich amount of work targeted for FSM area, power and testability objectives (see Chapter 2). However, the degree of diversity shown using the proposed measures suggest the FSM synthesis is still an open problem. Moreover, most of the heuristics reported address the problem of FSM synthesis for either a single or dual objectives and there exists a strong requirement to simultaneously address the problem for area, power and testability objectives and observe their relative effects on one another.

Traditionally, synthesis of FSMs is targeted for area minimization which itself is an NP-hard problem [5]. The problem gets further involved if additional objectives such as low-power and ease of testability are considered. Non-deterministic evolutionary heuristics like Genetic Algorithms (GA) and Tabu Search (TS) have shown good results in solving such combinatorial optimization problems in other areas of VLSI design automation [6]. These heuristics try to optimize user defined goals of the problem encapsulated within a cost function. The quality of the solution thus depends on how closely the problem is modeled using the cost measures.

There have been several attempts in using GA for FSM synthesis problem. However there is a lack of research study that compares the performance of various GA parameters and operators for optimizing the algorithmic performance for the problem. Similarly performance of TS, that has shown more promising results than GA in solving some combinatorial optimization, is yet to be evaluated for the problem.

#### 1.3 FSM State Assignment Problem

An FSM M can be formally defined as a 5-tuple  $M=(S,I,O,T,\delta)$  where S represents the finite state space, I represents the finite input space and O the finite output space,  $\delta:IxS\to S$  is the next-state function and T is the transition relation defined as I x  $S\to O$  (for a Mealy machine) or  $T:S\to O$  (for a Moore machine).

State Assignment Problem (SAP) involves an injective mapping f:  $S \to B^n$  where n is the code length  $(n \ge \lceil \log_2 |S| \rceil)$  and  $B^n$  is an n-dimensional Boolean space, a Boolean hypercube.

#### 1.4 Thesis Objective

The main goal of this work is to develop an automation to address the NP-hard problem of FSM state assignment such that area and power are reduced while increasing the testability of the circuit synthesized. Minimum Code-length is considered as constraint in this work. TS and GA are the automation engines employed for search space exploration

Individual objectives are explored using existing heuristics and new measures are proposed that better encapsulate their behavior at abstract levels. The objectives are further combined using various integrating mechanisms (discussed later) to solve multiobjective combinatorial optimization problem. Non-deterministic evolutionary heuristics, GA and TS, are the automation engines employed for search space exploration in this work. Thus another focus of this work is in the design of the exploration-heuristics for efficient exploration of SAP search space.

#### 1.5 Contributions

The work presents the results of investigations related to the objectives discussed in the previous section. In particular, the main contributions can be summarized as follows:

• The work proposes use of Expand-function as an efficient measure for multilevel area minimization of FSMs.

- A new power reduction strategy, Fanout, is presented that combines the traditional Minimum-Weighted-Hamming-Distance approach with area cover obtained using Expand-function. The technique aims at minimizing fanout of frequently switched states.

- A fuzzy based aggregation of Expand-function and Fanout is proposed as an efficient power minimization strategy for FSMs.

- A new recursive loop detection algorithm is proposed that can count the number and depth of loops present in an input cover.

- The work demonstrates initializability detection of sequential elements as an important factor affecting testability of a circuit, along with traditional depth and number of loops.

- A new method of initializability detection using Expand cover, Quick Complement Check, is proposed.

- TS is explored for SAP and is found to be efficient than GA.

- A fuzzy based aggregation of area, power and testability objectives for SAP

is proposed wherein individual objectives can be prioritized according to the

degree of optimization required relative to the others.

#### 1.6 Organization of the Thesis

The rest of the thesis is organized as follows. In Chapter 2, a survey of heuristics available in literature for SAP is presented. The chapter covers various techniques concerning the objectives of this work that are reported in literature, discussing relevant mathematics and background wherever required.

Chapter 3 formally defines the problem and discusses the proposed measures that are used in solving the problem in the this work. This is followed with a detailed discussion on the design of non-deterministic evolutionary heuristics for the given problem in Chapter 4.

In Chapter 5, experimental setup and results are presented using the measures discussed in Chapter 3 and compared with those discussed in Chapter 2. GA and TS are further experimented with in developing an efficient automation for the problem. Their relative performances are also compared in solving single as well as multiobjective optimization problems. The results are subsequently compared and contrasted with those reported in the literature. This thesis ends with conclusion and some future directions in Chapter 6.

## Chapter 2

### Literature Review

#### 2.1 Introduction

In this chapter, a survey of heuristics for FSM synthesis for area, power and testability is reported. The chapter begins by a formal discussion of SAP detailing the theory behind state assignment in Section 2.2. This is followed by a description of various measures that have been previously employed towards optimizing the goals of this work (Section 2.3 to Section 2.5). Review for FSM synthesis strategies is followed by a study of multiobjective optimization techniques in Section 2.6. Finally, non-deterministic iterative heuristics employed in this work, GA and TS, are discussed in Section 2.7.

FSM synthesis for area has traditionally been targeted independently for twolevel and multilevel realizations. Approaches used for FSM area optimization are discussed in Section 2.3. FSM synthesis for power has involved reduction between state transitions by utilizing state transition probabilities. Section 2.4 describes the relevant mathematics used behind FSM power optimization. Testability of an FSM is usually been improved by reducing sequential depth and number of loops in the sequential machine. A discussion on methods employed towards FSM testability is the focus of Section 2.5.

#### 2.2 Finite State Machine State Assignment

State assignment in FSMs [5] is one of the main problems in the synthesis of sequential machines. The complexity of FSMs lie in their combinational circuit that heavily depends on chosen state assignment or encoding for its sequential elements. Similarly, power dissipation and testability of the FSM are also functions of the state assignment. Thus, depending on the requirements, the assignment of states can be subject to different constraints. Gaining insight into the problem of assigning state codes is thus useful in coming up with solutions which will lead to structures and complexity that will satisfy the required objectives and constraints. This section thus proceeds with a discussion on relevant mathematics concerning the state assignment problem.

#### 2.2.1 Encoding and Partitioning

The state assignment problem of an FSM can be viewed as a coding problem or as a partitioning problem [5,7,8]. The coding problem requires each state to be assigned a unique binary pattern. From the partitioning point of view, each state variable,  $y_i$  (one of the bits of the memory part of FSM), partitions the assigned states into two sets. All states in one set are those for which  $y_i$  is 1, and those in the other set for which  $y_i$  is 0.

Therefore, a partition on a set S of states is a collection of disjoint subsets whose set union is S. The disjoint subsets are called the *blocks* of the partition. A partition is called an m-block partition if the number of blocks in it are m.

The partition induced by a state variable  $y_i$  is represented with the Greek symbol Tau,  $\tau(y_i)$ . As an example, consider a machine M with four states (A,B,C,D) and a single input (x) as given in Table 2.1.

| PS             | NS           |              |  |

|----------------|--------------|--------------|--|

|                | x=0          | x=1          |  |

| A              | A            | D            |  |

| В              | A            | $\mathbf{C}$ |  |

| $\overline{C}$ | $\mathbf{C}$ | В            |  |

| D              | $\mathbf{C}$ | A            |  |

Table 2.1: State Machine - 1.

The above state machine with a state assignment is shown in Table 2.2.

In the assignment used in Table 2.2,  $y_1 = 0$  for states A and B, and  $y_1 = 1$

| $y_{1}y_{2}$       | $Y_1Y_2$ |     |  |

|--------------------|----------|-----|--|

|                    | x=0      | x=1 |  |

| $A \rightarrow 00$ | 00       | 10  |  |

| $B \rightarrow 01$ | 00       | 11  |  |

| $C \rightarrow 11$ | 11       | 01  |  |

| $D \rightarrow 10$ | 11       | 00  |  |

Table 2.2: A sample encoding for State Machine - 1.

for states C and D. Therefore,  $y_1$  induces a 2-block partition  $\tau(y_1) = (\overline{AB}; \overline{CD})$ . Similarly,  $y_2$  induces another 2-block partition  $\tau(y_2) = (\overline{AD}; \overline{BC})$ , on the states of machine M.

If every state of the state machine is assigned a unique code then the product of all the partitions is a partition that has as many blocks as the number of states. We call such a partition as a zero partition represented by  $\pi(0)$ . Mathematically

$$\prod_{i=1}^{k} \tau(y_i) = \pi(0) \tag{2.1}$$

where k is number of partitions (which is also the number of state variables).

For example, the product of the partitions induced by coding of Table 2.2,  $\tau(y_1)$  and  $\tau(y_2)$  is given as

$$\tau(y_1) \cdot \tau(y_2) = (\overline{A}; \overline{B}; \overline{C}; \overline{D}) = \pi(0)$$

(2.2)

where the dot operator  $(\cdot)$  refers to the intersection operation on the states of blocks

in the individual partitions.

The problem of state assignment is to find a set of partitions such that (2.1) is true.

#### **Closed Partition**

A partition is said to be closed if for any two states  $S_i$  and  $S_j$  which are in the same block, and for any input  $I_k$ , the next-states denoted by  $I_k.S_i$  and  $I_k.S_j$  are in a common block of the partition. This condition must be true for all pairs of states in every block. Such a partition is said to be closed and is represented by  $\pi$ . For example, partition  $\tau(y_1)$  in Table 2.2 is a closed partition. A closed partition is a special form of a partition in which the next block can be uniquely determined from the knowledge of present block and inputs. For example, suppose that r state variables are assigned to a closed partition, where  $r = \lceil \log_2 |\pi| \rceil$  ( $|\pi|$  is the number of blocks in a closed partition) among k state variables of the sequential machine, where  $k = \lceil \log_2(n) \rceil$ , n being the number of states. Then, according to the definition of closed partition, the r state variables are independent of the remaining k-r state variables. Closed partition is thus referred to as zero-dependency condition. In the above example,  $y_1$  is independent of  $y_2$ . The equation for  $Y_1$  is

$$Y_1 = \overline{X}Y_1 + X\overline{Y_1} \tag{2.3}$$

Note that the partition  $\tau(y_2)$  is not a closed partition.

#### Parallel and Serial Decompositions

The presence of closed partition indicates that some of the state variables can be independently determined irrespective of the other state variables. Thus, if we can find a set of closed partitions such that Condition (2.1) above is satisfied, then the machine can be decomposed into parallel sub-machines, equal to the number of closed partitions in the set, operating independently. Such a decomposition is referred to as parallel decomposition. Mathematically it can be represented as,

$$\pi(1).\pi(2)\cdots\pi(k) = \pi(0)$$

(2.4)

However, if such a set of closed partitions could not be found, we need to find a partition denoted by T such that Condition (2.1) can be satisfied, i.e.,

$$\pi(1) \cdot \pi(2) \cdots \pi(v) \cdot T = \pi(0); \quad (v < k)$$

(2.5)

In such a case, the partitions  $\pi(1)$  to  $\pi(v)$  are still closed and so self-dependent. However, the partition T is not closed and so is dependent on state variables other than those assigned to itself. This yields a serial decomposition of a state machine in which independent subsets of the state machine feed the dependencies required for dependent subset of the machine.

|    |             | NS           |    |              |              |

|----|-------------|--------------|----|--------------|--------------|

| PS | $y_1y_2y_3$ | x1x2         |    |              |              |

|    |             | 00           | 01 | 10           | 11           |

| A  | 000         | A            | С  | D            | F            |

| В  | 011         | С            | В  | F            | ${ m E}$     |

| C  | 010         | A            | В  | F            | D            |

| D  | 110         | $\mathbf{E}$ | F  | В            | $\mathbf{C}$ |

| E  | 100         | E            | D  | $\mathbf{C}$ | В            |

| F  | 111         | D            | F  | В            | A            |

Table 2.3: State Machine - 2.

#### **Partition Pairs**

The structure of sequential machines is much more complicated than a bunch of parallel or serially connected sub-machines. There are sub-machines that are cross dependent. The concept of partition-pairs helps analyze such dependencies.

A partition pair (T, T') on the states of a sequential machine  $\mathbf{M}$  is an ordered pair of partitions such that, if  $S_i$  and  $S_j$  are in the same block of T, then for every input  $I_k$  in I,  $I_k.S_i$  and  $I_k.S_j$  are in the same block of T. The partition T is called the predecessor partition and T the successor partition.

Consider a state machine with a state assignment shown in Table 2.3. Partitions induced by state variables,  $y_2$  and  $y_3$  are given as

$$\tau(y_2) = \tau_1 = (\overline{A, E}; \overline{B, C, D, F}) \tag{2.6}$$

$$\tau(y_3) = \tau_2 = (\overline{A, C, D, E}; \overline{B, F}) \tag{2.7}$$

Clearly,  $(\tau_1, \tau_2)$  form a partition pair since the next-state at any input for a pair of states in a block in  $\tau_1$  lie in some block of  $\tau_2$ .  $\tau_1$  is said to be predecessor partition and  $\tau_2$  the successor. Thus, to uniquely determine the next block in the successor partition, one needs to know the present block in the predecessor partition along with inputs. That is to say that the successor partition is dependent on the information of the state variables that induce the predecessor partition. Thus, a partition pair can be thought of as one (or single) dependency condition.

#### P-Dependency Condition

A P-dependency condition, where P is greater than one, can be derived in a similar manner. This requires the computation of what is known as Mm-pairs [5].

A partition M(T') is the summation (union) of all partitions  $T_i$  such that  $(T_i, T')$  is a partition pair. Thus, M(T') is the largest partition, i.e., a partition containing the biggest blocks whose successor blocks are contained in T'. Similarly, a partition m(T) is the product (intersection) of all partitions  $T_{i'}$  such that  $(T, T_{i'})$  is a partition pair; where m(T) is the smallest partition, i.e., a partition containing the smallest blocks that can be the successors of the blocks of T.

Consider again the state machine of Table 2.3. The smallest partition that can

be implied by states A and C may be called as  $\tau_{AC}$ . Such a partition includes states A and C together in a block (AC) and leaves all other states in separate blocks, i.e.,

$$\tau_{AC} = (\overline{A}, \overline{C}; \overline{B}; \overline{D}; \overline{E}; \overline{F})$$

(2.8)

then a set of partition pairs  $(\tau_{AC}, \tau_x)$  and  $(\tau_{AC}, \tau_y)$  can be given as in equations-2.9 and 2.10 respectively.

$$(\tau_{AC}, \tau_x) = ((\overline{A}, \overline{C}; \overline{B}; \overline{D}; \overline{E}; \overline{F}), (\overline{A}; \overline{B}, \overline{C}; \overline{D}, \overline{F}; \overline{E}))$$

(2.9)

$$(\tau_{AC}, \tau_y) = ((\overline{A}, \overline{C}; \overline{B}; \overline{D}; \overline{E}; \overline{F}), (\overline{A}, \overline{B}, \overline{C}; \overline{D}, \overline{F}; \overline{E}))$$

(2.10)

Though both  $\tau_x$  and  $\tau_y$  contain the successor blocks for partition  $\tau_{AC}$  but partition  $\tau_x$  is said to contain more information. This is because there are lesser number of possible states in successor blocks, i.e. more information about possible next-state(s) from a given predecessor block. Thus there can exist a number of successor partitions containing different degrees of information.

As described perviously, the smallest successor partition for a partition T, i.e. a partition having highest number of blocks or smallest block sizes, is given by m(T). Hence, m(T) describes the largest amount of information that can be obtained from T regarding the next-state of machine-M. In the example partition pairs above,

$\tau_x$  is actually  $m(\tau_{AC})$ . A formal procedure for evaluating m(T) will be described shortly.

The P-dependency condition states that if the next-state variable  $Y_i$  can be computed from the external inputs and a subset  $P_i$  of the state variables, then the product of partitions induced by the subset  $P_i$  should be contained within M of the partition induced by  $y_i$ . Mathematically

$$\prod_{y_j \in P_i} \tau(y_j) \subseteq M[\tau(y_i)] \tag{2.11}$$

where  $\tau(y_k)$  represents the partition induced by variable  $y_k$ . The product is taken over all  $\tau(y_j)$ , such that  $y_j$  is contained in the subset  $P_i$ . The subset is started with minimum number of variables and gradually expanded until the condition is met. The satisfaction of condition means that  $Y_i$  can be derived using the variables used in the subset. Of course, the condition will remain satisfied if the subset is further expanded but we are only interested in minimum number of support variables.

The P-dependency condition is also referred to as information flow inequality [5]. The condition can be efficiently used to find the number of dependencies of state variables. Such a use of the inequality will next be explained using an example.

### An Example

Consider the state machine whose state table is given in Table 2.4. We begin by finding smallest partitions implied by pairs of states. Let  $\tau_{AB}$  be partition that includes a block (AB) and leaves all other states in separate blocks  $(\tau_{AB} = (\overline{AB}; \overline{C}; \overline{D}; \overline{E}))$ . Then, by definition, the smallest such partition containing the block implied by  $\tau_{AB}$  is  $m(\tau_{AB})$ , which can be determined by looking at the successive or next-states of states in  $\tau_{AB}$ . In the present case,

| PS | NS    |       |              | Z            |   |

|----|-------|-------|--------------|--------------|---|

|    | $I_0$ | $I_1$ | $I_3$        | $I_2$        |   |

|    |       |       |              |              |   |

| A  | С     | A     | D            | В            | 0 |

| В  | E     | С     | В            | D            | 0 |

| С  | С     | D     | С            | $\mathbf{E}$ | 0 |

| D  | E     | A     | D            | В            | 0 |

| E  | E     | D     | $\mathbf{C}$ | $\mathbf{E}$ | 1 |

Table 2.4: State Machine - 3.

$$m(\tau_{AB}) = \{ \overline{A, C, E}; \overline{B, D} \} = \tau_1'$$

Clearly,  $(\tau_{AB}, m(\tau_{AB}))$  is a partition pair.

Similarly, the rest of the smallest partitions implied by other pairs of states can be found as follows:

$$m(\tau_{AC}) = m(\tau_{DE}) = (\overline{A, C, D}; \overline{B, E}) = \tau_2'$$

$$m(\tau_{AD}) = m(\tau_{CE}) = (\overline{A}; \overline{B}; \overline{C}, \overline{E}; \overline{D}) = \tau'_{3}$$

$$m(\tau_{AE}) = m(\tau_{CD}) = (\overline{A}, \overline{B}, \overline{C}, \overline{D}, \overline{E}) = \pi(I)$$

$$m(\tau_{BC}) = m(\tau_{BE}) = (\overline{A}; \overline{B}, \overline{C}, \overline{D}, \overline{E}) = \tau'_{4}$$

$$m(\tau_{BD}) = (\overline{A}, \overline{C}; \overline{B}, \overline{D}; \overline{E}) = \tau'_{5}$$

Let the three state variables needed to encode the 8-states be y1, y2 and y3 and their partitions represented as  $\tau_{y1}$ ,  $\tau_{y2}$ ,  $\tau_{y3}$  respectively. Then the problem of state assignment is to encode y1, y2 and y3 such that

$$\tau_{y1}.\tau_{y2}.\tau_{y3} = \pi(0)$$

One such state assignment can be

$$\tau_{y1} = (\overline{A, C, E}; \overline{B, D})$$

$$\tau_{y2} = (\overline{A, B, D}; \overline{C, E})$$

$$\tau_{y3} = (\overline{A, C, D}; \overline{B, E})$$

The corresponding M of the above partitions are found out as follows:

$$M(\tau_{y1}) = \tau_{AB} + \tau_{AD} + \tau_{CE} + \tau_{BD} = (\overline{A}, \overline{B}, \overline{D}; \overline{C}, \overline{E})$$

$$M(\tau_{y2}) = \tau_{AD} + \tau_{CE} = (\overline{A}, \overline{D}; \overline{B}; \overline{C}, \overline{E})$$

$$M(\tau_{y3}) = \tau_{AC} + \tau_{DE} = (\overline{A}, \overline{C}; \overline{B}; \overline{D}, \overline{E})$$

where the operator + is the union of two partitions defined as union of every two blocks in the two partitions provided that the intersection of the two blocks is not empty.

The information flow inequality 2.11 can now be used to find out dependencies of state variables for the given state assignment. The inequality states that dependency of a state variable inducing partition  $\tau_{yi}$  is equal to the smallest subset of the product of partitions  $\tau_{y1}\tau_{y2}\tau_{y3}$  that is lesser or equal to  $M(\tau_{yi})$ . Thus, we see that

$$\tau_{y2} = M(\tau_{y1})$$

$$\tau_{y2}.\tau_{y3} \subset M(\tau_{y2})$$

$$\tau_{y1}.\tau_{y3} \subset M(\tau_{y3})$$

Consequently,  $Y_1$  is dependent on  $y_2$  while  $Y_2$  depends on the information supplied by  $y_2$  and  $y_3$ . Similarly,  $Y_3$  receives its inputs from  $y_1$  and  $y_3$ . This information can be specified as

$$Y_1 = f_1(Inputs, y_2)$$

$$Y_2 = f_2(Inputs, y_2, y_3)$$

$$Y_3 = f_3(Inputs, y_1, y_3)$$

# 2.3 FSM Encoding for Area

The state encoding (or assignment) for an FSM determines complexity of its combinational circuit. The number of storage bits  $n_b$  used to store the state assignment also affects the encoding and so the FSM's complexity. The area of an FSM is further a function of the type of flip-flop being used for storage. Encoding for finite

state machines has traditionally been targeted for reducing the complexity of its combinational part. A good survey of FSM encoding for area can be found in [9].

The use of D-type flip-flops is most prevalent in VLSI circuits today. This work will also be implicitly using D-type flip-flops for storing the finite state machine's state assignment.

The minimum number of state variables needed for state assignment is given as

$$r_0 = \lceil \log_2(s) \rceil \tag{2.12}$$

where s is equal to the number of states of the FSM.

An assignment using the minimum number of state variables has the benefit of using the minimum number of storage devices. However, with such an assignment, there is a potential of reduced flexibility in satisfying the number of encoding constraints (discussed later). The problem is further investigated in [10–15]

Even if minimal state assignments with D-type flip-flops is considered, the number of possible combinations of assignments is exhaustively large [16] given as follows:

$$N = \frac{2^{n_b}!}{(2^{n_b} - s)!} \tag{2.13}$$

Thus, exhaustive evaluation is not a feasible solution for the problem of deriving a good state assignment for all but the smallest machines. Thus, heuristics are generally employed to tackle the problem of FSM state assignment.

Logic minimization aims to optimize the combinational logic of an FSM. This in turn depends on the degree of freedom provided by the state assignment. A good assignment can help the logic minimizer to achieve a better realization in terms of logic cost. Logic minimizers employ different heuristics for two-level and multilevel circuits as their cost measures differ.

A two-level implementation realizes a logic function as a sum of product terms. The circuit complexity of such a representation is related to the number of inputs, outputs, number of product terms and number of variables utilized in a product term, i.e, the number of literals.

The simplest way to encode an FSM is by assigning 1-hot state codes. In 1-hot encoding for a state, the corresponding code bit for a state is set to 1 and all others to 0. Thus, 1-hot encoding is a case of non-minimal state assignment such that the number of variables required is equal to the number of states. It is further noticed [17, 18] that such an encoding is poor to minimizing the size in sum of products representation.

An objective of state encoding could be to reduce dependencies among states [19, 20]. The rationale is that by having dependencies reduced, literal count will decrease and so will interconnect. However, reduced dependencies correlate weakly with the minimality of sum of products representation [21].

The complexity of a two-level realization can be reduced by using mechanisms such as implicant merging, code covering and disjunctive coding [9]. The idea be-

hind *Implicant Merging* (See Table 2.5) is to assign adjacent codes to states that produce either same next-state or output or both at similar input conditions. This yields bigger cubes for performing Karnaugh minimization, and thus results in simpler final expressions. Implicant merging requires adjacency constraints to be met by the state assignment algorithm. Code Covering involves a code word of a state covering a code word of some other state(s), i.e. all the bit positions for which the second code word is 1, correspond to 1 in the first code word. An example utilizing code covering is illustrated in Table 2.6. Assume that  $S_1$  is encoded with 110 and  $S_2$  with 100. In this case, the input condition (s, 001) can be treated as don't care condition for the next-state  $S_2$ , reducing the cover cardinality from three to two. Covering constraints produce covering codewords. Reducing cover cardinality using **Disjunctive Coding** is illustrated in Table 2.7. Disjunctive constraints require that the disjunction of state codes is equal to some other state code. In the example shown, the states are encoded such that the code for  $S_2$  is the disjunction of the state codes for  $S_1$  and  $S_3$ . As such, the second implicant with the input field 101 gets contained in other input conditions and thus is completely saved.

The major difficulty for two-level realization of an FSM is the simultaneous consideration of all the types of constraints [15]. In general, it is not possible to satisfy all the coding conditions with a code using the minimum number of bits  $r_0$ . By increasing the number of code bits to  $r > r_0$ , more coding constraints can be satisfied. The increase in the number of storage elements and state signals to be

| PS                  | I           | NS          | $\mathbf{z}$ |

|---------------------|-------------|-------------|--------------|

| $S_1 \\ S_2 \\ S_3$ | i<br>i<br>i | S<br>S<br>S | O<br>O<br>O  |

| 0                   | i           | S           | О            |

Table 2.5: Merging of three symbolic implicants.

| PS            | I                 | NS                                                   | Z   |

|---------------|-------------------|------------------------------------------------------|-----|

| $S \\ S \\ S$ | 001<br>000<br>01- | $ \begin{array}{c c} S_1 \\ S_2 \\ S_2 \end{array} $ | 0 0 |

| $S \\ S$      | 001               | 110<br>100                                           | 0   |

Table 2.6: Using code word covering.

generated has to be justified against the potential of reducing combinational logic by satisfying additional coding constraints.

The problem with many approaches to two-level assignment is that no exact predictions are possible, as to how the satisfaction of coding conditions affects the complexity of the resulting combinational logic, since the different coding conditions interact with each other in a complex way. The application of coding constraints and finding out their effect would be excessively costly as it would require a huge number of logic minimizations. To mitigate this problem, [12] proposed an elegant

| PS            | I                 | NS                  | $\mathbf{z}$ |

|---------------|-------------------|---------------------|--------------|

| $S \\ S \\ S$ | 001<br>101<br>111 | $S_1 \\ S_2 \\ S_3$ | 0<br>0<br>0  |

| S S           | -01<br>1-1        | 100<br>010          | 0            |

Table 2.7: Using disjunctive codes.

solution of *symbolic minimization*. By using symbolic minimization techniques, it is possible to optimize the function independently of the encoding and determine the codes at a later time. This requires performing the minimization at the symbolic level, before the encoding.

In contrast to two-level circuits, multiple-level (or multilevel) circuits provide much more degree of freedom in optimizing combinational network and satisfying coding constraints. This is because of the flexibility provided due to operations such as common subexpression extraction and factorization. Unfortunately, it also comes with an increase in the difficulty of modeling and optimizing the multilevel network themselves.

The complexity measure for multilevel circuits is the encoding length and the number of literals in the optimized logic network. Since encoding length is mostly taken constant, literal saving by extracting common subexpressions has been the focus of most of the work done for multilevel FSM optimization. This involves find-

ing pairs of states that when encoded carefully can result in extraction of common subexpressions. In contrast to two-level circuits, state pairs in multilevel implementations do not necessarily have to be given adjacent codes for literal savings. If a pair of states have n state-bits in common, those common bits can be extracted to yield a subexpression of n literals. The process thus resulting in a net saving of n-1 literals from the both the states. The exact amount of savings achieved, after incorporating an instance of the extracted subexpression, is given by Literal Savings-1 measure as will be discussed in the next chapter.

The identification of state pairs that can result in maximum amount of literal savings has generated much interest for multilevel FSM optimizations. In this regard, two heuristics algorithms proposed by Devadas et al [22, 23] standout. The first algorithm, called fanout oriented, tries to assign closer codes (lesser Hamming distance) to the state pairs that have similar next-state transitions. The algorithm thus tries to maximize the size of extracted common cube by minimizing the Hamming distance (or distance in short) between such states. In the second approach, referred as fanin oriented, state pairs with higher number of incoming transitions from similar states are given higher weights for proximity in their state assignments. The motivation in this case is to maximize the frequency of common cubes in the encoded next-state functions. The schemes are improved upon in Jedi state assignment heuristic [24]. The fanin oriented approach utilized in [23], also called as Mustang state assignment heuristic, along with Jedi state assignment algorithm

will be discussed in more detail in the next section. Rules for detecting potential common cubes and formulae for more precise evaluation of literal savings have also been proposed and utilized in Muse state assignment algorithm [25].

There have been a few attempts of utilizing Genetic Algorithm for solving state assignment problem [26, 27]. Almaini et al [26] utilize ESPRESSO tool in SIS for their cost calculation which though being accurate is computationally very expensive. Amaral et al [27] used a cost function proposed by Armstrong [28]. Armstrong cost model (Section 2.3.3) combines the properties of fanin and fanout oriented algorithms. The contribution in the above works is in the design of GA for the SAP. However, the authors did not try to take advantage of having the information available due to presence of state assignment in their cost function.

### 2.3.1 Jedi Multilevel Area Measure

In Jedi state assignment heuristic [24], the encoding affinity cost is modeled as a function of how many times a pair of states are represented in next-state and output functions. The cost function of Jedi is given in Equation 2.14.

$$J_{k,l}^{P} = \sum_{i=1}^{m_0} (P_{k,i}^o + P_{l,i}^o) + \frac{n_E}{2} \sum_{i=1}^{n_s} (P_{k,i}^s + P_{l,i}^s)$$

(2.14)

where,

$P_{k,i}^{o}$  is number of times state k is represented in output i,

$P_{k,i}^{s}$  is number of times state k is represented in state i,

$m_o$  is the number of outputs,

$n_s$  is the number of states,

$n_E$  is the number of encoding bits.

For example, consider the state machine in Table 2.4. The next-state equations for states A-E are given as.

$$A = A.I_1 + D.I_1$$

$$B = A.I_2 + B.I_3 + D.I_2$$

$$C = A.I_0 + B.I_1 + C.I_0 + C.I_3 + E.I_3$$

$$D = A.I_3 + B.I_2 + C.I_1 + D.I_3 + E.I_1$$

$$E = B.I_0 + C.I_2 + D.I_0 + E.I_0 + E.I_2$$

and the output equation is given as

$$O_0 = E$$

Here,  $P_{C,D}^s$  is the number of times state C is present in next-state equation of state D which is equal to one. Similarly,  $P_{E,E}^s$  is two.  $P_{C,0_0}^o = 0$  and  $P_{E,0_0}^o = 1$ .

## 2.3.2 Mustang Multilevel Area Measure

In Mustang state assignment heuristic [23], the authors observed that if  $P_{k,i}^{s/o} = 50$  and  $P_{l,i}^{s/o} = 2$ , states k and l will have less common cubes due to the state assignment

than if they were  $P_{k,i}^{s/o} = 26$  and  $P_{l,i}^{s/o} = 26$ , even though the sums are the same. They thus proposed the use of multiplication in place of addition to represent encoding affinity. The cost function of Mustang is given in Equation 2.15

$$M_{k,l}^{P} = \sum_{i=1}^{m_0} (P_{k,i}^o * P_{l,i}^o) + \frac{n_E}{2} \sum_{i=1}^{n_s} (P_{k,i}^s * P_{l,i}^s)$$

(2.15)

Jedi and Mustang both try to reduce the Hamming distance between highly recurring states in the next-state functions. The flip-flop equations employ some of these next-state equations depending on state assignment. Thus, Jedi and Mustang encodings rely on increased probability of states occurring together if they are frequently occurring in next-state functions and try to minimize Hamming distance between them.

It is also possible that two states, though highly recurrent in next-state functions, do not appear together in the flip-flop equations. This is to say that either  $P_{k,i}$  or  $P_{l,i}$  in output or next-state terms is zero. Jedi, because of summation, can give affinity-weight to such a pair of states. However, this situation is more efficiently handled in Mustang by the use of multiplication operation. By multiplying recurrences of pair of states in a next-state equation, Mustang guarantees to give weight to only those pair of states that occur together in a next-state and consequently in flip-flop functions.

### 2.3.3 Armstrong's Multilevel Area Measure

Armstrong [28] defined adjacency cost as a combination of fanout and fanin based approaches. The cost function describing the desired adjacency between state pairs is given by Equation 2.16

$$A_{i,j}^{P} = R_{1} \sum_{l=1}^{s-1} \alpha_{li} \alpha_{lj} \delta_{ij} \qquad StateFanin$$

$$+R_{2} \sum_{a=0}^{c-1} \sum_{l=0}^{s-1} \beta_{lia} \beta_{lja} \delta_{ij} \qquad StateFanout$$

$$+R_{3}M \sum_{b=0}^{v-1} \gamma_{ijb} \delta_{ij} \qquad OutputFanout(Moore)$$

$$+R_{3}(1-M) \sum_{a=0}^{c-1} \sum_{b=0}^{v-1} \Phi_{ijab} \delta_{ij} \qquad OutputFanout(Mealy)$$

$$+R_{4}(\alpha_{ij} + \alpha_{ji}) \delta_{ij} \qquad TieBreaker \qquad (2.16)$$

where c, v and s denote number of input conditions, output variables and states respectively, and

$$\alpha_{lm} = \begin{cases} 1 & \text{if } S_m \subseteq Successor(S_l) \\ 0 & \text{otherwise} \end{cases}$$

$$\beta_{lma} = \begin{cases} 1 & \text{if } S_m \subseteq Predecessor(S_l, I_a) \\ 0 & \text{otherwise} \end{cases}$$

$$\gamma_{ijb} = \begin{cases} 1 & \text{if } Z_b(S_i) = Z_b(S_j) \\ 0 & \text{otherwise} \end{cases}$$

$$\delta_{ij} = \begin{cases} 1 & \text{if } i \neq j \\ 0 & \text{if } i = j \end{cases}$$

$$\phi_{ijab} = \begin{cases} 1 & \text{if } Z_b(S_i, I_a) = Z_b(S_j, I_a) \\ 0 & \text{otherwise} \end{cases}$$

$$M = \begin{cases} 1 & \text{for Moore machines} \\ 0 & \text{for Mealy machines} \end{cases}$$

where  $S_i$  denotes state-i,  $I_a$  being input condition-a, and  $Z_b(S_i)$  and  $Z_b(S_i, I_a)$  denotes outputs in state-i for moore and mealy machine respectively. In case of the mealy-type machine, the output is triggered on the application of input  $I_a$  while being in state-i. The terms  $R_1$ ,  $R_2$ ,  $R_3$  to  $R_4$  are scaling factors. The values for scaling factors used in this work are 4, 3, 2 and 1 respectively.

The first term in the Armstrong's equation gives a weight of  $R_1$  to pair of states that have a common predecessor or a common fanin state. Similarly the second term gives a weight of  $R_2$  to pair of states that fanout to a common next-state. The third and fourth terms add a weight of  $R_3$  to pair of states having similar output at similar input conditions. The two terms for  $R_3$  distinct between Mealy and Moore

types of machines. Finally,  $R_4$  is used as a tie breaker if two states have transitions in between them.

#### An Example

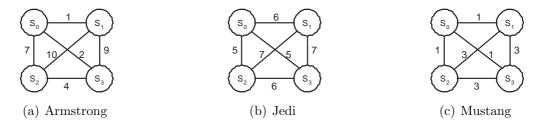

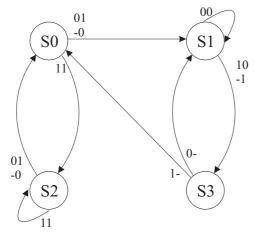

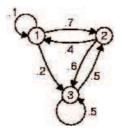

The three cost models described above are next explained by constructing their adjacency (affinity) graphs using state-machine-4 as given in Table 2.8. The adjacency graphs for the three cost models, as shown in Figure 2.1, are detailed next. The weights on arcs in the Figure describe the relative adjacency required by the respective measure.

Consider the weighted arc between states S1 and S2 in Armstrong's graph (Figure 2.1(a)). The weight on the edge is calculated as follows: states  $S_1$  and  $S_2$  have a common predecessor state  $S_0$  so  $R_1$  is added. States  $S_1$  and  $S_2$  are both predecessors of states  $S_3$  so  $S_2$  is added. The state machine is of Mealy type and outputs for both the states at  $S_1$  are same (which is logic-1) so we add  $S_2$ . Finally there are transitions in between the two states and so  $S_2$  is also added. Thus the total arc weight is  $S_1$  is also added. Thus the total arc

The arc between  $S_0$  and  $S_1$  in Figure 2.1(b) is derived as follows: State  $S_0$  does not appear in output equation while  $S_1$  appears twice. Thus the summation of the first term in Equation 2.14 evaluates to 2. States  $S_0$  and  $S_1$  are present in next-state equations of states  $S_1$ ,  $S_2$ , and  $S_3$  while number of encoding bits used is 2. Thus the second term evaluates to 4 and the total arc weight to 6. Similar calculations using

Equation 2.15 lead to the Mustang graph in Figure 2.1(c).

Affinity cost as modeled in adjacency graphs is next used to minimize Equation 2.17.

$$\sum_{i=1}^{n_s} \sum_{j=1}^{n_s} A_{i,j}^P \cdot \Delta(i,j)$$

(2.17)

where  $\Delta(i, j)$  is the Hamming distance between codes of state i and j

$A_{i,j}^P$  being the affinity as given by Jedi, Mustang or Armstrong by their respective equations.

State encoding is next determined by *embedding* the corresponding weighted graph in a Boolean space of appropriate dimensions. Since graph-embedding is an intractable problem, heuristic algorithms are used to determine an encoding where pairwise code distance correlates reasonably well with their affinity weight (the higher the weight, the lower the distance). *Simulated Annealing* algorithm is therefore used by Jedi in solving Equation 2.17. Mustang provides a constructive algorithm for the purpose whereas Amaral [27] used GA in solving Armstrong's affinity graph.

## **2.3.4** Expand

Expand-function as used in ESPRESSO tool [29] is also utilized in this work as a cost measure for multilevel area estimation. The Expand-function is discussed in

Figure 2.1: Adjacency Graphs.

| PS    | N     | IS    | 2     | Z     |

|-------|-------|-------|-------|-------|

|       | I = 0 | I = 1 | I = 0 | I = 1 |

| $S_0$ | $S_1$ | $S_2$ | 0     | 0     |

| $S_1$ | $S_2$ | $S_3$ | 1     | 1     |

| $S_2$ | $S_1$ | $S_3$ | 1     | 0     |

| $S_3$ | $S_3$ | $S_1$ | 0     | 1     |

Table 2.8: State Machine - 4.

detail in the next chapter.

# 2.4 FSM Encoding for Low Power

Power dissipation has always been one of the major concerns in logic circuits design. Excessive power dissipation often causes chip run-time failure, reduction in chip life-time, and costs more expensive packaging. In recent times, portable electronics applications have given power-aware computing a whole new importance. This is due to the fact that limitations in battery capacities and progress trail far behind the ever increasing computing requirements. Power consumption is thus constrained and optimized at all levels of design hierarchy including technology se-

lection, architectural transformation, logic synthesis and physical design [3]. VLSI designers have thus been faced with another optimization parameter of low-power. Recently, a lot of work is reported in the literature to automate the exploration of low power solutions at different levels of VLSI hierarchy [3,30].

### Power Estimation for FSMs

The exact power consumption of a VLSI device is a complex function of many parameters and thus can only be accurately found out by running numerous power simulations on the final device. However, a simpler measure for power dissipation by a CMOS logic gate is generally given by the following equation.

$$P_{ave} = \frac{C_L V dd^2 E_{SW}}{2.T_{cur}} \tag{2.18}$$

where  $T_{cyc}$  is the cycle time  $(1/f_{clk})$ ,  $C_L$  is the physical capacitance at the output of a node and  $E_{SW}$ , referred to as switching activity, is average number of logic transitions at the node per cycle time. The switching-capacitance (or switchedcapacitance) is defined as product of physical capacitance  $C_L$  and the average data activity  $E_{SW}$  which describes the average capacitance charged/discharged during each clock cycle.

The major source of power consumption in CMOS circuits is due to charging and discharging of the circuit capacitances. Thus, power consumption of a circuit can be reduced by either reducing the total switching in the logic or by reducing the logic (capacitance) or both of them, i.e. by reducing their product, switching-capacitance.

The major source of power consumption in CMOS circuits is due to charging and discharging of the circuit capacitances which can be expressed as

where  $T_{cyc}$  is the cycle time,  $C_L$  the load capacitance of a CMOS gate and  $E_{SW}$  being the expected switching activity at the gate's outputs.

The above equation shows that by reducing switching, supply voltage or capacitance seen by the gate, the power consumption of a CMOS device can be reduced.

There is a rich amount of work reported in the literature for power estimation of sequential circuits [31–34]. The power estimation techniques can be broadly classified into statistical [35] or probabilistic [36]. Both the approaches are implemented in SIS [37] version 1.2. The statistical approaches work by simulating the state machine using the user provided input vectors and determining the state probabilities based on it. Probabilistic approaches on the other hand try to correlate the various probabilities in order to calculate state probabilities if the FSM is simulated for infinite amount of time. Statistical techniques can be fast and accurate if a short representative sequence for an FSM can be determined. However, determining such a sequence is an open research problem. Najm in [38] reports a statistical power estimation technique using randomly generated input sequences until a desired accuracy is achieved. Najm et al in [39] propose a technique to estimate power within a desirable accuracy of an FSM by simulating fraction of a large input set. The technique tries to simulate FSM repeatedly by blocks of consecutive vectors at random

until a desired accuracy is achieved. A Monte-Carlo approach for power estimation for sequential circuits is also proposed [40]. The technique generates mutually independent power samples using multiple copies of the circuit that are simulated in parallel with mutually independent input vector streams. Samples are collectively analyzed to check for the terminating condition.

The power estimation problem is addressed even at a more higher level using entropy as power estimating function [41,42]. The rationale is that since entropy is a measure of information-carrying capacity, a higher entropy on a state line means higher number of transitions on it. The maximum transition can be attributed when the probability on a line is exactly half and corresponds to its maximum entropy value.

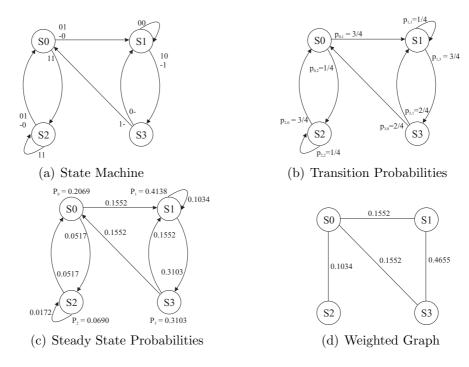

A state transition graph (STG) is denoted by G(V, E) where a vertex  $S_i \in V$  represents a state of the FSM and an edge  $e_{i,j} \in E$  represents a transition from state  $S_i$  to  $S_j$ . Let  $P_{S_i}$  denote the state probability, that is, the probability of finding the state machine in  $S_i$  at any given time, and  $p_{ij}$  denotes the conditional (state) transition probability, which is the probability of the machine making a transition from state  $S_i$  to state  $S_j$ , that is

$$p_{ij} = Probability(Next = S_j | Present = S_i)$$

(2.19)

A STG can be interpreted as a Markov chain. A Markov chain is a representation

of a finite state Markov process [43]. A Markovian process is termed as memoryless since the probability distribution at any time depends only on the present time and not on how the process arrived till that period. For a large class of Markovian processes, in which the STG is also a member, the probability of a state is the limiting value approached as the FSM is operated for infinite amount of time. This is termed as *limiting state probability theorem* [44]. Mathematically,

$$P_{Sj} = limit_{t->\infty} p_{ij} P_{Sj}(t) \tag{2.20}$$

The above can be iteratively calculated by solving Chapman-Kolmogorov equations [45] as follows:

$$P_{Si}(n+1) = \sum_{j \in In\_State(i)} p_{ji} P_{Sj}(n)$$

$$i = 1, 2, \dots, M-1$$

$$1 = \sum_{j} P_{Sj}(n+1)$$

(2.21)

where n is iteration number and  $In\_State(i)$  is the set of fanin states for state-i in the STG.

The process is terminated once state probabilities converge so that the difference between successive iterations is within a user defined tolerance value. To tackle the complexity of solving the above system of equations, approximate methods have been proposed in [46, 47].

The Total State Transition Probability for a transition from a state  $S_i$  to state  $S_j$  is the probability that the machine transits to state  $S_j$  given that it is in state  $S_i$ . The total state transition probability can thus be calculated [48] as follows:

$$P_{ij} = p_{ij}.P_{Si} \tag{2.22}$$

where  $P_{ij}$  is the total state transition probability from state  $S_i$  to state  $S_j$ .

The sum of total state transition probabilities in between two states indicates the amount of switching in between them. This sum can be treated as a weight between the two states attributed on a single edge connecting them.

$$W_{ij} = P_{ij} + P_{ji} (2.23)$$

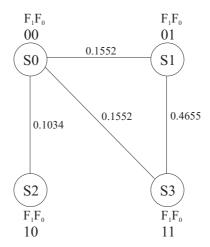

A STG in which all the transitions between two states are replaced with a weighted edge is called a weighted graph. The weight on an edge indicates the relative proximity in the state assignment of the two connected states on that edge. By assigning shorter distance codes to states connected with higher weights, i.e higher transition probability, the overall switching on the state lines of the FSM can be minimized. Thus a cost model for minimizing power consumption can be to have Minimum Weighted Hamming Distance (MWHD). Mathematically, this can be achieved by minimizing Equation 2.24

$$\sum_{S_i S_j \in S} W_{ij} H(S_i, S_j) \tag{2.24}$$