COE 561 Term 081

HW# 4 Solution

**Q.1.** Consider a technology library containing the following cells:

| Cell                                 | Area Cost |

|--------------------------------------|-----------|

| INV(x1) = x1'                        | 1         |

| NAND2(x1, x2) = (x1 x2)'             | 2         |

| NAND3(x1, x2, x3) = $(x1 x2 x3)$ '   | 3         |

| NOR2(x1, x2) = (x1 + x2)'            | 2         |

| AOI21(x1, x2, x3) = $((x1 x2) + x3)$ | 3         |

| OAI21(x1, x2, x3) = $((x1+x2) x3)$ ' | 3         |

(i) Show the **pattern trees** of the library cells using **NAND2** and **INV** as base functions. Assume that symmetric representations do not need to be stored.

| -   | Cell     | gate         | Pattern tree | cost |

|-----|----------|--------------|--------------|------|

| ŧ1  | INV      | _ <b>b</b> _ | <b>⊕</b>     | 1    |

| -t2 | NAND2    | <b>−</b> CF  |              | 2    |

| Ęŝ  | NAND3    | Dona Do-     |              | 3    |

| Łψ  | NOR2     | -to-Da-to-   |              | 2    |

| t5  | 40I3I    | =0-10-       |              | 3    |

| 46  | OAI 21 . | \$D-7        |              | 3    |

|     |          |              | ,            |      |

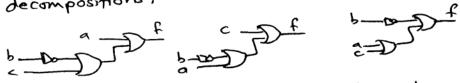

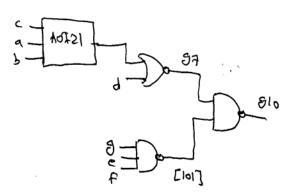

(ii) Decompose the function f = a + b' + c using NAND2 and INV as base functions into all possible **non-symmetric decompositions**. Then, **map** the decomposed circuits using the given library and determine the decomposition that leads to a lower area cost.

The function f = a + b + c can be decomposed into 2-input or gates by one of the following decompositions;

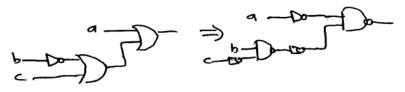

The first and second decompositions have the same structure and will lead to a solution of the same cost. So, we will consider mapping the first and third decompositions.

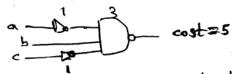

The minimum solution for mapping this decomposition has a cost of 5 as shown below:

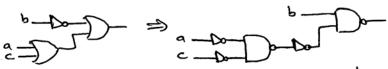

Next, we consider the third decomposition.

The minimum solution for mapping this decomposition has a cost of 4 as shown below:

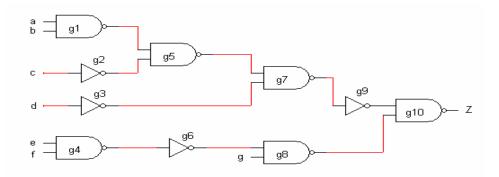

(iii) Using the dynamic programming approach, **map** the circuit given below using the given library into the **minimum area** cost solution. Inputs are  $\{a, b, c, d, e, f, g\}$  and output is  $\{Z\}$ .

| Match      | gate                                                                                                                                                  | cost                                                                                                                                                                                     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>+</b> 2 | Nandz(a,b)                                                                                                                                            | 2                                                                                                                                                                                        |

| ŧ1         | INV(c)                                                                                                                                                | 1                                                                                                                                                                                        |

| tı         | (NV(d)                                                                                                                                                | 1                                                                                                                                                                                        |

| t2         | Nandz (ef)                                                                                                                                            | 2                                                                                                                                                                                        |

| t2         | Nand2 (81,92)                                                                                                                                         | 2+2+1=5                                                                                                                                                                                  |

| 61         | INV (84)                                                                                                                                              | 1+2=3                                                                                                                                                                                    |

| £2         | Nandz (95,93)                                                                                                                                         | 2+5+1=8                                                                                                                                                                                  |

| +2         | Nonda (96,8)                                                                                                                                          | 2+3=5                                                                                                                                                                                    |

| 43         | Nond3 (exf.g)                                                                                                                                         | 3                                                                                                                                                                                        |

| ŧ,         | INV (24)                                                                                                                                              | 1+8=9                                                                                                                                                                                    |

| ۴s         | AOI21 (31,32,d)                                                                                                                                       | 3+2+1= =                                                                                                                                                                                 |

| t2         | Nonda (90,98)                                                                                                                                         | 2+6+3=11                                                                                                                                                                                 |

| £3         | Nand 3 (95,03,98                                                                                                                                      | -                                                                                                                                                                                        |

|            | t <sub>1</sub> t <sub>1</sub> t <sub>2</sub> t <sub>2</sub> t <sub>2</sub> t <sub>2</sub> t <sub>2</sub> t <sub>3</sub> t <sub>1</sub> t <sub>5</sub> | to Nondo (0,0)  to INV(c)  to INV(d)  to Nondo (e,f)  to Nondo (9,92)  to INV (94)  to Nondo (95,93)  to Nondo (96,9)  to Nondo (e,f,9)  to INV (94)  to Nondo (e,f,9)  to Nondo (94,98) |

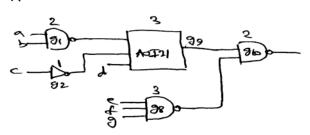

Thus, the minimum cost is !! and the mapped solution is shown below;

(iv) Using the given library, use the SIS command *read\_libray* q1.lib to read the library. Then, map the circuit to the library using the sis command *map -s -m 0*. Compare your solution to the solution obtained in (iii). You can save the mapped circuit using the sis command *write\_blif -n*. Why do you think the solution obtained by SIS is better than your solution?

The solution achieved by SIS is given below with a total area of 10.

```

.model hw4q1_081.blif

.inputs a b c d e f g

.outputs g10

.default_input_arrival 0.00 0.00

.default_output_required 0.00 0.00

.default_input_drive 0.20 0.20

.default_output_load 1.00

.default_max_input_load 999.00

.gate NAND3 a=g b=e c=f O=[101]

.gate AOI21 a=c b=a c=b O=g5

.gate NOR2 a=d b=g5 O=g7

.gate NAND2 a=[101] b=g7 O=g10

.end

```

The obtained solution is better than the solution we obtained because SIS uses an additional optimization technique by inserting pairs of inverters at each line in the subject graph and then finding an optimal mapping of the subject graph. Any mapped pair of inverters can then be eliminated. Using this technique it is possible to obtain a better mapping of the given network.

(v) Assuming **Boolean matching**, determine the <u>number</u> of ROBDD's that need to be stored in the cell library for each of the following cells. <u>Justify your answer</u>.

a.

$$f=ab+ac+bc$$

Since a, b, and c are all symmetric

$C_3 = \{(a,b,c)\} \implies \# Robbobs = 1$

b.

$$f = a b c + a' b' d$$

we have 2 binate variables 20,69 and 2 unate variables &c,d3

Variables a and 5 are symmetric,

PROBIDD'S = 2

**Q.2.** Consider the incompletely-specified FSM that has 6 states, two inputs and one output, represented by the following state table:

| <b>Present State</b> | Next State, Output |       |       |       |

|----------------------|--------------------|-------|-------|-------|

|                      | 00                 | 01    | 11    | 10    |

| S1                   | S2, 0              | -,-   | S5, 1 | -,-   |

| S2                   | S1, 0              | S3, - | -,-   | -,-   |

| S3                   | S3, -              | S1, 1 | S5, - | S4, 1 |

| S4                   | -,-                | S2, - | S1, - | -,-   |

| S5                   | S3, -              | S2, 1 | -, 0  | S6, - |

| S6                   | S6, 1              | S1, - | S2, - | S5, - |

(i) Determine the incompatible and the compatible states along with their implied pairs.

52

53

$$(52,53)$$

$(51,55)$

$(52,53)$

$(51,55)$

$(51,55)$

$(51,55)$

$(51,55)$

$(51,55)$

$(51,55)$

$(51,55)$

$(51,55)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$(51,52)$

$($

The incompatible states are; (\$1,54), (\$1,56), (\$2,56), (\$3,54)

The compatible states with their implied pairs:

$$(51,52)$$

$(51,53)$   $\leftarrow$   $(52,53)$

$(52,53)$   $\leftarrow$   $(51,53)$

$(52,54)$   $\leftarrow$   $(52,53)$

$(52,55)$   $\leftarrow$   $(51,53)$ ,  $(52,53)$

$(53,55)$   $\leftarrow$   $(51,52)$ ,  $(54,56)$

$(53,56)$   $\leftarrow$   $(52,55)$ ,  $(54,55)$

$(54,56)$   $\leftarrow$   $(51,52)$

$(54,56)$   $\leftarrow$   $(51,52)$

$(55,56)$   $\leftarrow$   $(51,52)$

(ii) Compute the maximal compatible classes along with their implied state pairs.

Maximal compatible classes:

NE ASSIGN for every stake

$$S_i$$

variable  $X_i$ .

NE ASSIGN for every stake  $S_i$  variable  $X_i$ .

NE ASSIGN for every stake  $S_i$  variable  $X_i$ .

NE ASSIGN for every stake  $S_i$  variable  $X_i$ .

From the incompatible stake pairs we have  $(X_1 + X_1)(X_1 + X_2)(X_1 + X_3)(X_2 + X_4)(X_3 + X_4)$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_3 + X_4)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_3 + X_4)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_5X_6)(X_1 + X_6)(X_2 + X_6)(X_3 + X_4)$$

$$= (X_1 + X_1X_6X_6)(X_1 + X_6)(X_1 + X_6)(X_1 + X_6)$$

$$= (X_1 + X_1X_6X_6)(X_1 + X_1X_6)(X_1 + X_1X_6)$$

$$= (X_1 + X_1X_6X_6)(X_1 + X_1X_6)(X_1 + X_1X_6)$$

$$= (X_1 + X_1X_6X_6)(X_1 + X_1X_6)($$

(iii) Reduce the state table into the minimum number of states and show the reduced state table.

**Q.3.** Consider the incompletely-specified FSM that has 4 states, two inputs and two outputs, represented by the following state table:

| Product | Input | Present State | Next State | Output |

|---------|-------|---------------|------------|--------|

| P1      | 10    | S1            | S2         | 11     |

| P2      | 00    | S2            | S2         | 11     |

| P3      | 01    | S2            | S2         | 00     |

| P4      | 00    | S3            | S2         | 00     |

| P5      | 10    | S2            | S1         | 11     |

| P6      | 10    | S3            | <b>S</b> 1 | 11     |

| P7      | 00    | S1            | S1         |        |

| P8      | 01    | S3            | S0         | 00     |

| P9      | 11    | S1            | S1         | 10     |

| P10     | 11    | S3            | <b>S</b> 3 | 01     |

| P11     | 11    | S0            | S0         | 11     |

(i) Assuming the following constraints, S0 = S1 OR S3, and that the code of S2 is covered by all other state codes, the state table can be reduced into the table shown below. Using implicant merging, covering and disjunctive relations show step by step how you can obtain the reduced state stable given below.

| Input | Present State | Next State | Output |

|-------|---------------|------------|--------|

| -0    | S1, S2        | S2         | 11     |

| 10    | S2, S3        | S1         | 11     |

| 00    | S1            | S1         |        |

| 01    | S3            | S0         | 00     |

| 11    | S0, S1        | S1         | 10     |

| 11    | S0, S3        | S3         | 01     |

(ii) Show the encoding constraint matrix and compute all the seed dichotomies of the encoding constraint matrix. Then, eliminate seed dichotomies that violate the given covering and disjunctive constraints.

Encoding constraint Matrix:

$$A = \begin{bmatrix} 0 & 1 & 1 & 0 \\ 0 & 0 & 1 & 1 \\ 1 & 1 & 0 & 0 \\ 1 & 0 & 0 & 1 \end{bmatrix}$$

## Seed Dichotomies:

SIA:

$$(51,52)$$

,  $(50)$  X

SZA:  $(51,52)$ ,  $(53)$  X

SIB:  $(50)$ ,  $(51,52)$

SZB:  $(53)$ ,  $(51,52)$

SZB:  $(53)$ ,  $(51,52)$

SZB:  $(53)$ ,  $(51,52)$

SZB:  $(53)$ ,  $(51)$  X

SZB:  $(53)$ ,  $(51)$  X

SZB:  $(52)$ ,  $(51)$  X

SZB:  $(52)$ ,  $(51)$  X

SZB:  $(52)$ ,  $(52)$ ,  $(52)$  X

SZB:  $(52)$ ,  $(52)$ ,  $(52)$  X

SZB:  $(52)$ ,  $(52)$ ,  $(53)$  X

SZB:  $(52)$ ,  $(52)$ ,  $(53)$  X

SZB:  $(52)$ ,  $(52)$ ,  $(53)$  X

SZB:  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$ ,  $(52)$

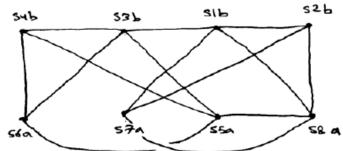

(iii) Compute all the prime dichotomies and eliminate those that violate the disjunctive constraints.

Prime Dichotomies:

P1: (SIb, S2b, S7a, S8a): (S0, S3), (S1, S2)

P2: (S3b, S4b, S5a, S6a): (S0, S1), (S2, S3)

P3: (S5a, S8a): (S0, S1, S3), (S2)

P4: (S1b, S3b): (S0), (S1, S2, S3)

Note that P4 violates the disjunctive constraint Note that P4 violates the disjunctive constraint and has to be discarded. Also, P3 violates and has to be discarded. Also, P3 violates the disjunctive constraint if we assume 2-bits encoding.

(iv) Find a state encoding satisfying the given constraints. Verify that your encoding satisfies all the constraints.

A minimum cover is pl and pr which results in the following state encoding

| state     | code |  |

|-----------|------|--|

| So        | 1 1  |  |

| SI        | 0    |  |

| 52        | 0 0  |  |

| <b>S3</b> | 1 0  |  |

Note that the disjunctive constraint so = SIORS3

is satisfied since II = 01 or lo.

Also, the code of s2 = 00, which is covered

by all other codes.

Also, si.s2 = 0-, which does not intersect

with other codes.

52.53 = -0, which does not intersect

with other codes.

Sois1 = -1, which does not intersect

with other codes.

sois3 = 1-, which does not intersect

with other codes.

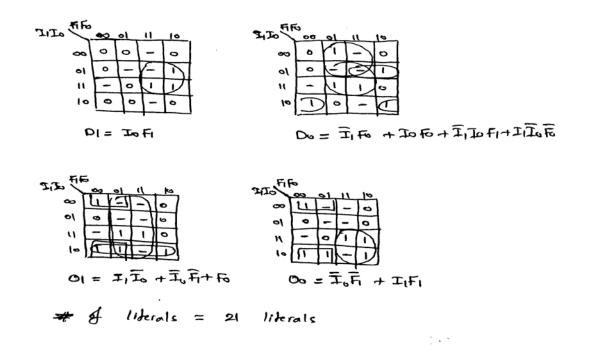

(v) Using K-MAP, obtain the equations for the output and flip-flops. Compare your solution to the solution obtained by running the SIS command *stg\_to\_network* using the state codes obtained in (iii).

The circuit resulting based on the stg\_to\_network command is as follows:

```

sis> read_blif hw4q3_081.blif sis> stg_to_network sis> print  [0] = IN_0 IN_1 LatchOut_v2 + IN_0' IN_1 LatchOut_v2 \\ [1] = IN_0 IN_1' LatchOut_v3' + IN_0' IN_1 LatchOut_v2 + IN_0' LatchOut_v3 + IN_1 LatchOut_v3 \\ \{OUT_0\} = IN_0 IN_1' LatchOut_v3' + IN_1 LatchOut_v3 + IN_1' LatchOut_v2' \\ \{OUT_1\} = IN_0 IN_1 LatchOut_v2 + IN_0 IN_1' LatchOut_v3' + IN_1' LatchOut_v2' \\ sis> print_stats \\ hw4q3_081 \quad pi=2 \quad po=2 \quad nodes=4 \quad latches=2 \\ lits(sop)=31 \ \#states(STG)=4

```

Note that the number of literals is more than what we have obtained using K-map because the objective here is to minimize the number of products and not the number of literals. To optimize the number of literals, we need to do single output optimization using the command stg\_to\_network –e 2 which produces the following circuit:

```

sis> read_blif hw4q3_081.blif

sis> stg_to_network -e 2

sis> print

[0] = IN_1 LatchOut_v2

[1] = IN_0 IN_1' LatchOut_v3' + IN_0' IN_1 LatchOut_v2 + IN_0' LatchOut_v3

+ IN_1 LatchOut_v3

{OUT_0} = IN_0 IN_1' + IN_1' LatchOut_v2' + LatchOut_v3

{OUT_1} = IN_0 LatchOut_v2 + IN_1' LatchOut_v2'

sis> print_stats

hw4q2_081 pi= 2 po= 2 nodes= 4 latches= 2

lits(sop)= 21 #states(STG)= 4

```

(vi) Perform state assignment using the program nova by running the SIS command *state\_assign nova*. Compare the obtained solution to your solution in (v) in terms of number of literals.

The result produced is as follows which is worse that the solution obtained in (v).

```

sis> read_blif hw4q3_081.blif

sis> state assign nova

Running nova, written by Tiziano Villa, UC Berkeley

sis> print

{OUT 0} = IN 0 IN 1' LatchOut v2' + IN 1 LatchOut v2 LatchOut v3 + IN 1' LatchOut v2 +

IN_1' LatchOut_v3' + LatchOut_v2 LatchOut_v3'

\{OUT_1\} = IN_0 LatchOut_v2' + IN_1' LatchOut_v2 + IN_1' LatchOut_v3' + LatchOut_v2' + IN_1' LatchOut_v2' + IN_1'

LatchOut_v3'

v4.0 = IN 0 IN 1' LatchOut v2' + IN 0' IN 1 LatchOut v3 + IN 0' LatchOut v2+ IN 1

LatchOut v2 LatchOut v3 + LatchOut v2 LatchOut v3'

v4.1 = IN_0 LatchOut_v2' + IN_0' LatchOut_v2 + IN_1 LatchOut_v2 LatchOut_v3

sis> print stats

hw4q3_081

pi=2 po=2 nodes=4

latches= 2

lits(sop) = 40 \#states(STG) = 4

```

The state assignment generated by nova is:  $\{S0 = 10, S1 = 11, S2 = 00, S3 = 01\}$ .

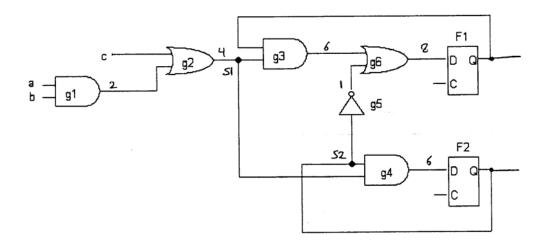

**Q.4.** Consider the following circuit with inputs {a, b, c} and outputs {F1, F2}. Assume that the delay of an Inverter is 1 unit delay, the delay of a 2-input AND gate is 2 unit delays, and the delay of a 2-input OR gate is 2 unit delays. Consider the circuit given below:

(i) Determine the critical path of this circuit and the maximum propagation delay.

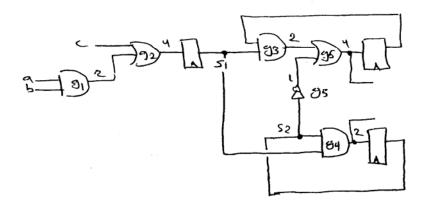

(ii) Using only the **Retiming** transformation, reduce the critical path of this circuit with the minimum number of flip-flops possible.

The resulting circuit after retiming is .

It is clear that the critical path of the retimed circuit is 4 delay units.

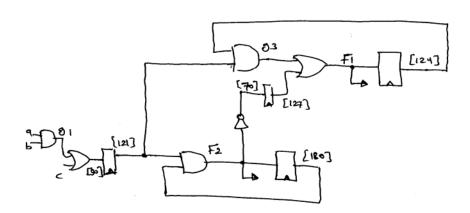

(iii) Read the library q4.lib using the command *read\_library q4.lib*. Then, map your design to the library using the command *map -s*. Then, retime the circuit using the command *retime -i*. Compare the maximum arrival time before and after retiming. Compare the obtained solution to the solution you obtained in (ii).

The result of applying the retiming transformation is given below:

final cycle delay = 4.00final number of registers = 4final logic cost = 11.00final register cost = 64.00

RETIME: Final cycle time achieved = 4.00

The resulting circuit is:

.model hw4q4\_081.blif

.inputs a b c

.outputs f1 f2

.default\_input\_arrival 0.00 0.00

.default\_output\_required 0.00 0.00

.default\_input\_drive 0.00 0.00

.default\_output\_load 1.00

.default\_max\_input\_load 999.00

.mlatch dff\_re D=[90] Q=[121] NIL 3

.mlatch dff\_re D=f1 Q=[124] NIL 3

```

.mlatch dff_re D=[70] Q=[127] NIL 3

.mlatch dff_re D=f2 Q=[130] NIL 3

.gate and2 1A=a 1B=b O2=g1

.gate or2 1A=c 1B=g1 O1=[90]

.gate and2 1A=[121] 1B=[124] O2=g3

.gate inv 1A=f2 O=[70]

.gate or2 1A=g3 1B=[127] O1=f1

.gate and2 1A=[121] 1B=[130] O2=f2

.end

```

Note that the number of registers obtained by SIS is different due to our description of the circuit having the fanout connecting to G5 not coming directly from F2. This is why we were able to minimize the number of registers more than what the tool could have done. If we have connected F2 to a buffer representing S2 and then let S2 fanout, SIS will obtain the same solution we have obtained.