## COMPUTER ENGINEERING DEPARTMENT

#### **COE 561**

#### **Digital System Design and Synthesis**

#### **Final Exam**

(Open Book Exam)

First Semester (111)

Time: 7:00-10:00 PM

| Student Nam | e : _KEY |  |  |

|-------------|----------|--|--|

|             |          |  |  |

| Student ID. | :        |  |  |

| Question | Max Points | Score |

|----------|------------|-------|

| Q1       | 20         |       |

| Q2       | 22         |       |

| Q3       | 21         |       |

| Q4       | 12         |       |

| Q5       | 25         |       |

| Total    | 100        |       |

# $(\ensuremath{\mathbf{Q1}})$ Consider a technology library containing the following cells:

| Cell                                          | Area Cost | Gate |

|-----------------------------------------------|-----------|------|

| INV(x1) = x1'                                 | 1         | ->   |

| $NAND2(x1, x2) = (x1 x2)^{\circ}$             | 2         |      |

| NAND3(x1, x2, x3) = (x1 x2 x3)'               | 3         |      |

| NOR2(x1, x2) = (x1 + x2)                      | 2         |      |

| NOR3(x1, x2, x3) = $(x1 + x2 + x3)$ '         | 3         |      |

| AOI21(x1, x2, x3) = $((x1 x2) + x3)$ '        | 3         |      |

| AOI22(x1, x2, x3, x4) = $((x1 x2) + (x3 x4))$ | 4         |      |

| OAI21(x1, x2, x3) = $((x1+x2) x3)$            | 3         |      |

| OAI22(x1, x2, x3, x4) = $((x1+x2)(x3+x4))$    | 4         |      |

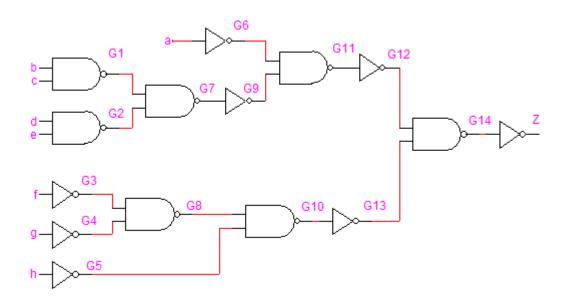

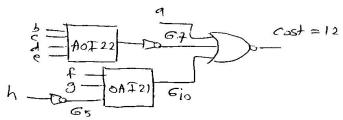

(i) Consider the circuit given below with inputs  $\{a, b, c, d, e, f, g, h\}$  and output  $\{Z\}$ . Using the dynamic programming approach and **Structural Matching**, map the circuit using the given library into the **minimum area** cost solution.

- (ii) Can you obtain a better mapping than the one obtained in (i). If the answer is yes, show the better solution and explain how it is obtained.

- (iii) Assuming **Boolean Matching**, determine the <u>number</u> of ROBDD's that need to be stored in the cell library for the following cell. <u>Justify your answer</u>.

$$Y = a b c d + a' b' c d + e f + e' g$$

| CiD | vertex    | gate          | cost       |

|-----|-----------|---------------|------------|

|     | GI        | Nandz (b,c)   | 2          |

|     | 62        | Norda (die)   | 2_         |

|     |           | 1NV (f)       | ı          |

|     | <u>G3</u> | 1NV (9)       | 1          |

|     | 64        | INV(h)        | l          |

| **  | G 5       | INV (a)       | 1          |

|     | GG        |               | 2+2+2=6    |

|     | 67        | Nand2 (31,62) | 2 +1+1 = 4 |

| •   | G8        | Nand2 (63,64) |            |

|   | vertex | gate                 | cost              |

|---|--------|----------------------|-------------------|

|   | 69     | INV (67)             | 1+6 =7            |

|   |        | AOI22(b,c,d,e)       | 4                 |

|   | 610    | Nond 2 (G8, G5)      | 2+4+1=7           |

|   |        | 0AI21 (f,g, G5)      | 3+1=4             |

| , | GII    | Nard2 (65, 69)       | 2+1+4=1           |

|   |        | Nand3(66,61,62)      | 3 + 1 + 2 + 2 = 8 |

|   | 210    | 1NV (GII)            | 1+7=8             |

|   | G12    | NOR2 (a, 67)         | 2+6=8             |

| - |        |                      |                   |

|   | 613    | 1NV (610)            | 1+4=5             |

|   |        | AOI21(B3,G4,h)       | 3+1+1=5           |

| - |        | Nand2 (612,613)      | 2 + 8 + 5 = 15    |

|   | 614    | Nand 3 ( G5, G9, G13 |                   |

|   |        | Nand3 (612, 68, 65   | ) 3+8+4+1=6       |

|   | 7      | INV (614)            | 1 + 13 = 14       |

|   | -      | NOR2 (GIL, GIO)      | 2 +7 +4 = 13      |

|   |        | NOR3 (610, a, G7)    | 3+4+6=13          |

|   |        |                      |                   |

minimum area cost of 13.

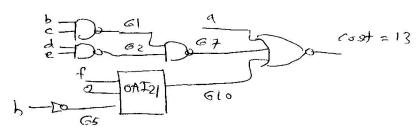

One minimal area solution is;

(ii) Yes, a better solution with a cost of 12

This solution is obtained by adding a cascade of inverters at the subput of G7.

(iii)

$$G = \{ (e), (f), (g) \}$$

$G = \{ (a,b), (c,d) \}$

Thus, number of ROBDOIS needed is 2! = 2

(Q2) Consider the incompletely-specified FSM that has 5 states, one input (X) and one outputs (Z), represented by the following state table:

| <b>Present State</b> | Next State, Z |       |  |

|----------------------|---------------|-------|--|

|                      | X=0           | X=1   |  |

| S0                   | S3, –         | S0, – |  |

| S1                   | S4, 0         | S0, – |  |

| S2                   | S3, 0         | S1, – |  |

| S3                   | S2, -         | S2, - |  |

| S4                   | S2, 1         | S1, – |  |

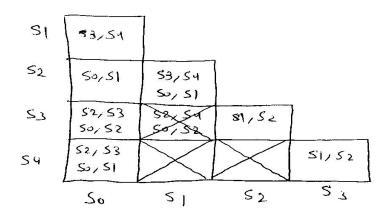

- (i) Determine the incompatible states and the compatible states along with their implied pairs.

- (ii) Compute the maximal compatible classes along with their implied state pairs.

- (iii) Compute the prime compatibility classes along with their implied state pairs.

- (iv) Reduce the state table into the minimum number of states and show the reduced state table.

The compatible states with their implied pairs are:

$$(S1,S2) \leftarrow (S3,S4)$$

and  $(S0,S1)$

$$(53,54) \in (51,52)$$

# (ii) Maximal Compatible Classes:

From the incompatible state pairs, we have;

$$= \overline{S_1} \, \overline{S_2} \, + \overline{S_1} \, \overline{S_4} \, + \overline{S_2} \, \overline{S_3} \, \overline{S_4} \, + \overline{S_3} \, \overline{S_4}$$

Thus, the maximal compatible classes along with their implied state pairs are;

$$(S_0, S_3, S_4) \leftarrow (S_0, S_2), (S_2, S_3), (S_0, S_1), (S_1, S_2)$$

# (1111) Prime Compatibility Classes

In addition to the maximal compatible classes, we have the following prime classes;

$$(52, 53) \in (52, 53), (50, 52)$$

$$(50,54) \neq (52,53), (50,51)$$

$$(53,54) \leftarrow (51,52)$$

(50)

(51)

(52)

(S3)

(S4)

(iv) The following minimum cover can be used which satisfies the closure;

Thus, the state machine can be reduced to

| $\rho_{eS}$ | Next State, Z |          |

|-------------|---------------|----------|

|             | X=0           | × = 1    |

| 50,1,2      | S3,4,0        | So,1,2,- |

| S 3,4       | 50,1,23       | 50,1,2 - |

(Q3) Consider the given FSM which has 4 states, one input and one output, represented by the following state table:

| Product | Input | Present State | Next State | Output |

|---------|-------|---------------|------------|--------|

| P1      | 0     | S1            | S2         | 0      |

| P2      | 1     | S1            | S2         | 0      |

| P3      | 0     | S2            | S2         | 0      |

| P4      | 1     | S2            | S3         | 0      |

| P5      | 0     | S3            | S4         | 0      |

| P6      | 1     | S3            | S3         | 0      |

| P7      | 0     | S4            | S4         | 0      |

| P8      | 1     | S4            | S1         | 1      |

(i) Assuming the following constraints: S3 covers S2, and that the code of S4 is covered by all other state codes, the state table can be reduced into the table given below. Using implicant merging and covering relations show step by step how you can obtain the reduced state stable given below:

| Input | Present State | Next State | Output |

|-------|---------------|------------|--------|

| _     | S1, S2        | S2         | 0      |

| 1     | S2, S3        | S3         | 0      |

| 1     | S4            | S1         | 1      |

(ii) Compute all the seed dichotomies and construct their compatibility graph. Find a minimum cover for the seed dichotomies. Based on the found cover, derive an encoding satisfying the given constraints with minimal bit length.

Next, I and 13 can be merged using implicant merging into the following row:

fy \_ S1, S2 S2 0

P5 and P7 can be removed since sur is covered by all states are, its code will be all o's and since the output is o.

This results in the given reduced table composed of ru, 12 and P8.

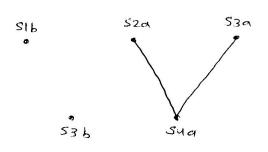

# (11) Seed Dichotomies

$51a: (51,52), (53) \times$   $51b: (53), (51,52) \times$   $52a: (51,52), (54) \times$   $52b: (54), (51,52) \times$   $53a: (52,53), (51) \times$   $53b: (51), (52,53) \times$   $54a: (52,53), (54) \times$

Seed dichotomy Compatibility Graph

Based on the compatibility graph, a minimum cover of 3 prime dichotomies is needed as follows:

Pli SIb: (53), (51,52)

P2: (S1, S2, S3), (S4)

P3: (52,53), (51,54)

Thus, a minimum of 3 bits are needed as follows:

f1 f2 f3

51 0 1 0

52 0 1 1

53 1 1 1

54 0 0 0

Note that for PI we have to assign sy to a b satisfy the covering constraints.

Note that all the encoding and covering constraints are satisfied by the derived encoding,

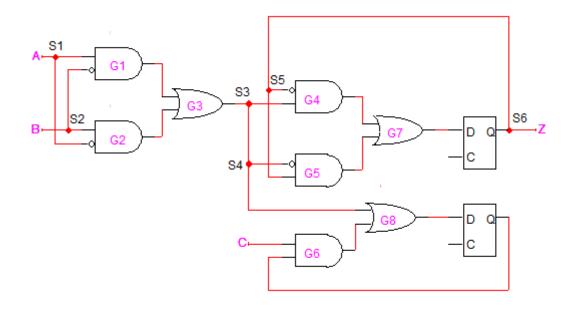

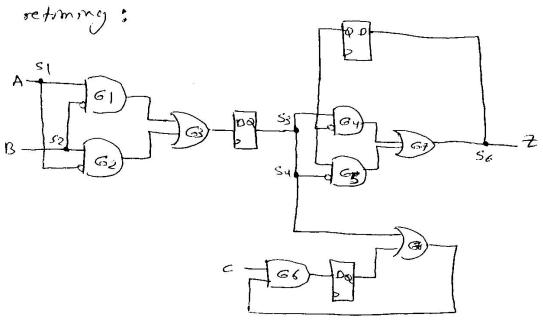

(Q4) Consider the sequential circuit given below having 3 inputs {A, B, C} and one output {Z}. Assume that the delay of all given gates is 2 unit delays.

- Determine the critical path of this circuit and the maximum propagation delay. **(i)**

- (ii) Using only the **Retiming** transformation, reduce the critical path of this circuit with the minimum number of flip-flops possible. Determine the maximum propagation delay after retiming.

- There are 8 critical paths from either gates (1) GI or G2, through G3, then through either gates G4 or G5, through G7.

- (11) We can apply the following retiminey transformations to reduce the critical path:

- retime 67 by +1

- retire G4 by +1

retire G5 by +1

retire S5 by +1

- retime 68 by +1

- retime 54 by +1

- retime 53 by +1

This results in the following circuit after

The maximum propagation delay in the resulting circuit is 4. The number of flip-flops has increased from 2 b 3:

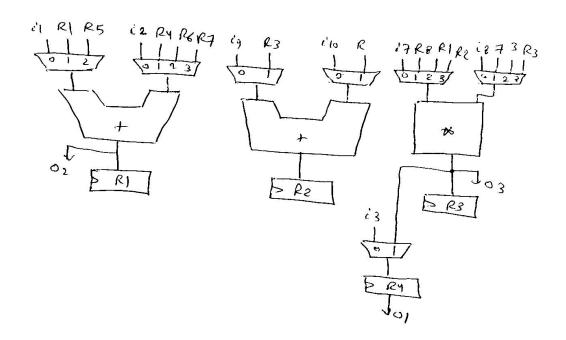

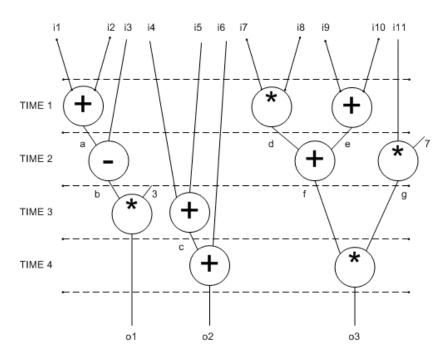

(Q5) Consider the network given below with inputs {i1, i2, i3, i4, i5, i6, i7, i8, i9, i10, i11} and outputs {o1, o2, o3}. Assume that the delay of both the Adder and the Multiplier fit within one clock cycle and that the input values will be available to the circuit for only one clock cycle. Also assume that both addition and subtraction operations will be performed by the Adder.

$$a = i1 + i2;$$

$b = a - i3;$   $c = i4 + i5;$   $d = i7 * i8;$   $e = i9 + i10;$   $f = d + e;$   $g = i11 * 7;$   $o1 = b * 3;$   $o2 = c + i6;$   $o3 = g * f;$

- (i) Using **List Scheduling** algorithm LIST\_L, schedule the sequencing graph into the **minimum number of cycles** under the <u>resource constraints of one Adder and one Multiplier</u>. Show the details of the algorithm step by step and the resulting scheduled sequencing graph.

- (ii) Using **List Scheduling** for minimum resource usage algorithm LIST\_R, schedule the sequencing graph under the latency constraint of **5 clock cycles** minimizing the number of resources required. Show the details of the algorithm step by step and the resulting scheduled sequencing graph.

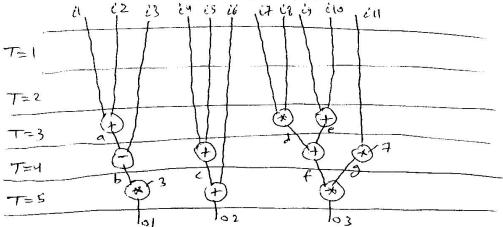

- (iii) Consider the scheduled sequencing graph below:

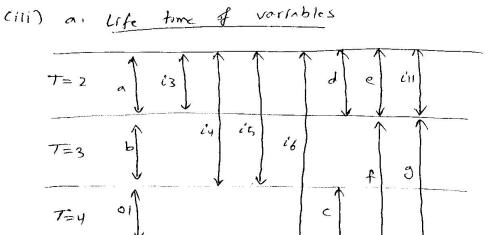

- a. Show the life-time of all variables.

- b. Determine the minimum number of registers that are required to store all the variables. Show the mapping of variables to registers. Select a mapping that **minimizes the number of multiplexers and interconnect area** as much as possible.

- c. Draw the **data-path** implementing the scheduled sequencing graph based on the variable-register mapping that you obtained in (b).

# (1) List-Li

#### l = 1 :

Ul, add = {a,c,e3. We need to schedule either a or e since they have longer path to sink. Letis schedule a.

Ul, mul = {d, 03. We schedule of since it has longer path to sink.

## l=2;

1/2, add = {b, c, e}, we schedule e since it has longer path to sink.

U2, mul = 203

#### l = 3;

Us, add = { b, c, f}, Any of them can be scheduled as they have the same path to smk. Let's schedule b. U3, mul = {}

#### Q=4:

U4, add = {c,f}, Any can be scheduled. Let's Schedule C. U4, mul = 2019

## l=5:

Us, add = { 02, f3, Schedule f since it has longer path to sink.

Us, mul = 23

## l=6:

UK, add = 2023 UG, mul = {035 Thus, the minimum required schedule is 6 clock cycles as follows:

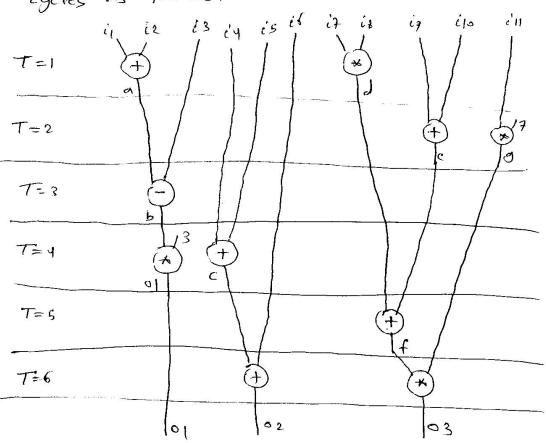

# (11) List-R:

$\lambda = 5$ , a = [1,1]. We need to compute the ALAP schedule with  $\lambda = 5$  as follows! it is is if it is in in

#### Q=1:

Ul, add = Ea, c, e 3. None of the sperations has o slack. We schedule one operation with the lowest slack. Schedule a

UI, mul = Edigg. None of the operations has o slack, we schedule one operation with the lowes slack, we schedule di

# l=25

U2, add = Eb, c, e3. None of the operations has o slack, we schedule e since it has lower slack U2, mul = 833

## $\ell=3$ :

Us, add = {b,c,f}. None of the operations has o slack. Any can be scheduled as they have the same slack. Let's schedule b.

V3, mul = 23

## Q=4%

U4, add = Ec, f 3. Both of Nem have a slack of o and need to be scheduled. Thus, a = [2,1]. U4, mul = 2013

U5, add = 2025 U5, mvl = 2035

This, with 5 clock cycles, we need a minimum

of 2 adders and 1 multiplier as shown below:

T=1

T=2

T=3

T=1

OI

C

T=5

OI

O2

O2

O3

b. Based on the lifetime of all variables, it is obvious that we need 8 registers to store all variables.

we will assign variables to registers as follows to minmite area:

RI: (a,b,c) R2: (e,f) R3: (d,g)

R4: (13,01) R5: 64 R6: 65

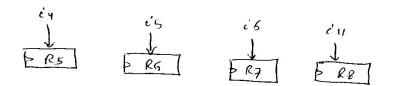

R7: 66 R8: 611

## C. Data Path: