### COMPUTER ENGINEERING DEPARTMENT

### **COE 561**

### **Digital System Design and Synthesis**

### **Final Exam**

(Open Book Exam)

First Semester (091)

Time: 7:00-10:00 PM

| Student Nam | e :KEY |  |  |

|-------------|--------|--|--|

|             |        |  |  |

| Student ID. | :      |  |  |

| Question | Max Points | Score |

|----------|------------|-------|

| Q1       | 20         |       |

| Q2       | 20         |       |

| Q3       | 23         |       |

| Q4       | 12         |       |

| Q5       | 25         |       |

| Total    | 100        |       |

### $(\ensuremath{\mathbf{Q1}})$ Consider a technology library containing the following cells:

| Cell                                                | Area Cost | Gate |

|-----------------------------------------------------|-----------|------|

| INV(x1) = x1'                                       | 1         | ->   |

| NAND2(x1, x2) = (x1 x2)'                            | 2         |      |

| NAND3(x1, x2, x3) = (x1 x2 x3)'                     | 3         |      |

| NOR2(x1, x2) = (x1 + x2)                            | 2         |      |

| NOR3(x1, x2, x3) = $(x1 + x2 + x3)$ '               | 3         |      |

| AOI21(x1, x2, x3) = $((x1 \ x2) + x3)$ '            | 3         |      |

| AOI22(x1, x2, x3, x4) = $((x1 \ x2) + (x3 \ x4))$ ' | 4         |      |

| OAI21(x1, x2, x3) = $((x1+x2) x3)$ '                | 3         |      |

| OAI22(x1, x2, x3, x4) = $((x1+x2)(x3+x4))$ '        | 4         |      |

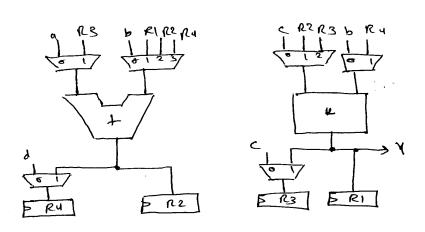

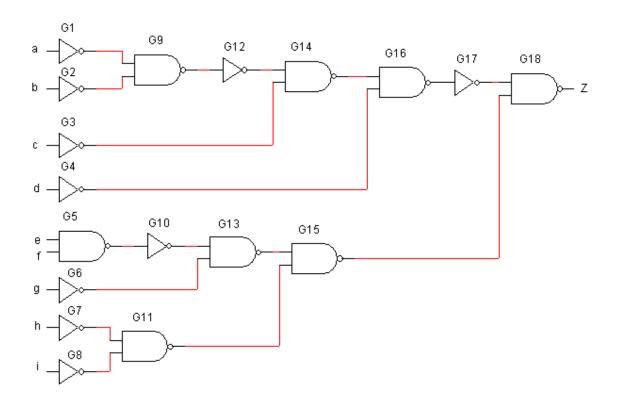

(i) Consider the circuit given below with inputs  $\{a, b, c, d, e, f, g, h, i\}$  and output  $\{Z\}$ . Using the dynamic programming approach and **Structural Matching**, map the circuit using the given library into the **minimum area** cost solution.

(ii) Assuming **Boolean Matching**, determine the <u>number</u> of ROBDD's that need to be stored in the cell library for the following cell. <u>Justify your answer</u>.

$$Y = a b c + d e + f g + f' g'$$

| (i) | vertex      | gale                                                          | cost                      |

|-----|-------------|---------------------------------------------------------------|---------------------------|

|     | GI          | 1NV(a)                                                        |                           |

|     | G2          | IM (P)                                                        | 1                         |

|     | Gž          | 127(6)                                                        | 1                         |

|     | <u> </u>    | (NV(d)                                                        | 1                         |

| _   |             | Nand 2 (e,f)                                                  | 2                         |

| -   | <u> </u>    | (NV(g)                                                        | 1                         |

|     | <u> </u>    | Inr(r)                                                        | 1                         |

|     | <u> </u>    |                                                               | 1                         |

|     | G2          | (NV(i)<br>Nand2 (01,62)                                       | 2+1+1=4                   |

|     | G9          |                                                               | 1+2=3                     |

|     | Glo         | INV (@5)                                                      | 2+1+1=4                   |

|     | GII         | Nand 2 (G7, G8)                                               |                           |

|     | <b>G12</b>  | INV (G9)<br>NOR2 (a,b)                                        | 1+4=5                     |

|     | G13         | Nand2 (@10, G6<br>Nand3 (e,f, @                               | ~ . 1 = 4                 |

|     | <b>G</b> 14 | Nand2 (812, 6<br>Nand3 (61, 68                                |                           |

| _   | G15         | Nand2(G13, G11)  OAT21(G5, 3, 1)  OAT21(G13, h)  OAT22(G5, 8) | G(1) $3+2+4=9(1)$ $3+4=7$ |

| vertex | gate                                    | cost                    |

|--------|-----------------------------------------|-------------------------|

| G16    | Nand2 (@14, G15)<br>OAI21 (G9, C, G4)   | 2 + 5+6 = 13 3 +4+1 = 8 |

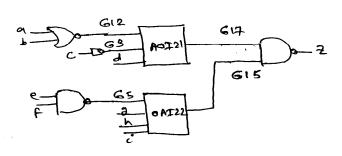

| GIA    | INV (G16)<br>AOIZI (G12,G3,d)           | 1+8=9 3+2+1=6           |

| G18    | Nandz (617, 615)<br>Nand3 (614, 63, 615 | 2+6+6=14                |

Thus, the minimum area cost solution is 14 as shown below:

(11)

C2 = { (d,e), (f,8)}

C3 = { (a,b,c)}

Number of ROBDD's required is I

since (d,e) are unake while (f,8)

are binate.

(Q2) Consider the incompletely-specified FSM that has 5 states, one input (X) and one output (Z), represented by the following state table:

| <b>Present State</b> | Next State, Z |       |  |

|----------------------|---------------|-------|--|

|                      | X=0           | X=1   |  |

| S0                   | S0, 0         | S1, 1 |  |

| S1                   | S0, 1         | S3, 0 |  |

| S2                   | S4, 0         | S3, 1 |  |

| S3                   | S2, 1         | S3, - |  |

| S4                   | S2, -         | S1, 1 |  |

- (i) Determine the incompatible states and the compatible states along with their implied pairs.

- (ii) Compute the maximal compatible classes along with their implied state pairs.

- (iii) Reduce the state table into the minimum number of states and show the reduced state table.

' · ·

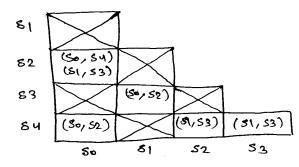

### (i) Compatibility Table:

(80, 54) (S0, 52)

The incompatible states are: (80, 51), (80, 53), (81, 52), (81, 54), (82, 53)The compatible states with their implied pairs:  $(80, 82) \neq (80, 84)$  and (81, 83)  $(81, 83) \neq (80, 82)$   $(82, 84) \neq (81, 83)$   $(83, 84) \neq (81, 83)$

# (11) Maximal Compadible Classes:

From the incompatible state pairs we have;

$$= (\overline{50} + \overline{51} \overline{53})(\overline{51} + \overline{5254})(\overline{52} + \overline{53})$$

$$= (\overline{S_0}\overline{S_1} + \overline{S_0}\overline{S_2}\overline{S_4} + \overline{S_1}\overline{S_3})(\overline{S_2}+\overline{S_3})$$

Thus, the maximal compatible classes with their implied pairs are:

$$(53, 54) \neq (51,53)$$

$(51, 53) \neq (50,52)$

$(50,52,54) \neq (51,53)$

(111) The following cover can be used which satisfies the closure property:

§ (50,52,54), (51,53)}

Thus, the state machine can be reduced to two states as follows:

| P.S. | Nisi, Z | <b>&gt;</b> |

|------|---------|-------------|

| 1,0, | X = 0   | ×=1         |

| S024 | 5024,0  | 513, 1      |

|      | 5024,1  | 513,0       |

| 813  |         |             |

(Q3) Consider the incompletely-specified FSM that has 5 states, two inputs and one output, represented by the following state table:

| Product | Input | Present State | Next State | Output |

|---------|-------|---------------|------------|--------|

| P1      | 00    | S0            | S0         | 0      |

| P2      | 01    | S0            | S0         | 0      |

| P3      | 10    | S0            | S3         | 0      |

| P4      | 11    | S0            | S3         | 0      |

| P5      | 00    | S1            | S0         | 0      |

| P6      | 01    | S1            | S4         | 0      |

| P7      | 10    | S1            | S1         | 0      |

| P8      | 11    | S1            | S1         | 0      |

| P9      | 00    | S2            | S3         | 0      |

| P10     | 01    | S2            | <b>S</b> 3 | 0      |

| P11     | 10    | S2            | S1         | 0      |

| P12     | 11    | S2            | S4         | 0      |

| P13     | 00    | S3            | S3         | 0      |

| P14     | 01    | S3            | <b>S</b> 3 | 0      |

| P15     | 10    | S3            | S3         | 0      |

| P16     | 11    | S3            | S2         | 1      |

| P17     | 00    | S4            | S4         | 0      |

| P18     | 01    | S4            | S0         | 0      |

| P19     | 10    | S4            | S4         | 0      |

| P20     | 11    | S4            | S1         | 0      |

(i) Assuming the following constraints, S4 covers S0, S4 covers S1 and that the code of S3 is covered by all other state codes, the state table can be reduced into the table given below. Using implicant merging and covering relations show step by step how you can obtain the reduced state stable given below.

| Input | Present State | Next State | Output |

|-------|---------------|------------|--------|

| 0–    | S0, S1, S4    | S0         | 0      |

| 1–    | S1, S2, S4    | S1         | 0      |

| -0    | S4            | S4         | 0      |

| 01    | S1            | S4         | 0      |

| 11    | S2            | S4         | 0      |

| 11    | S3            | S2         | 1      |

(ii) Compute all the prime dichotomies. Find a state encoding satisfying the given constraints with minimal bit length.

Since in PIT, oo sy sy o, and sy covers so, we can add sy to 11 resulting in;

since in P6, of SI 84 0, and S4 covers 80, we can add SI to T2 resulting in: T4 01 S0, S1, S4 S0 0

Next, 13 and My can be merged into the follow.

TS 0- 80, 51, 54 50 0

Pg and PII can be merged into the following row:

re 10 81,52 81 0

P8 and P20 can be merged who the following row:

77 11 81,54 81 0

Since in p19, 10 su su o, and su covers si, we can add su to resulting in:

78 10 81, 82, 84 81 0

81,000 m p12, 11 82 su 0, and 84 covers

81,000 m p12, 11 82 su 0, and 84 covers

81,000 m p12, 11 82 su 0, and 84 covers

81,000 m p12, 11 82 su 0, and 84 covers

81,000 m p12, 11 82 su 0, and 84 covers

81,000 m p12, 11 82 su 0, and 84 covers

81,000 m p12, 11 82 su 0, and 84 covers

Next, T8 and T9 can be merged into the following row:

rio 1- 81,52,54 81 0

PIZ and PIZ can be merged who the following row:

following row:

YII -0 Sy Sy 0

The rows P3, P4, P9, P10, P13, P14 and P15 can all be removed since 53 is covered by all other states and will be assigned the all other code.

This results in the given reduced table.

(11)

### Seed Dichotomies

81a: (50,51,54), (52)

82a: (50,51,54), (53)

81b: (52), (50,51,54)

82b: (53), (50,51,54)

83a: (51,52,54), (50)

84a: (51,52,54), (53)

83b: (50), (81,52,54)

84b: (53), (51,52,54)

Prime dichotomies are:

Pl: (50, S1, S4), (52, S3)

P2: (50, S1, 52, S4), (53)

P3 = (81, 82, 84), (80, 53)

The prime dichotomies Pl and \$3 cover all the seed dichotomies and are selected.

Thus, we obtain the following encoding:

| State     | code  |  |  |

|-----------|-------|--|--|

| <b>%~</b> | 100   |  |  |

| sı        | 1 10  |  |  |

| 52        | 0 1 0 |  |  |

| \$3       | 9 0 6 |  |  |

| S 4       | , , , |  |  |

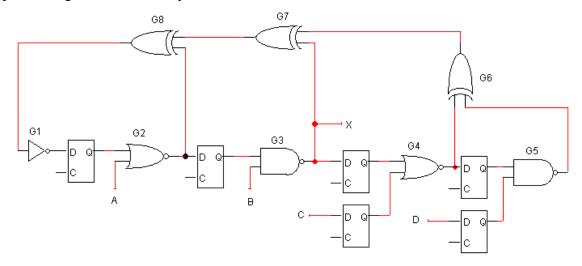

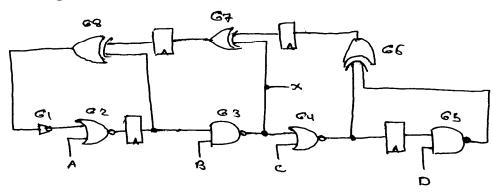

(Q4) Consider the sequential circuit given below having 4 inputs {A, B, C, D} and one output {X}. Assume that the delay of an inverter is 1 unit delay, the delay of a 2-input NAND gate is 2 unit delays, the delay of a 2-input NOR gate is 2 unit delays and the delay of a 2-input XOR gate is 3 unit delays.

- (i) Determine the critical path of this circuit and the maximum propagation delay.

- (ii) Using only the **Retiming** transformation, reduce the critical path of this circuit with the minimum number of flip-flops possible. Determine the maximum propagation delay after retiming.

- (i) The maximum propagation delay is 12 and there are two critical paths as follows; {65, 66, 67, 68, 613, {64, 66, 67, 68, 613}

- (11) We can apply the following retiming transformations to reduce the critical paths

retime 65 by -1

retime 64 by -1

retime 66 by -1

retime 66 by -1

retime 66 by +1

retime 68 by +1

retime 68 by +1

retime 68 by +1

This results in the following encust after retining?

The maximum propagation delay in the resulting circuit is 7 across the path 263, 64, 653.

The number of regristers has also been reduced from 6 to 4 regristers.

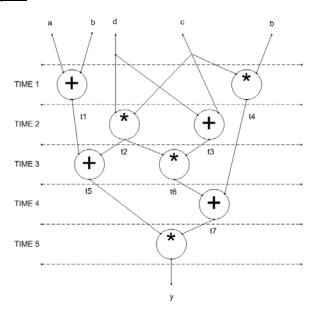

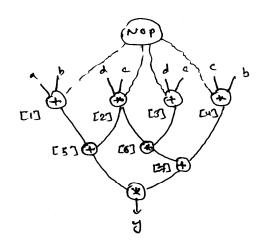

(Q5) Consider the network given below with inputs  $\{a, b, c, d\}$  and output  $\{y\}$ :

- (i) Draw the **sequencing graph** for the above network.

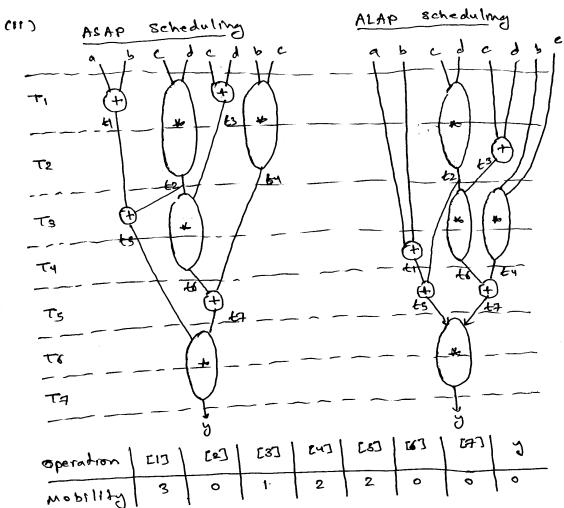

- (ii) Assuming that the delay of an <u>Adder fits within one clock cycle</u> and the delay of a <u>Multiplier fits within two clock cycles</u>, show the **ASAP** and **ALAP** scheduling of the sequencing graph. Compute the **mobility** of each operation.

- (iii) Using **List Scheduling** algorithm LIST\_L, schedule the sequencing graph into the **minimum number of cycles** under the <u>resource constraints of one Adder and one multiplier</u>. Assume that the delay of an <u>Adder fits within one clock cycle</u> and the delay of a <u>Multiplier fits within two clock cycles</u>. Show the details of the algorithm step by step and the resulting scheduled sequencing graph.

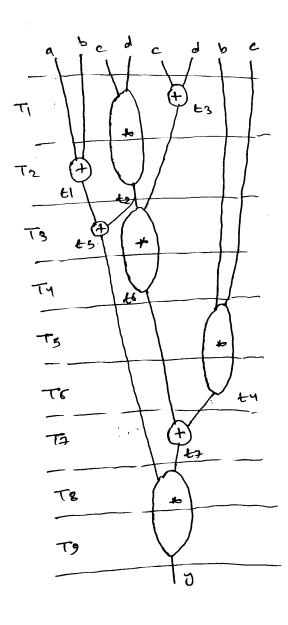

- (iv) Consider the scheduled sequencing graph below assuming that the delay of an Adder fits within one clock cycle and the delay of a Multiplier fits within one clock cycle. Assume that the input values will be available to the circuit for only one clock cycle.

- a. Show the life-time of all variables.

- b. Determine the minimum number of registers that are required to store all the variables. Show the mapping of variables to registers. Select a mapping that **minimizes the number of multiplexers and interconnect area** as much as possible.

- c. Draw the **data-path** implementing the scheduled sequencing graph based on the variable-register mapping that you obtained in (b).

### (1) Sequencing Graph:

#### LBJ Scheduling (111)

1=1

UI, add = { E13, E3] } we schedule [3] smee it has lower slack Ul, mul = { [2], [4]} we schedule [2] smee it has lower slack

1 = 2

U2, add = { [1]} we schedule [1]. U2, mul = [4] Since T2, mul = {[2]} [4] is not scheduled.

L=3

N3, 28 = 8[5] 3 we schedule [5]. U3, mul = { [4], [6]} we schedule [6] since 18 has lower stack

2=4

V4, add = 23 Uu, mv1 = 1 [4]3 smee Tu, mu1 = [ [6] } [4] Is not scheduled.

L=5

U5, add = & 3 U5, mul = { [4] } [4] is scheduled.

U9, add = 23

Thus, with one adder and one multiplier the mammum schedule is 9 clock cycles.

(iv) as life time of variables:

|     |    |    | c | d |    |

|-----|----|----|---|---|----|

| T=2 | 61 | _  |   |   |    |

| T=3 |    | 4  | 也 |   | ty |

| T=4 | 45 | FR |   |   |    |

| T=5 |    | 47 |   |   |    |

b. Based on the Irfetime of all variables of it is obvious that 4 registers are needed to store all the variables.

| Adder        | Mult.        |

|--------------|--------------|

| a +b =t1     | c + 6 = t4   |

| d + c = t3   | c * d = t2   |

| t1+t2=t5     | t2 + t3 = t6 |

| tu + t6 = t7 | ts: 4 67 = 0 |

To minimize the number of mux inputs and wiring, we make the following assignment of variables to registers:

RI: {tu} R2; {tl, ts} R8; {c, t2, t6} R4; {d, t3, t9}

ì

## c. Data Path