# COE 405 Dataflow Descriptions in VHDL

Dr. Aiman H. El-Maleh Computer Engineering Department King Fahd University of Petroleum & Minerals

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

| <b>Example: A 2x4 Decoder</b><br><b>Signal</b> D : <b>Bit_Vector</b> (1 <b>To</b> 4) := "0000";                          |     |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| Signal S0, S1 : Bit;                                                                                                     |     |

| <i>Decoder</i> : <b>D</b> <= "0001" after T When S1='0' and S0='0' <b>else</b><br>"0010" after T When S1='0' <b>else</b> |     |

| "0100" after T When S0="0" else "1000";                                                                                  |     |

| Example: 4-Phase Clock Generator<br>Signal Phi4 : Bit_Vector(1 To 4) := "0000";                                          |     |

| ClkGen: With Phi4 Select                                                                                                 |     |

| Phi4 <= "1000" after T When "0000",<br>"0100" after T When "1000",                                                       |     |

| "0010" after T When "0100",                                                                                              |     |

| "0001" after T When "0010",                                                                                              |     |

| "1000" after T When "0001",                                                                                              | 9   |

|                                                                                                                          | 1 9 |

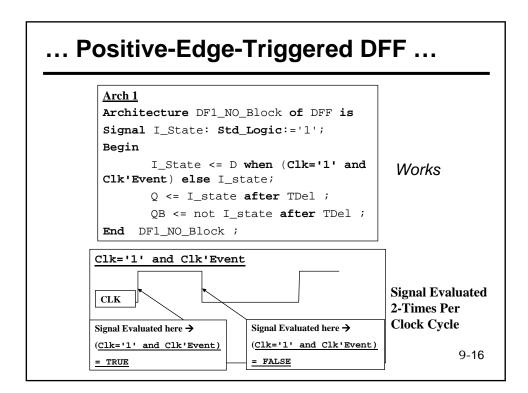

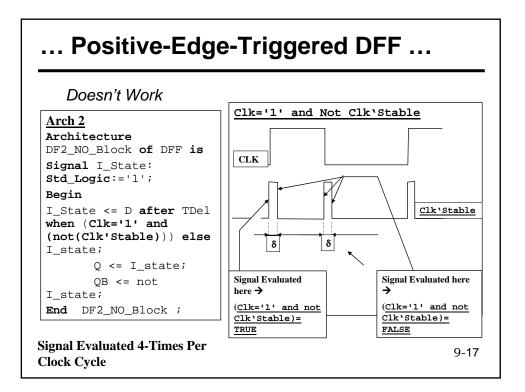

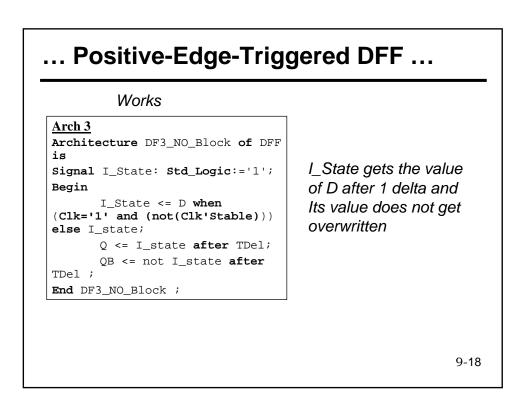

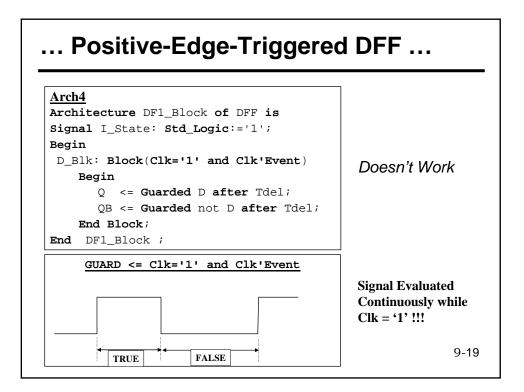

# Positive-Edge-Triggered DFF ...

```

Library IEEE;

Use IEEE.Std_Logic_1164.ALL;

Entity DFF is

Generic(TDel: Time:= 5 NS);

Port(D, Clk: in Std_Logic; Q, QB: out Std_Logic);

End DFF;

```

- We will show several dataflow architectures with and without Block statement

Will show why some of these architectures do not

- work

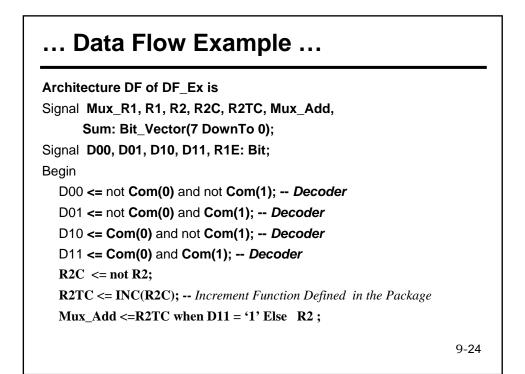

# Data Flow Example ...

**Model** A System with 2 8-Bit Registers R1 and R2, a 2-Bit Command signal "**COM**" and an external 8-Bit Input "**INP**"

•When Com= "00" → R1 is Loaded with External Input

•When Com= "01" → R2 is Loaded with External Input

•When Com= "10" → R1 is Loaded with R1+R2

•When Com= "11" → R1 is Loaded with R1-R2

Use Work.Utils\_Pkg.ALL Entity DF\_Ex is Port (Clk: IN Bit; Com: IN Bit\_Vector (1 DownTo 0); INP: IN Bit\_Vector(7 DownTo 0) R1, R2: BUFFER Bit\_Vector(7 DownTo 0)); End DF\_Ex;

# ... Data Flow Example

```

Sum <= ADD(R1, Mux_Add); -- ADD Function-- Defined in Package

Mux_R1 <= INP when D00 = '1' Else Sum;

R1E <= D00 OR D10 OR D11;

Rising_Edge: BLOCK(Clk='1' and not Clk'Stable) Begin

R1_Reg: BLOCK(R1E='1' AND GUARD) Begin

R1 <= Guarded Mux_R1 ;

End Block R1_Reg ;

R2_Reg: BLOCK(D01='1' AND GUARD) Begin

R2 <= Guarded INP ;

End Block R2_Reg ;

End Block Rising_Edge;

End DF;

9-25

```

# **"ORING"** Signal Resolution Function

FUNCTION oring ( drivers : qit\_vector) RETURN qit IS VARIABLE accumulate : qit := '0'; BEGIN FOR i IN drivers'RANGE LOOP accumulate := accumulate OR drivers(i); END LOOP; RETURN accumulate; END oring;

SUBTYPE ored\_qit IS oring qit;

-- The following declarations are equivalent SIGNAL t : ored\_qit; SIGNAL t : oring qit;

**Multiplexer uses implicit ORing** ARCHITECTURE multiple\_assignments OF mux\_8\_to\_1 IS SIGNAL t : ored\_qit; BEGIN t <= i7 AND s7; t <= i6 AND s6; t <= i5 AND s5; t <= i4 AND s4; t <= i3 AND s3;  $t \le i2 \text{ AND s2};$  $t \le i1 \text{ AND } s1;$  $t \le i0 \text{ AND } s0;$ z <= t; END multiple\_assignments; Multiplexer uses implicit ORing on t •AND\_OR logic is realized 9-32

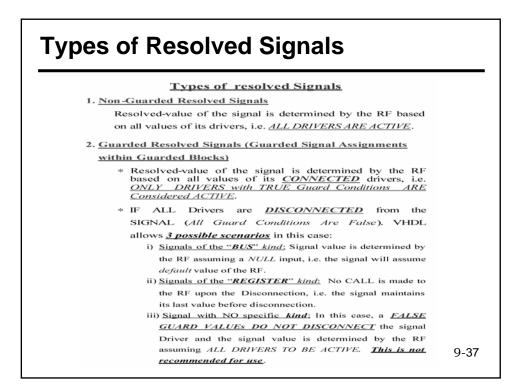

| Syntax                                                                                                     |      |

|------------------------------------------------------------------------------------------------------------|------|

| <u>Signal</u> <sig_name> : <resolved sig_subtype=""> [Signal_kind] [:=Initial_Value]</resolved></sig_name> | /;   |

| <u>Signal kind</u> ::= BUS   Register                                                                      |      |

| Examples:                                                                                                  |      |

| Signal x : Wired_MVL4 <i>BUS</i> ;                                                                         |      |

| Signal y : Wired_MVL4 <u><i>Register</i></u> ;                                                             |      |

| <u>Note</u> :                                                                                              |      |

| 1. Only Signals of Kind BUS May be Specified for                                                           |      |

| as Port Signals                                                                                            |      |

| 2. Signals of Register Kind May NOT be Specified                                                           |      |

| as Port Signals)                                                                                           |      |

| Entity ex is                                                                                               |      |

| Port(s1, s2 : in MVL4; Z: out wired_MVL4 BUS);                                                             |      |

| End ex;                                                                                                    | 9-38 |

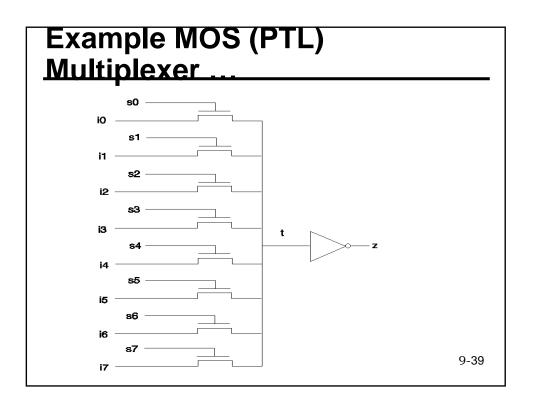

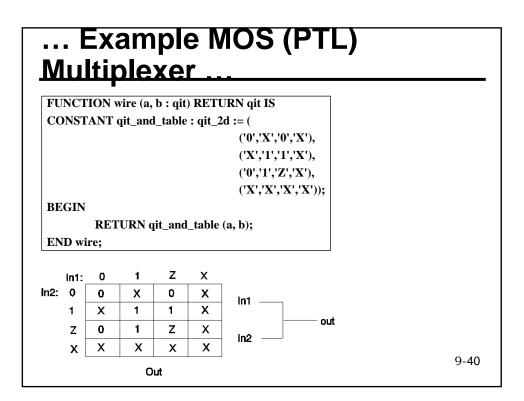

| Example MOS (PTL)                                             |      |

|---------------------------------------------------------------|------|

| Multiplexer                                                   |      |

| FUNCTION wiring ( drivers : qit_vector) Return qit IS         |      |

| Variable accumulate : qit := 'Z'; Default                     |      |

| BEGIN                                                         |      |

| FOR i IN drivers'RANGE LOOP                                   |      |

| accumulate := wire (accumulate, drivers(i));                  |      |

| END LOOP;                                                     |      |

| RETURN accumulate;                                            |      |

| END wiring;                                                   |      |

| SUBTYPE wired_qit IS wiring qit;                              |      |

| TYPE wired_qit_vector IS Array (Natural Range <>) OF wired_qi | it;  |

|                                                               |      |

|                                                               | 9-41 |

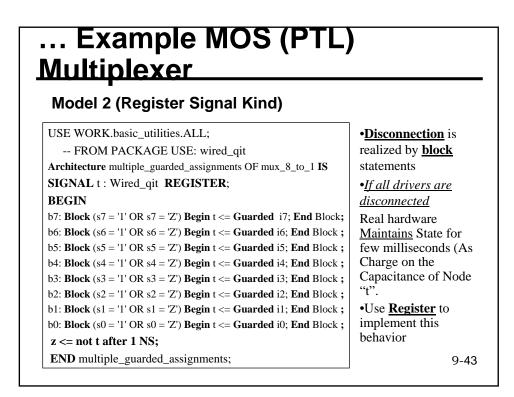

| Example MOS (PTL)<br>Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                       |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Model 1 (BUS Signal Kind)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                       |  |  |

| USE WORK.basic_utilities.ALL;<br>FROM PACKAGE USE: wired_qit<br>Architecture multiple_guarded_assignments OF mux_8_to_1 IS<br>SIGNAL t : Wired_qit BUS;<br>BEGIN<br>b7: Block (s7 = '1' OR s7 = 'Z') Begin t <= Guarded i7; End Block;<br>b6: Block (s6 = '1' OR s6 = 'Z') Begin t <= Guarded i6; End Block ;<br>b5: Block (s5 = '1' OR s5 = 'Z') Begin t <= Guarded i5; End Block ;<br>b4: Block (s4 = '1' OR s4 = 'Z') Begin t <= Guarded i4; End Block ;<br>b3: Block (s3 = '1' OR s3 = 'Z') Begin t <= Guarded i3; End Block ;<br>b2: Block (s2 = '1' OR s3 = 'Z') Begin t <= Guarded i2; End Block ;<br>b1: Block (s1 = '1' OR s1 = 'Z') Begin t <= Guarded i1; End Block ;<br>b0: Block (s0 = '1' OR s0 = 'Z') Begin t <= Guarded i0; End Block ; | •Disconnection is<br>realized by block<br>statements<br>• <u>If all drivers are</u><br><u>disconnected</u><br>Hardware returns to<br>'Z' → Modeling This<br>Requires Using <u>BUS</u><br>Signal Kind. |  |  |

| <pre>z &lt;= not t after 1 NS;<br/>END multiple_guarded_assignments;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9-42                                                                                                                                                                                                  |  |  |

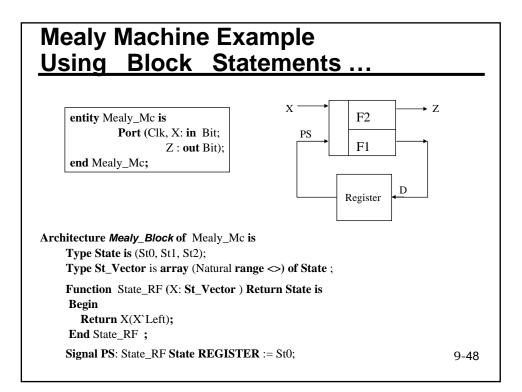

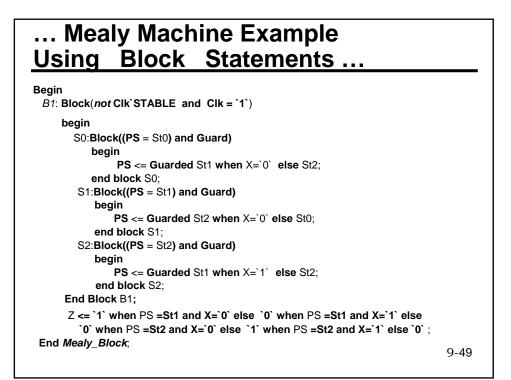

### ... Mealy Machine Example **Using Block Statements** Since there are 3 concurrent signal assignments to the signal PS , it is declared as a Resolved Signal with the RF being State\_RF. Signal PS is also declared to be of REGISTER kind. This Means that the signal is Guarded and Resolved and that the RF is not invoked in case all its Drivers are Turned Off (e.g. when CLK = '0') in which case the signal retains its Previous Value. The outer Block statement ``B1`` defines an IMPLICIT Guard signal Which is TRUE only on the Rising Edge of the Clock. The Implicit Guard Signal ANDed with the Present State define the Guard Condition for the Nested Block Statements. **ONE Inner Block Statement is assigned to each possible Present** State. The State Machine Model used allows only One Driver of the Resolved Signal PS to be Active at any Given Time. Thus the `Left Attribute is used in the RF to derive the signal value forced by this driver. 9-50

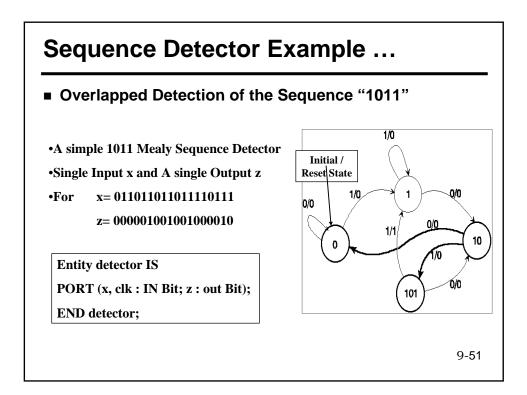

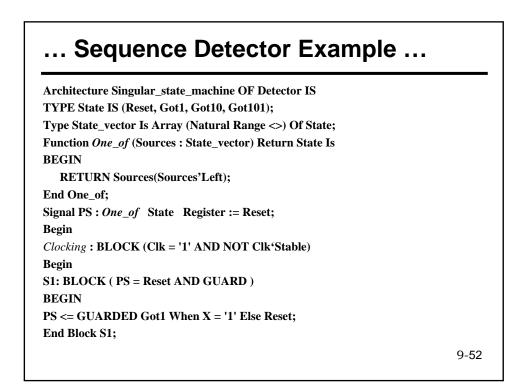

# ... Sequence Detector Example ...

S2: Block ( PS = Got1 And Guard ) Begin PS <= GUARDED Got10 When X = '0' Else Got1; End Block S2; S3: Block ( PS = Got10 And Guard ) Begin PS <= Guarded Got101 When X = '1' Else Reset; End Block S3; S4: Block ( PS = Got101 And Guard) Begin PS <= Guarded Got1 When X = '1' Else Got10; End Block S4; End Block Clocking;

PS receives four concurrent assignments

PS must be <u>res</u>olved; use

one\_of as an RF

9-53

Z <= '1' When ( PS = Got101 And X = '1') Else '0';

End Singular\_state\_machine;

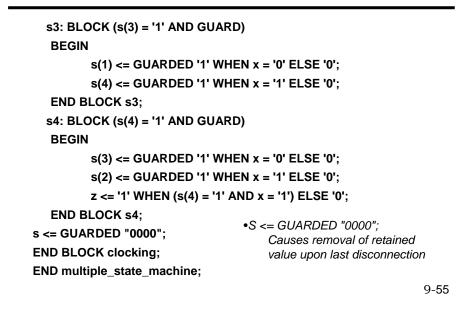

### ... Sequence Detector Example ... --States are: 1 = reset, 2 = got1, 3 = got10, 4 = got101 --use a signal for each state ARCHITECTURE multiple\_state\_machine OF detector IS SIGNAL s : ored\_bit\_vector (1 TO 4) REGISTER := "1000"; BEGIN clocking : BLOCK (clk = '1' AND NOT clk'STABLE) BEGIN s1: BLOCK (s(1) = '1' AND GUARD) BEGIN s(1) <= GUARDED '1' WHEN x = '0' ELSE '0'; s(2) <= GUARDED '1' WHEN x = '1' ELSE '0'; END BLOCK s1; s2: BLOCK (s(2) = '1' AND GUARD) BEGIN s(3) <= GUARDED '1' WHEN x = '0' ELSE '0'; s(2) <= GUARDED '1' WHEN x = '1' ELSE '0'; 9-54 END BLOCK s2;

# ... Sequence Detector Example

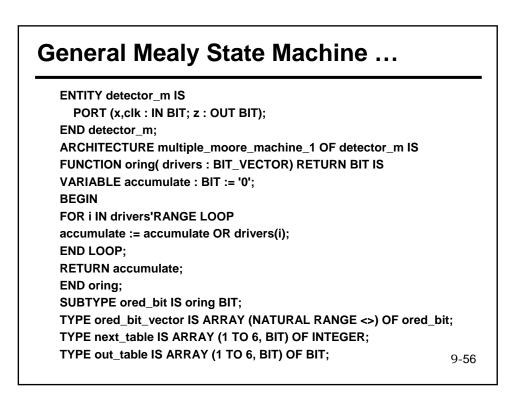

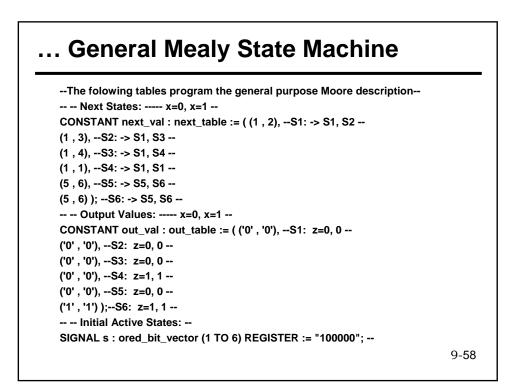

# ... General Mealy State Machine ...

```

-- Fill in next_val, out_val, and s arrays

SIGNAL o : ored_bit REGISTER;

BEGIN

clocking : BLOCK (clk = '1' AND (NOT clk'STABLE))

BEGIN

g: FOR i IN s'RANGE GENERATE

si: BLOCK (s(i) = '1' AND GUARD)

BEGIN

s(next_val(i,'0')) <= GUARDED '1' WHEN x='0' ELSE '0';

s(next_val(i,'1')) <= GUARDED '1' WHEN x='1' ELSE '0';

o <= GUARDED out_val(i, x);</pre>

END BLOCK si;

s (i) <= GUARDED '0';

END GENERATE;

END BLOCK clocking;

z <= 0;

END multiple_moore_machine_1;

```

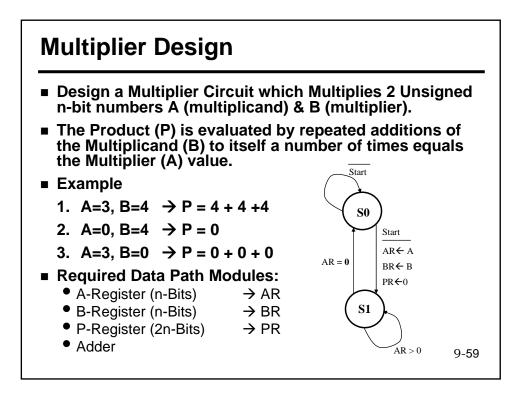

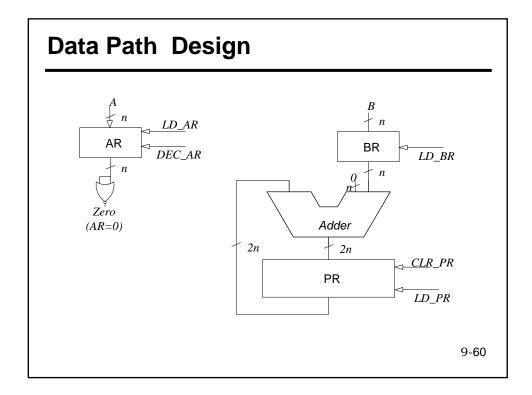

# Controller Model ...

Entity **CPath\_Mult** is Port (clk, start, zero: IN Bit ; LD\_AR, LD\_BR, CLR\_PR, LD\_PR, Dec\_AR: OUT BIT); End **CPath\_Mult** ; Architecture DF of **CPath\_Mult** is Type States is (Initial, Iterative); Type State\_Vector is Array (Natural Range <>) of States; Function RF(V:State\_Vector) Return States is Begin Return V(V'Left); end RF; Signal PS: RF States **Register** := Initial; **Begin**  *edge*: **Block**(*Clk*='1' and not Clk'Stable) **Begin**

| S0: Block(PS= Initial and Guard)                          |      |

|-----------------------------------------------------------|------|

| Begin                                                     |      |

| PS <= Guarded Iterative when Start='1' Else Initial;      |      |

| end Block S0;                                             |      |

| S1: Block(PS= Iterative and Guard)                        |      |

| Begin                                                     |      |

| PS <= Guarded Iterative when Zero /='1' Else Initial;     |      |

| end Block S1;                                             |      |

| $LD_AR \ll 1'$ when $PS=$ Initial and Start='1' else '0'; |      |

| LD_BR <= '1' when PS= Initial and Start='1' else '0';     |      |

| $Clr_PR \ll 1'$ when PS= Initial and Start='1' else '0';  |      |

| LD_PR <= '1' when PS=Iterative and Zero /= '1' else '0';  |      |

| DEC_AR <= '1' when PS=Iterative and Zero /= '1' else '0'; |      |

| End Block edge;                                           |      |

| End DF;                                                   | 9-62 |

# Data Path Model ...

### Entity DPath\_Mult is

Generic(N: Positive:= 8);

Port(LD\_AR, LD\_BR, CLR\_PR, LD\_PR, Dec\_AR, Clk: in Bit; A, B: in Bit\_Vector(N-1 DownTo

0); Zero: out Bit :='0'; P: out Bit\_Vector(2\*N-1 DownTo 0));

9-63

### End DPath\_Mult;

```

Architecture DF of DPath_Mult isSignal AR, BR: Bit_Vector(N-1 DownTo 0);Signal PR: Bit_Vector(2*N-1 DownTo 0);Signal ARE,BRE,PRE : Boolean:=False ;BeginARE <= LD_AR='1' or DEC_AR='1';</td>BRE <= LD_BR='1';</td>-- Inner Block (Register) Enable SignalsPRE <= LD_PR='1' or CLR_PR='1';</td>edge: Block(Clk='1' and not Clk'Stable)Begin

```

| Data Path Model                                                                                       |       |

|-------------------------------------------------------------------------------------------------------|-------|

| AReg: Block(ARE and Guard)<br>Begin                                                                   |       |

| $AR \le Guarded A$ when $LD_AR='1'$ else $AR+(N-1 Downto 0=>'1')$ when $Zero /= '1'$ else Unaffected; | e     |

| Zero <= '1' when (Bin2Int(AR)=0) else '0';                                                            |       |

| end Block AReg;                                                                                       |       |

| BReg: Block(BRE and Guard)                                                                            |       |

| Begin                                                                                                 |       |

| BR <= Guarded B;                                                                                      |       |

| end Block BReg;                                                                                       |       |

| PReg: Block(PRE and Guard)                                                                            |       |

| Begin                                                                                                 |       |

| $PR \le Guarded PR + (N-1 Downto 0 => '0')$ &BR when LD_PR='1' else (2*N-1 Downto 0 => '0')           | '0'); |

| end Block PReg;                                                                                       |       |

| End Block edge;                                                                                       |       |

| $P \leq PR$ ;                                                                                         |       |

| End DF;                                                                                               | 9-64  |

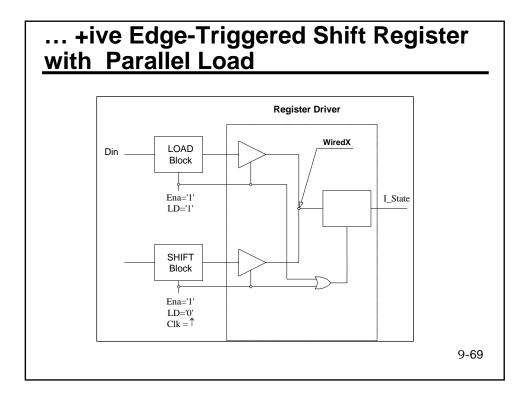

### +ive Edge-Triggered Shift Register with Parallel Load ...

**Register INPUTS In Order of Priority**

- Ena : If Ena=0, The register Cannot Change its state.

- LD : IF LD = 1, Data on the parallel inputs (Din) are Loaded into the Register independent of the Clock Signal (Asynchronous Load)

- Dir : Determines the Direction of the Shift or Rotate Operation. Dir=0 indicates a Left shift/Rotate while Dir = 1, indicates a Right Shift /Rotate.

- Shift Mode Signals M1 & M2

- M1M2 : 00 A 0 is Shifted-In

- M1M2 : 01 A 1 is Shifted-In

- M1M2 : 10 The Sin input is Shifted-In

- M1M2 : 11 Rotate Operation.

9-65

### ... +ive Edge-Triggered Shift Register with Parallel Load ...

| •• =               | is Array(Natural range <>) of MVL4 ;<br>is array(MVL4 , MVL4) of MVL4; |      |

|--------------------|------------------------------------------------------------------------|------|

|                    | 'x', '0', '1', 'Z'                                                     |      |

|                    |                                                                        |      |

| Function WiredX    | (INP : MVL4_Vec) Return MVL4 is                                        |      |

| Variable Result: I | MVL4:='z'; Initialize                                                  |      |

| Begin              |                                                                        |      |

| For i in INP'Ra    | ange Loop                                                              |      |

| Result:= TA        | B_X(Result , INP(i));                                                  |      |

| End Loop;          |                                                                        |      |

| Return Result      | t;                                                                     |      |

| end WiredX ;       |                                                                        |      |

| SubType WX is      | WiredX MVL4 ;                                                          | 9-66 |

| Type WX_Vector     | is Array(Natural range <>) of WX ;                                     |      |

# ... +ive Edge-Triggered Shift Register with Parallel Load ...

Entity ShiftReg is Port (Ena, Ld, Clk, Dir, M1, M2 : in Bit; Sin : in MVL4 ; Din : in WX\_Vector(7 downto 0); Q : Out WX\_Vector(7 downto 0)); END ShiftReg ; Architecture DF of ShiftReg is Signal I\_State : WX\_Vector(7 downto 0) Register; signal t: bit\_vector(2 downto 0); Begin t <= Dir & M1 & M2 ; Load: Block(Ena='1' and Ld='1') begin I\_State <= Guarded Din;

end block Load:

9-67

### ... +ive Edge-Triggered Shift Register with Parallel Load ... Shift: Block(Ena='1' and Ld='0' and Clk='1' and not Clk`Stable) begin With t Select I\_State <= Guarded I\_State(6 downto 0) & '0' When "000", I\_State(6 downto 0) & '1' When "001", I State(6 downto 0) & Sin When "010", I\_State(6 downto 0) & I\_State(7) When "011", '0' & I\_State(7 downto 1) When "100", '1' & I\_State(7 downto 1) When "101", Sin & I\_State(7 downto 1) When "110", I\_State(0)& I\_State(7 downto 1) When "111"; end block Shift; Q <= I\_State After 5 ns; End DF; 9-68