# COE 405 Behavioral Descriptions in VHDL

Dr. Aiman H. El-Maleh Computer Engineering Department King Fahd University of Petroleum & Minerals

### **Outline**

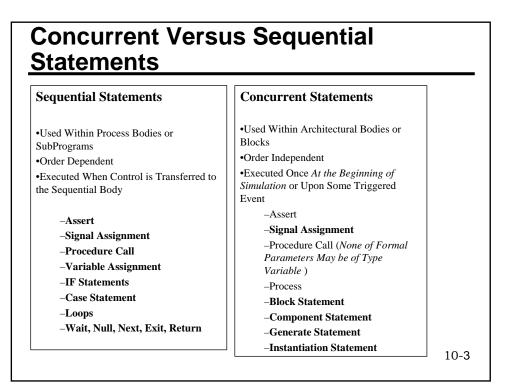

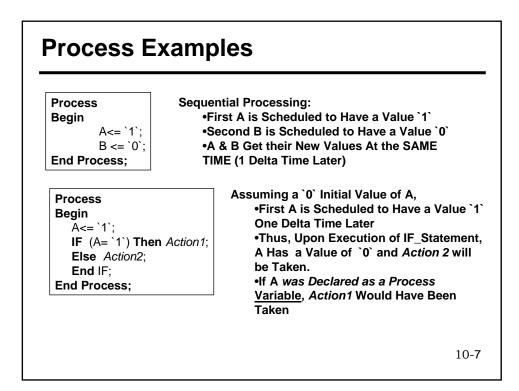

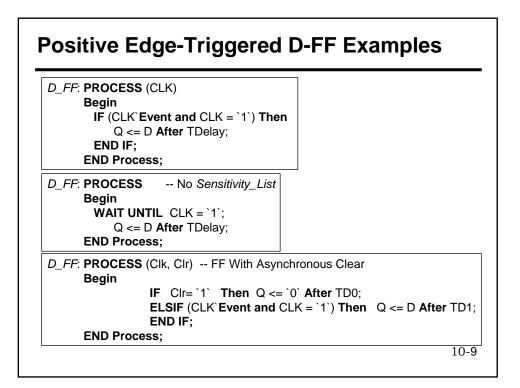

- Constructs for Sequential Descriptions

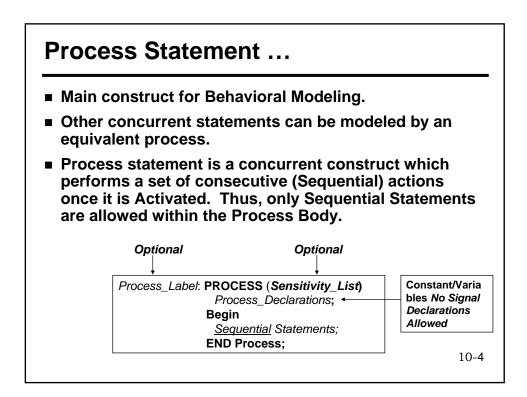

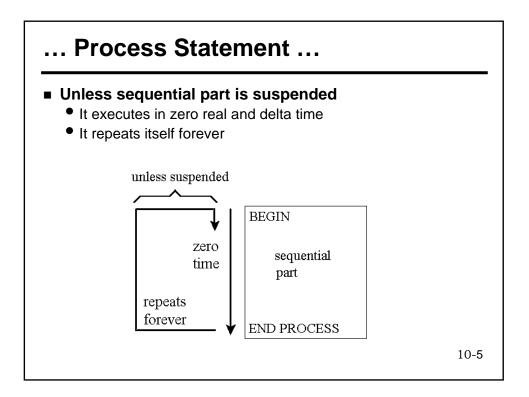

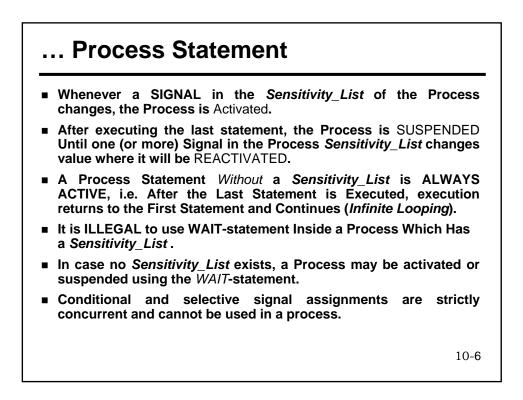

- Process Statement

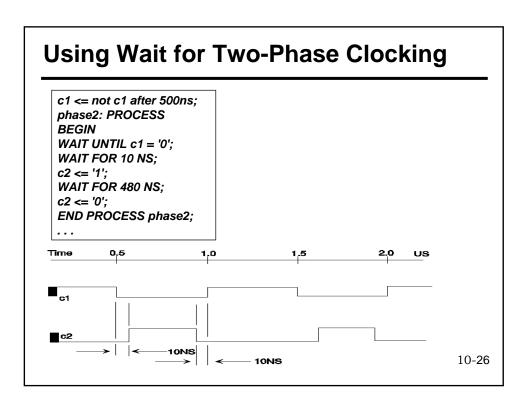

- Wait Statement

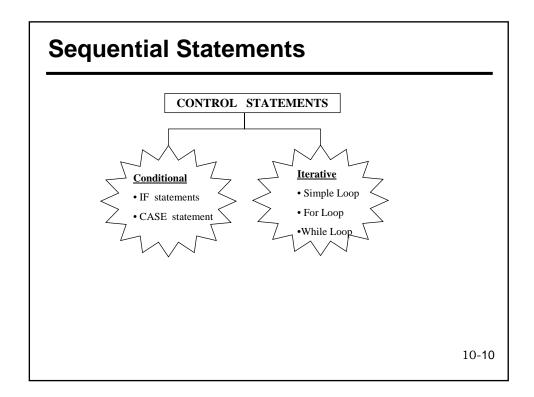

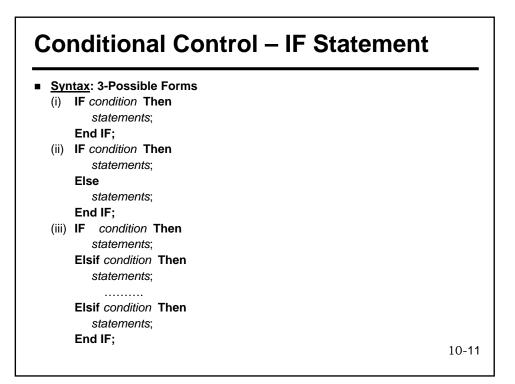

- Control Statements: Conditional & Iterative

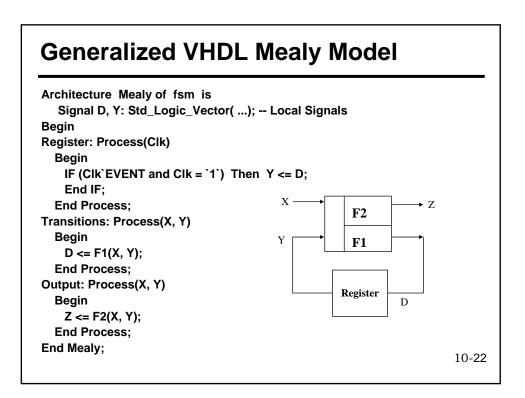

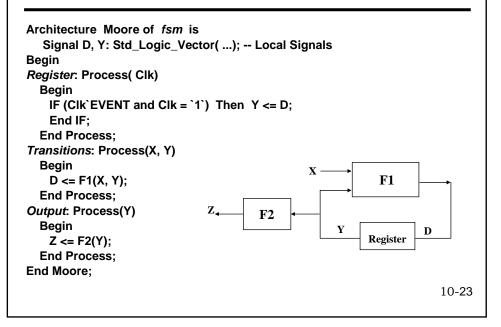

- Behavioral Modeling of Mealy & Moore FSMs

- Assertion for Behavioral Checks

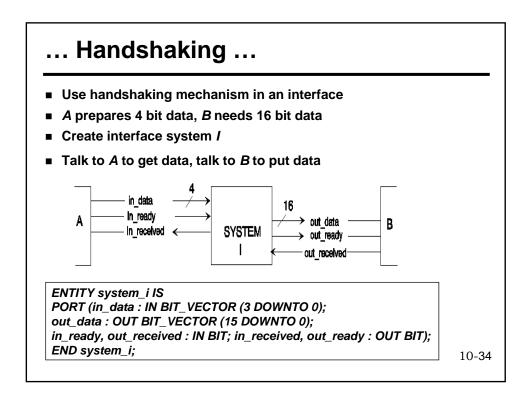

- Handshaking

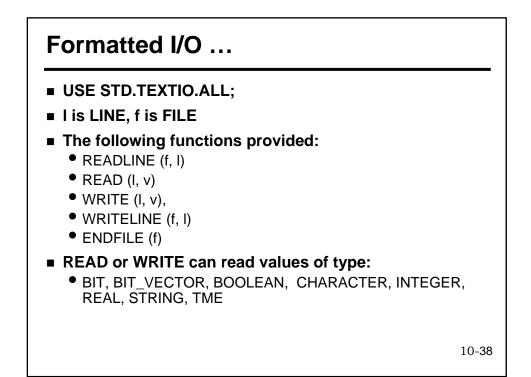

- Formatted I/O

| Wait Statement     Syntax of Wait Statement :                                                                                                                                               |                                                                                               |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                             |                                                                                               |  |

| <ul> <li>WAIT ON Signal_List;</li> </ul>                                                                                                                                                    | On event on a signal                                                                          |  |

| <ul> <li>WAIT UNTIL Condition;<br/>true;</li> </ul>                                                                                                                                         | until event makes condition                                                                   |  |

| • WAIT FOR Time_Out_Exp                                                                                                                                                                     | ression;                                                                                      |  |

| <ul> <li>WAIT FOR 0 any_time_uni</li> </ul>                                                                                                                                                 | it; Process Suspended for 1 delta                                                             |  |

| When a WAIT-statement is Execonditions for its Reactivation a                                                                                                                               |                                                                                               |  |

| <ul> <li>Process Reactivation condition</li> <li>WAIT ON Signal_List UNTIL Ca</li> <li>wait on X,Y until (Z = 0) +<br/>After 70 NS OR (in Case X<br/>True) Whichever Occurs File</li> </ul> | ondition FOR Time_Expression ;<br>for 70 NS; Process Resumes<br>or Y Changes Value and Z=0 is |  |

| <ul> <li>Process Reactivated IF:</li> <li>Event Occurred on the Signal_L</li> <li>Wait Period Exceeds ``Time_E</li> </ul>                                                                   | List while the Condition is True, OR $_{10-8}$                                                |  |

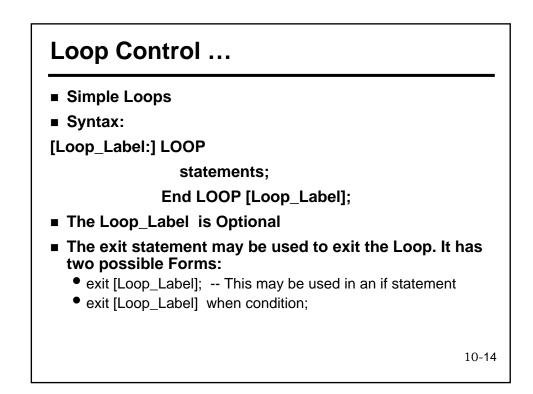

## ...Loop Control

```

Process

variable A : Integer :=0;

variable B : Integer :=1;

Begin

Loop1: LOOP

A := A + 1;

B := 20;

Loop2: LOOP

IF B < (A * A) Then

exit Loop2;

End IF;

B := B - A;

End LOOP Loop2;

exit Loop1 when A > 10;

End LOOP Loop1;

End Process;

```

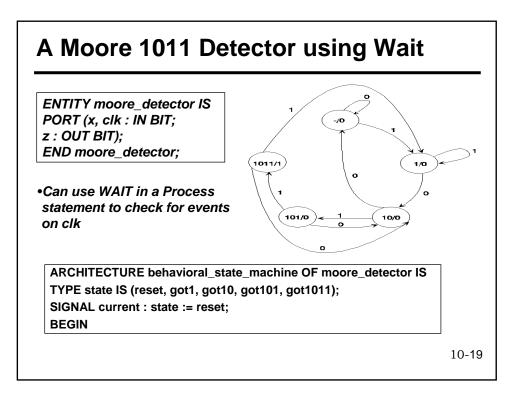

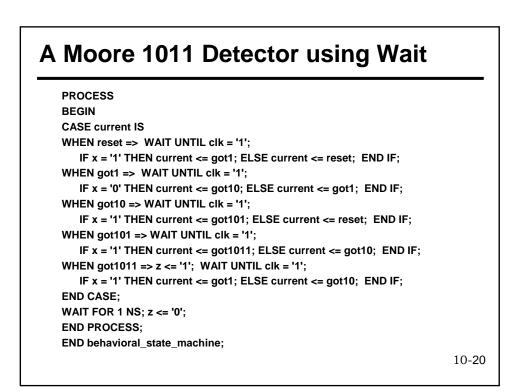

#### A Moore 1011 Detector without Wait

```

ARCHITECTURE most_behavioral_state_machine OF moore_detector IS

TYPE state IS (reset, got1, got10, got101, got1011);

SIGNAL current : state := reset;

BEGIN

PROCESS (clk)

BEGIN

IF (clk = '1' and CLK'Event) THEN

CASE current IS

WHEN reset =>

IF x = '1' THEN current <= got1; ELSE current <= reset; END IF;

WHEN got1 =>

IF x = '0' THEN current <= got10; ELSE current <= got1; END IF;

WHEN got10 =>

IF x = '1' THEN current <= got101; ELSE current <= reset; END IF;

WHEN got101 :

IF x = '1' THEN current <= got1011; ELSE current <= got10; END IF;

WHEN got1011 =:

IF x = '1' THEN current <= got1; ELSE current <= got10; END IF;

END CASE;

END IF;

END PROCESS;

z <= '1' WHEN current = got1011 ELSE '0';

END most_behavioral_state_machine;

10-21

```

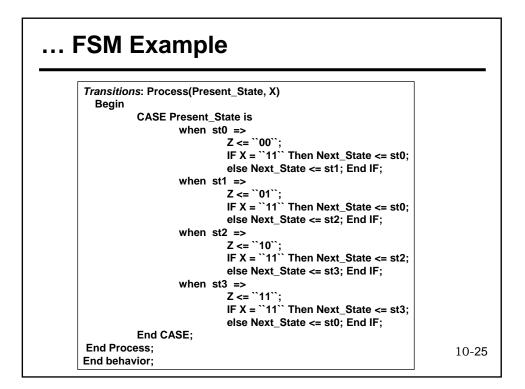

## Generalized VHDL Moore Model

| M Example                                  |             |  |

|--------------------------------------------|-------------|--|

|                                            |             |  |

| Entity fsm is                              |             |  |

| port ( Clk, Reset : in Std_Logic;          | 0           |  |

| X : in Std_Logic_Vector(0 to               |             |  |

| Z : out Std_Logic_Vector(1 de              | ownto 0));  |  |

| End fsm;                                   |             |  |

|                                            | ]           |  |

| Architecture behavior of fsm is            |             |  |

| Type States is (st0, st1, st2, st3);       |             |  |

| Signal Present_State, Next_State : States; |             |  |

| Begin                                      |             |  |

| <i>reg</i> : Process(Reset, Clk)           |             |  |

| Begin                                      |             |  |

| IF Reset = `1` Then                        |             |  |

| Present_State <= st0; Machine Re           | eset to st0 |  |

| elsIF (CIk`EVENT and CIk = `1`) Then       |             |  |

| Present_State <= Next_state;               |             |  |

| End IF;                                    |             |  |

| End Process;                               |             |  |

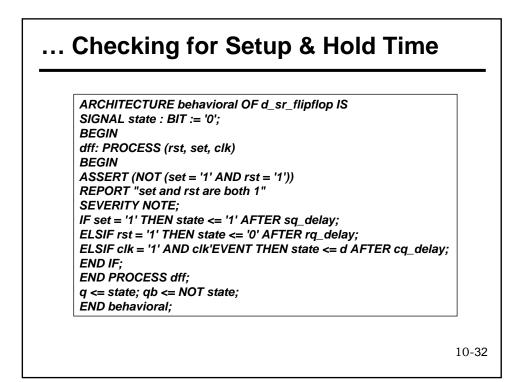

### Assert Statement ...

Syntax:

ASSERT assertion\_condition REPORT "reporting\_message" SEVERITY severity\_level;

Semantics

- Make sure that assertion\_condition is true

- Otherwise report "reporting message" then

- Take the severity\_level action

- Severity: FAILURE ERROR WARNING NOTE

- Use assert to flag violations

- Use assert to report events

- Can be sequential or concurrent

| BEGIN                                 |                                            |

|---------------------------------------|--------------------------------------------|

| dff: PROCESS (rst, set, clk)<br>BEGIN |                                            |

| ASSERT                                |                                            |

| (NOT (set = '1' AND rst = '1'))       | <ul> <li>Conditions are checked</li> </ul> |

| REPORT                                | only when process is                       |

| "set and rst are both 1"              |                                            |

| SEVERITY NOTE;                        | activated                                  |

| IF set = '1' THEN                     | <ul> <li>Make sure that set='1'</li> </ul> |

| state <= '1' AFTER sq_delay;          | AND rst='1' does not                       |

| ELSIF rst = '1' THEN                  | happen                                     |

| state <= '0' AFTER rq_delay;          |                                            |

| ELSIF clk = '1' AND clk'EVENT THEN    | <ul> <li>Severity NOTE issues</li> </ul>   |

| state <= d AFTER cq_delay;            | message                                    |

| END IF;                               | 5                                          |

| END PROCESS dff;                      |                                            |

| q <= state;                           |                                            |

| qb <= NOT state;                      | 10-                                        |

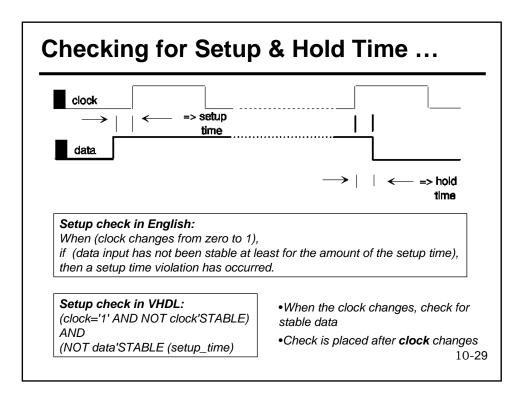

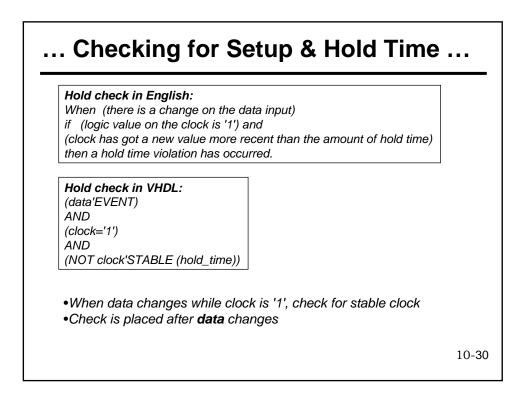

### ... Checking for Setup & Hold Time ...

ENTITY d\_sr\_flipflop IS GENERIC (sq\_delay, rq\_delay, cq\_delay : TIME := 6 NS; set\_up, hold : TIME := 4 NS); PORT (d, set, rst, clk : IN BIT; q, qb : OUT BIT); BEGIN ASSERT (NOT (clk = '1' AND clk'EVENT AND NOT d'STABLE(set\_up) )) REPORT "Set\_up time violation" SEVERITY WARNING; ASSERT (NOT (d'EVENT AND clk = '1' AND NOT clk'STABLE(hold) )) REPORT "Hold time violation" SEVERITY WARNING; END d\_sr\_flipflop;

Concurrent assertion statementsCan be placed also in the architecture

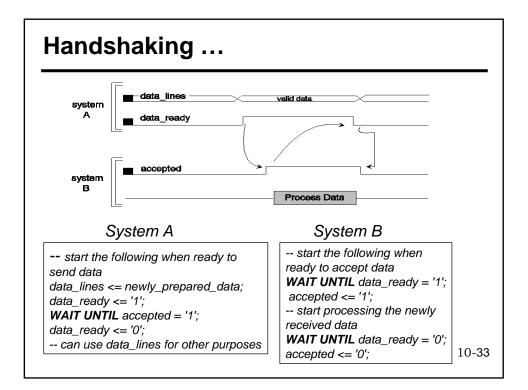

| Handshaking                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARCHITECTURE waiting OF system_i IS<br>SIGNAL buffer_full, buffer_picked : BIT := '0';<br>SIGNAL word_buffer : BIT_VECTOR (15 DOWNTO 0);<br>BEGIN<br>a_talk: PROCESS<br>BEGIN<br><br>Talk to A, collect 4 4-bit data, keep a count<br>When ready, pass 16-bit data to b_talk<br><br>END PROCESS a_talk;<br>b_talk: PROCESS<br>BEGIN<br><br>Wait for 16-bit data from a_talk<br>When data is received, send to B using proper<br>handshaking | •a_talk process &<br>b_talk process talk to<br>each other<br>•Use buffer_full,<br>buffer_picked, and<br>word_buffer for a_talk<br>and b_talk<br>communication |

| END PROCESS b_talk;<br>END waiting;                                                                                                                                                                                                                                                                                                                                                                                                         | 10-35                                                                                                                                                         |

| A talk: PROCESS                                  |     |

|--------------------------------------------------|-----|

| VARIABLE count : INTEGER RANGE 0 TO 4 := 0;      |     |

| BEGIN                                            |     |

| WAIT UNTIL in_ready = '1';                       |     |

| count := count + 1;                              |     |

| CASE count IS                                    |     |

| WHEN 0 => NULL;                                  |     |

| WHEN 1 => word_buffer (03 DOWNTO 00) <= in_data; |     |

| WHEN 2 => word_buffer (07 DOWNTO 04) <= in_data; |     |

| WHEN 3 => word_buffer (11 DOWNTO 08) <= in_data; |     |

| WHEN 4 => word_buffer (15 DOWNTO 12) <= in_data; |     |

| buffer full <= '1';                              |     |

| WAIT UNTIL buffer_picked = '1';                  |     |

| buffer_full <= '0'; count := 0;                  |     |

| END CASE;                                        |     |

| in_received <= '1';                              |     |

| WAIT UNTIL in_ready = '0';                       |     |

| in_received <= '0';                              |     |

| END PROCESS a talk;                              | 10- |

## Handshaking ...

b\_talk: PROCESS BEGIN -- communicate with a\_talk process IF buffer\_full = '0' THEN WAIT UNTIL buffer\_full = '1'; END IF; out\_data <= word\_buffer; buffer\_picked <= '1'; WAIT UNTIL buffer\_full = '0'; buffer\_picked <= '0'; -- communicate with system B out\_ready <= '1'; WAIT UNTIL out\_received = '1'; out\_ready <= '0'; END PROCESS b\_talk;

The IF buffer\_full = '0' statement is used so that the WAIT Until does not hold the process if buffer\_full is already '1' when this statement is reached

## ... Formatted I/O ...

TYPE state IS (reset, got1, got10, got101); TYPE state\_vector IS ARRAY (NATURAL RANGE <>) OF state; FUNCTION one\_of (sources : state\_vector) RETURN state IS USE STD.TEXTIO.ALL; VARIABLE I : LINE; FILE flush : TEXT IS OUT "/dev/tty"; BEGIN FOR i IN sources'RANGE LOOP WRITE (I, state'IMAGE(sources(I)), LEFT, 7); END LOOP; WRITELINE (flush, I); RETURN sources (sources'LEFT); END one\_of;

Add screen output to resolution function

The 'IMAGE type attribute translates a state to its corresponding string

The keyword LEFT specifies left justification

7 specifies the string length 10-39

| USE STD.TEXTIO.ALL;<br>PROCEDURE display (SIGNAL value1,<br>value2 : BIT) IS<br>FILE flush : TEXT OPEN APPEND_MODE<br>is "debug.txt";<br>VARIABLE filler : STRING (1 TO 4) := " "<br>VARIABLE 1 : LINE;<br>BEGIN<br>WRITE (I, NOW, RIGHT, 8, NS);<br>IF value1'EVENT THEN<br>WRITE (I, value1, RIGHT, 3);<br>WRITE (I, filler, LEFT, 0);<br>ELSE<br>WRITE (I, filler, LEFT, 0);<br>WRITE (I, value2, RIGHT, 3);<br>END IF;<br>WRITELINE (flush, I);<br>END display; | <ul> <li>An EVENT on value1 or value puts the following in I:<br/>NOW</li> <li>An EVENT on value1 puts the following in I:<br/>v1</li> <li>An EVENT on value2 puts the following in I:<br/> v2</li> <li>WRITELINE writes:<br/>time v1<br/>time v2</li> </ul> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|