## COE 405 Hardware Design Environments

Dr. Aiman H. El-Maleh Computer Engineering Department King Fahd University of Petroleum & Minerals

### Outline

- Welcome to COE 405

- Digital System Design

- Design Domains and Levels of Abstractions

- Synthesis Process

- Objectives of VHDL

- Styles in VHDL

- Design Flow in VHDL

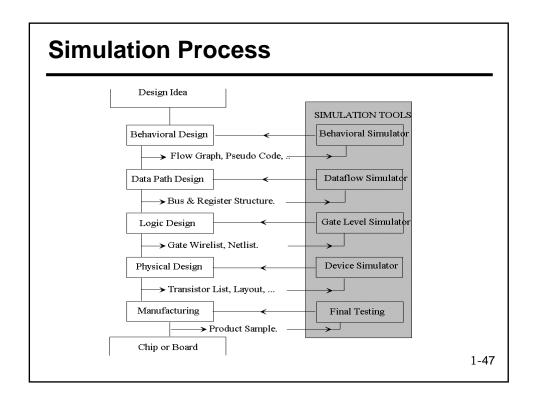

- Simulation Process

### Welcome to COE 405

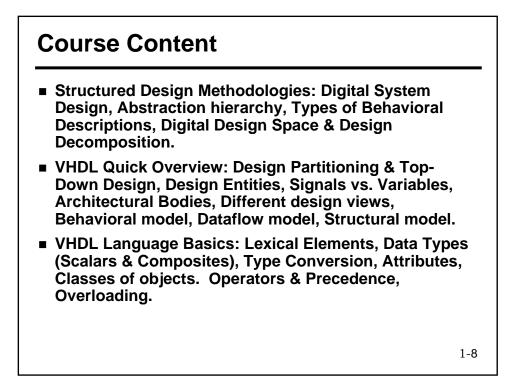

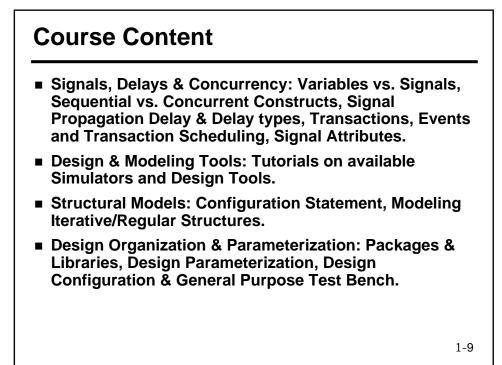

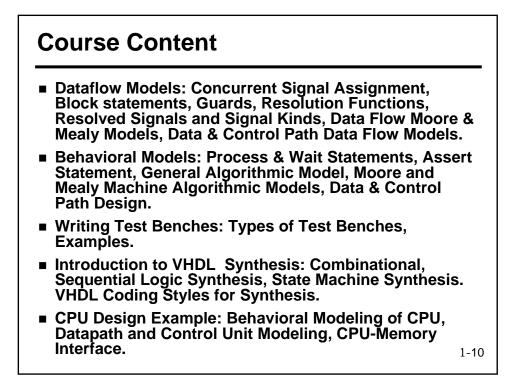

- Catalog Description

- Design methodology. Hardware modeling basics. Modeling concurrency and timing aspects. Behavioral, structural, and data flow level modeling using hardware description languages (HDLs). System level modeling and design of practical processors, controllers, arithmetic units, etc. Translation of instruction sets to hardware models for software emulation. Case studies.

- Prerequisite: COE 308 or consent of instructor

- Instructor Dr. Aiman H. El-Maleh. Room: 22/318 Phone: 2811 Email: <u>aimane@ccse.kfupm.edu.sa</u>

- Office Hours SMW 10:00-10:50, and by appointment

| Grading Policy                                                          |                                                                            |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Assignments                                                             | 15%                                                                        |

| Quizzes                                                                 | 10%                                                                        |

| Exam I                                                                  | 15% (Th., Mar. 29, 1:00 PM)                                                |

| Exam II                                                                 | 20% (Th. , May 10, 1:00 PM)                                                |

| Project                                                                 | 20%                                                                        |

| Final                                                                   | 20%                                                                        |

| <ul> <li>Attendance will be taken</li> </ul>                            | regularly.                                                                 |

|                                                                         | norized absences must be presented no wing resumption of class attendance. |

| <ul> <li>Late assignments will be<br/>penalized 10% per each</li> </ul> | accepted (upto 3 days) but you will be late day.                           |

| <ul> <li>A student caught cheatin<br/>15%.</li> </ul>                   | g in any of the assignments will get 0 out of                              |

| • No makeup will be made                                                | for missing Quizzes or Exams.                                              |

|                                                                         | 1-7                                                                        |

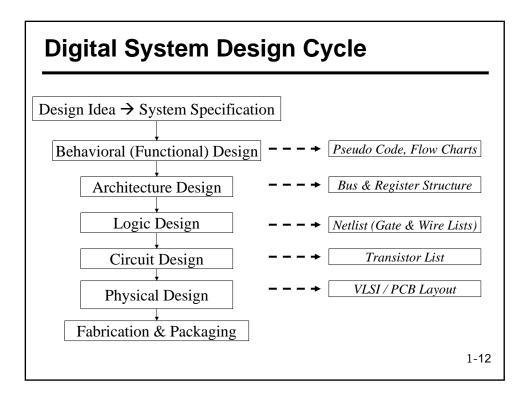

# Digital System Design

#### Realization of a specification subject to the optimization of

- Area (Chip, PCB)

- Lower manufacturing cost

- Increase manufacturing yield

- Reduce packaging cost

- Performance

- Propagation delay (combinational circuits)

- Cycle time and latency (sequential circuits)

- Throughput (pipelined circuits)

- Power dissipation

- Testability

- Earlier detection of manufacturing defects lowers overall cost

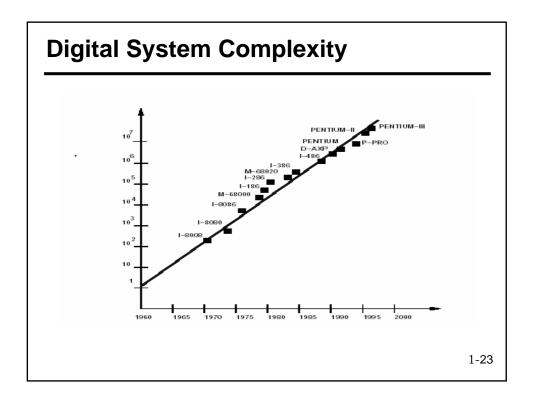

- Design time (time-to-market)

- Cost reduction

- Be competitive

### **Observations**

- Design involves trade-offs between

- Cost

- Performance

- Testability

- Power dissipation

- Fault tolerance

- Ease of design

- Ease of making changes to the design.

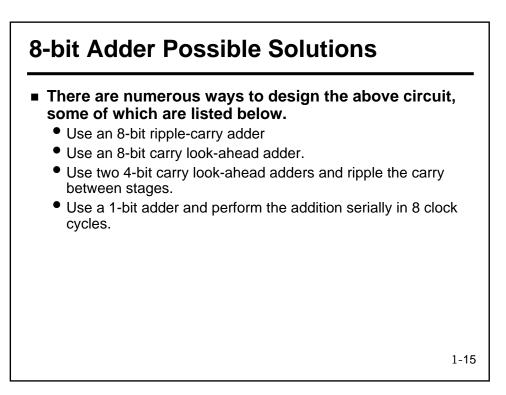

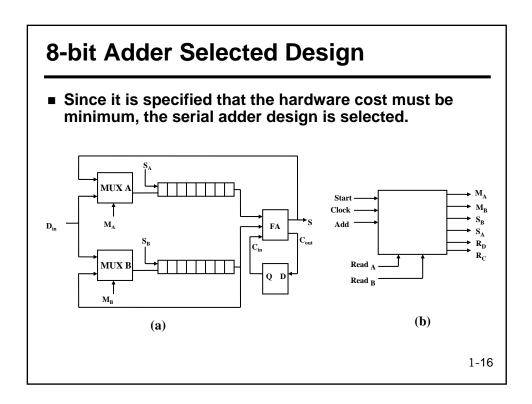

- Serial is cheap but slow, parallel fastest in terms of performance but most costly.

- The different ways we can think of building an 8-bit adder constitutes what is known as *design space* (at a particular level of abstraction).

- Each method of implementation is called a point in the design space.

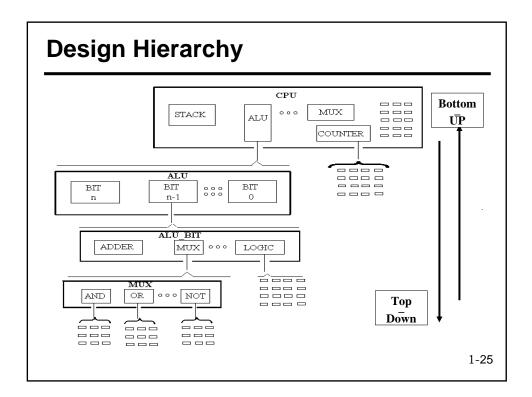

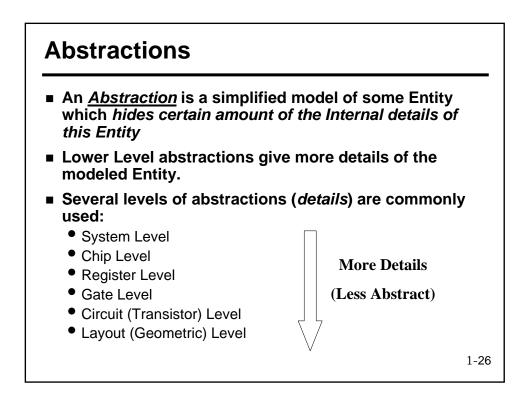

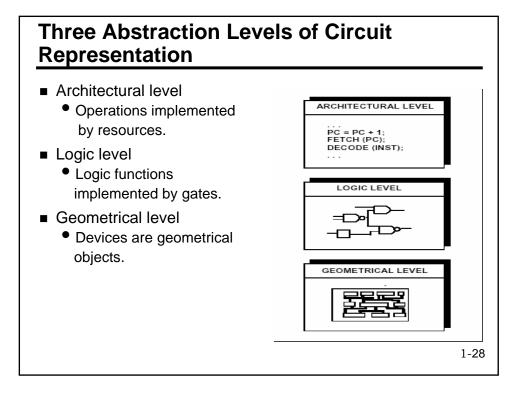

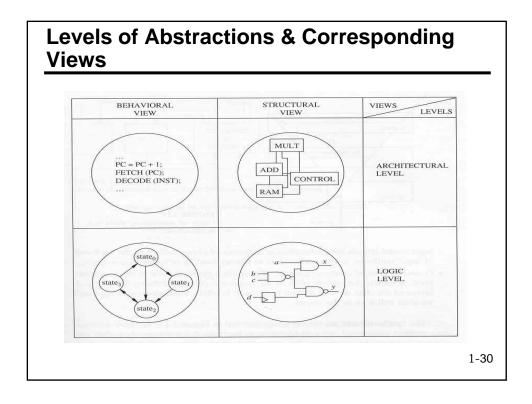

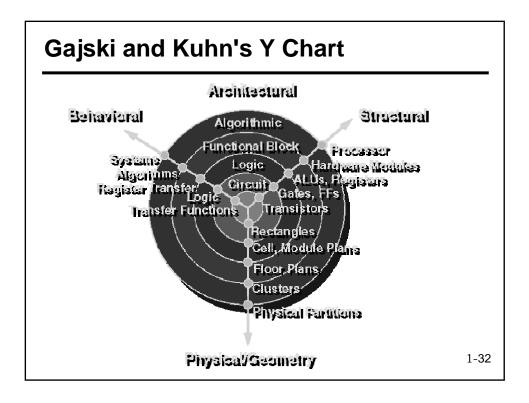

#### Design Domains & Levels of Abstraction

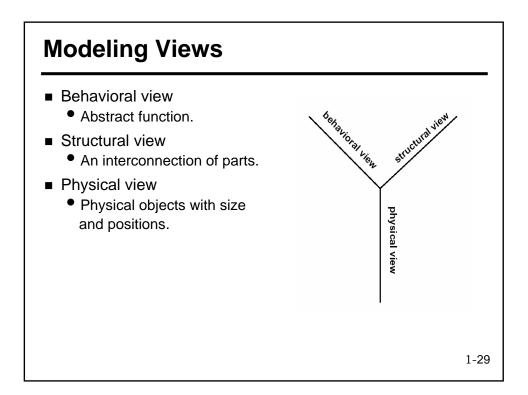

- Designs can be expressed / viewed in one of <u>three</u> possible domains

- Behavioral Domain (*Behavioral View*)

- Structural/Component Domain (Structural View)

- Physical Domain (Physical View)

- A design modeled in a given domain can be represented at several levels of abstraction (*Details*).

| esign Dol<br>evels of A |                                   |                                                |                                                      |     |

|-------------------------|-----------------------------------|------------------------------------------------|------------------------------------------------------|-----|

|                         | Design Dom                        | ain                                            |                                                      |     |

| Abstraction Level       | Behavioral                        | Structural                                     | Physical                                             |     |

| System                  | English Specs                     | Computer,<br>Disk Units,<br>Radar, etc.        | Boards, MCMs,<br>Cabinets,<br>Physical<br>Partitions |     |

| Chip                    | Algorithms,<br>Flow Charts        | Processors,<br>RAMs, ROMs                      | Clusters, Chips,<br>PCBs                             |     |

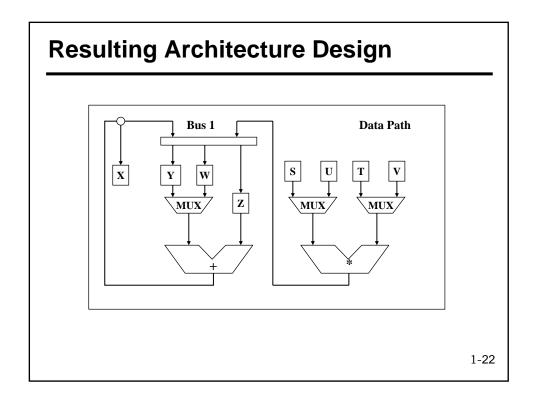

| Register                | Data Flow, Reg.<br>Transfer       | Registers,<br>ALUs,<br>Counters,<br>MUX, Buses | Std. Cells, Floor<br>Plans                           |     |

| Gate                    | Boolean<br>Equations              | AND, OR,<br>XOR, FFs, etc                      | Cells, Module<br>Plans                               |     |

| Circuit (Tr)            | Diff, and<br>element<br>Equations | Transistors, R,<br>C, etc                      | Mask Geometry<br>(Layout)                            |     |

|                         |                                   |                                                |                                                      | 1-3 |

### **Design Methods**

- Full custom

- Maximal freedom

- High performance blocks

- Slow

#### Semi-custom

- Gate Arrays

- Mask Programmable (MPGAs)

- Field Programmable (FPGAs))

- Standard Cells

- Silicon Compilers & Parametrizable Modules (adder, multiplier, memories)

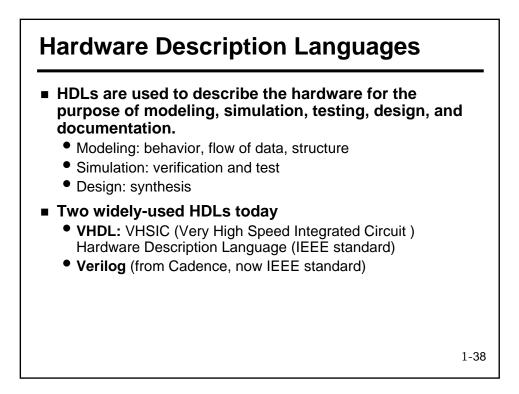

### **Objectives of VHDL**

- Provide a unified notation to describe Electronic Systems (digital hardware) at various levels of abstractions.

- Standardization of documentation

To support the communication of design data

- System design time and cost

- reduced ambiguity in specification of design interfaces and design functions

- reusability of existing designs

- Open-system CAE tools

- can change CAE system without losing use of existing designs

- elimination of language translators

- Improved integration of multi-vendor designs

- shared design databases become possible

- standard cells, behavioral models

1-39

### **VHDL Requirements**

- Support for design hierarchy

- Library support

- Sequential statement

- Generic design

- Type declaration and usage

- Use of subprograms

- Timing control

- Structural specification

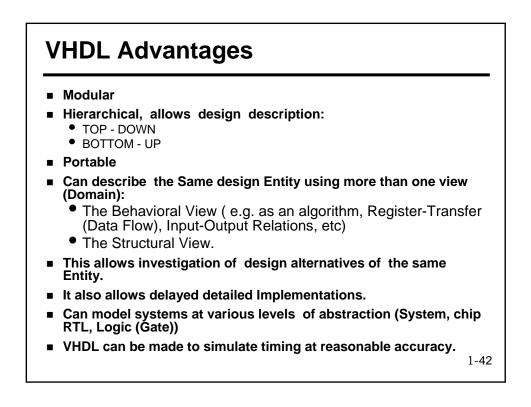

# **Styles in VHDL**

#### Behavioral

- High level, algorithmic, sequential execution

- Hard to synthesize well

- Easy to write and understand (like high-level language code)

#### Dataflow

- Medium level, register-to-register transfers, concurrent execution

- Easy to synthesize well

- Harder to write and understand (like assembly code)

#### Structural

- Low level, netlist, component instantiations and wiring

- Trivial to synthesize

- Hardest to write and understand (very detailed and low level)

1-43

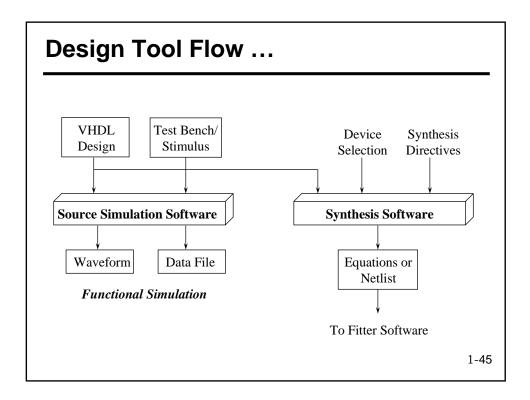

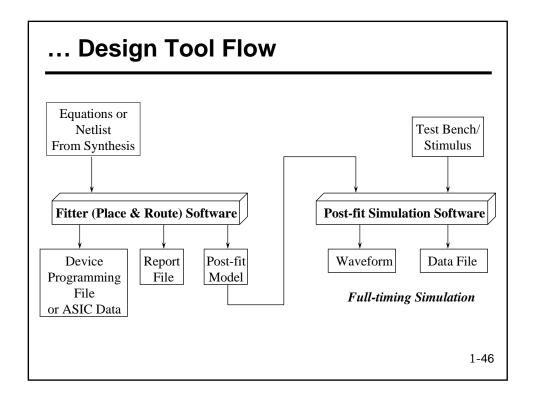

#### **Design Flow in VHDL** Define the design requirements Describe the design in VHDL • Top-down, hierarchical design approach • Code optimized for synthesis or simulation Simulate the VHDL source code Early problem detection before synthesis Synthesize, optimize, and fit (place and route) the design for a device Synthesize to equations and/or netlist • Optimize equations and logic blocks subject to constraints • Fit into the components blocks of a given device Simulate the post-layout design model Check final functionality and worst-case timing Program the device (if PLD) or send data to ASIC vendor 1-44

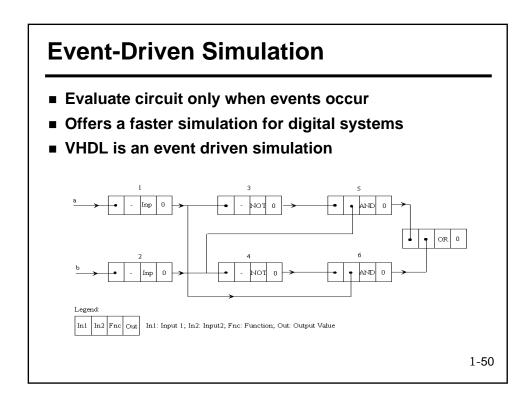

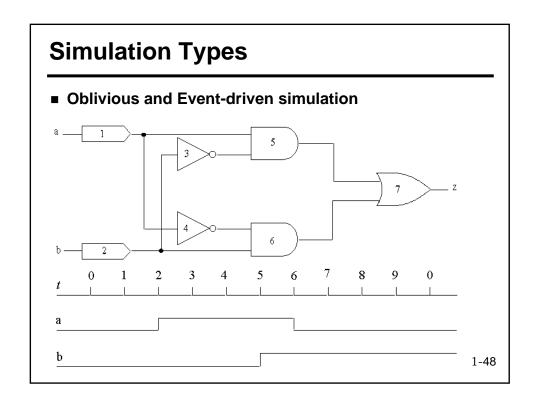

### **Oblivious Simulation**

- Need a tabular netlist for oblivious simulation

- Simulate fixed time intervals

- Update table values at each interval

| 1     Input     a     -     0       2     Input     b     -     0       3     NOT     2     -     1       4     NOT     1     -     1       5     AND     1     3     0       6     AND     4     2     0       7     OR     5     6     0 | 2 Input b - 0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 3         NOT         2         -         1           4         NOT         1         -         1           5         AND         1         3         0           6         AND         4         2         0                              |               |

| 4         NOT         1         -         1           5         AND         1         3         0           6         AND         4         2         0                                                                                    |               |

| 5 AND 1 3 0<br>6 AND 4 2 0                                                                                                                                                                                                                 |               |

| 6 AND 4 2 0                                                                                                                                                                                                                                | 4 NOT 1 - 1   |

|                                                                                                                                                                                                                                            | 5 AND 1 3 0   |

| 7 OR 5 6 0                                                                                                                                                                                                                                 | 6 AND 4 2 0   |

|                                                                                                                                                                                                                                            | 7 OR 5 6 0    |

|                                                                                                                                                                                                                                            |               |

|                                                                                                                                                                                                                                            |               |