## COE 405, Term 131

## **Design & Modeling of Digital Systems**

## Quiz# 4

Date: Sunday, Dec. 15, 2013

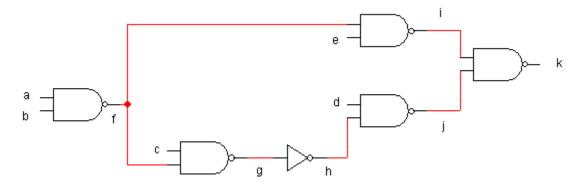

**Q.1.** Consider the logic network below with inputs {*a*, *b*, *c*, *d*, *e*} and output {*k*}:

Assume that the delay of the inverter gate is 1 and that the delay of the 2-input NAND gate is 2. Also, assume that the input data-ready times are zero except for input *a*, which is equal to 2.

(i) Compute the data ready times and slacks for all vertices in the network.

| cin | Data ready time            | Data required time              | Black               |

|-----|----------------------------|---------------------------------|---------------------|

|     | $t_a = 2$                  | $\overline{t}_a = 4 - 2 = 2$    | $S_a = 2 - 2 = 0$   |

|     | $t_b = 0$                  | $\overline{t}_b = 4 - 2 = 2$    | SL = 2-0=2          |

|     | tc = 0                     | $\overline{t}_c = 6 - 2 = 4$    | $S_c = 4 - 0 = 4$   |

|     | td =0                      | to = 9-2=7                      | SJ = 7-0=7          |

|     | te=o                       | te = 9 - 2 = 7                  | Se = 7-0=7          |

|     | 4 = 2 + 2 = 4              | $\overline{t}_{f} = 6 - 2 = 4$  | $s_{f} = 4 - 4 = 0$ |

|     | 4g = 4+2 = 6               | $\overline{E}_{g} = 7 - 1 = 6$  | 59 = 6 - 6 = 0      |

|     | $e_h = 6 + 1 = 7$          | $\overline{kh} = 9 - 2 = 7$     | Sh = 7-7=0          |

|     | ti = 4 + 2 = 6             | $\bar{t}_{e} = 11 - 2 = 9$      | $S_{i} = 9 - 6 = 3$ |

| -   | $\epsilon_{j} = 7 + 2 = 9$ | $\overline{E}_{j} = 11 - 2 = 9$ | 50 = 9-9=0          |

| -   | $t_{\rm K} = 9 + 2 = 11$   | En = 11                         | SK=11-11=0          |

- (ii) Determine the topological critical path.

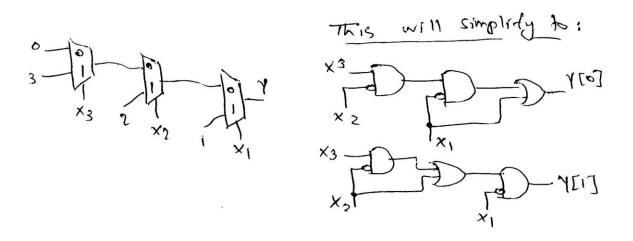

- (iii) Suggest an implementation of the function k using only inverters and 2-input NAND gates to reduce the delay of the circuit to the minimum possible and determine the maximum propagation delay in the optimized circuit. Has the area been affected?

(111)

$$K = fe + dh = fe + fcd = f(e+cd)$$

=  $(ab)(e+cd)$

This leads to the following implementation:

The maximum propagation delay in the optimized circuit is 7. The number of liderals in the original circuit is 11. The number of liderals in the optimized circuit is b. Thus, the area has also been reduced.

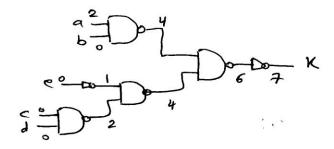

- **Q.2.** Determine possible circuits that will be synthesized by each of the following modules:

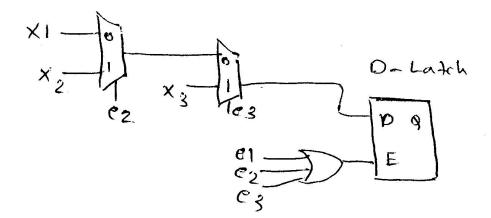

- (i) module m1 (output [1:0] y, input x1, x2, x3); assign y = x1?1:x2?2:x3?3:0; endmodule

(ii) module m2 (output reg y, input e1, e2, e3, x1, x2, x3); always @ (e1, e2, e3, x1, x2, x3) begin if (e1) y=x1; if (e2) y=x2;

end

endmodule

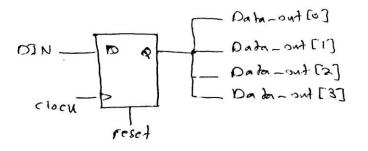

(iii) module m3 (output reg [3:0] Data\_out, input DIN, clock, reset); always @ (posedge clock, posedge reset) begin if (reset) Data\_out = 0; else begin Data\_out[0]=DIN; Data\_out[1]=Data\_out[0]; Data\_out[2]=Data\_out[1];

Data\_out[3]=Data\_out[2];

end end endmodule

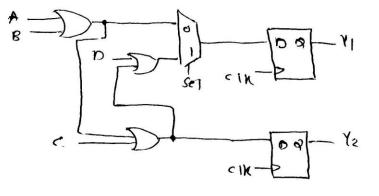

(iv) module m4 (output reg Y1, Y2, input A, B, C, D, sel, clk); always @ (posedge clk) begin Y1 = A | B; Y2 = Y1 | C;if (sel) Y1 = Y2 | D;

end

endmodule