## COE 405, Term 131

## **Design & Modeling of Digital Systems**

## Quiz# 4

Date: Sunday, Dec. 15, 2013

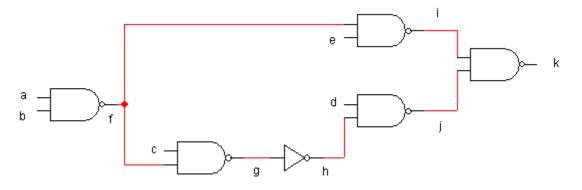

**Q.1.** Consider the logic network below with inputs  $\{a, b, c, d, e\}$  and output  $\{k\}$ :

Assume that the delay of the inverter gate is 1 and that the delay of the 2-input NAND gate is 2. Also, assume that the input data-ready times are zero except for input *a*, which is equal to 2.

- (i) Compute the data ready times and slacks for all vertices in the network.

- (ii) Determine the topological critical path.

- (iii) Suggest an implementation of the function k using only inverters and 2-input NAND gates to reduce the delay of the circuit to the minimum possible and determine the maximum propagation delay in the optimized circuit. Has the area been affected?

- **Q.2.** Determine possible circuits that will be synthesized by each of the following modules:

- (i) module m1 (output [1:0] y, input x1, x2, x3); assign y = x1?1:x2?2:x3?3:0; endmodule

```

(ii) module m2 (output reg y, input e1, e2, e3, x1, x2, x3);

always @ (e1, e2, e3, x1, x2, x3) begin

if (e1) y=x1;

if (e2) y=x2;

if (e3) y=x3;

end

endmodule

```

(iii) module m3 (output reg [3:0] Data\_out, input DIN, clock, reset); always @ (posedge clock, posedge reset) begin if (reset) Data\_out = 0; else begin Data\_out[0]=DIN; Data\_out[1]=Data\_out[0]; Data\_out[2]=Data\_out[1]; Data\_out[3]=Data\_out[2]; end end endmodule

(iv) module m4 (output reg Y1, Y2, input A, B, C, D, sel, clk); always @ (posedge clk) begin Y1= A | B; Y2 = Y1 | C; if (sel) Y1 = Y2 | D; end endmodule