Name: Id#

## **COE 405, Term 062**

## **Design & Modeling of Digital Systems**

## Quiz#1

Date: Saturday, March 17, 2007

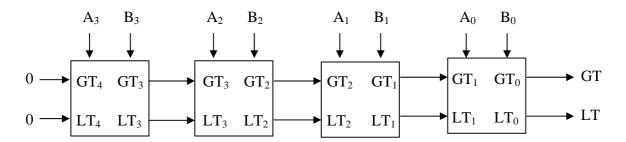

**Q.1.** It is required to model a 4-bit comparator that compares two 4-bit numbers A=A<sub>3</sub>A<sub>2</sub>A<sub>1</sub>A<sub>0</sub> and B=B<sub>3</sub>B<sub>2</sub>B<sub>1</sub>B<sub>0</sub>, and produces two outputs GT and LT. If A>B, then the output signal GT is set to 1 and LT is set to 0. If A<B, then the output signal LT is set to 1, and GT is set to 0. Otherwise both signals will be set to 0, which indicates that the two numbers are equal (i.e. A=B). The 4-bit comparator circuit can be designed in a modular way as shown below:

The equations for the 1-bit magnitude comparator can be found to be:

$$GT_{i} = GT_{i+1} + \overline{LT_{i+1}}A_{i}\overline{B_{i}}$$

$$LT_{i} = LT_{i+1} + \overline{GT_{i+1}}A_{i}B_{i}$$

- (i) Describe an Entity **COMP** for a 1-bit magnitude comparator.

- (ii) Model an Architecture Conc for the 1-bit magnitude comparator (COMP) using concurrent statements.

- (iii) Describe an Entity **COMP4** for a 4-bit magnitude comparator.

- (iv) Model Architecture **Struct** for the 4-bit magnitude comparator (**COMP4**) using instantiations of the Entity **COMP**.