# COE 405, Term 152

# **Design & Modeling of Digital Systems**

# HW#2 Solution

# Due date: Thursday, Feb. 25

**Q.1.** It is required to design a sequential circuit that has a single input X representing a signed 2's complement number and a single output Y. The circuit receives the number serially through the input X from the least significant bit (LSB) to the most significant bit (MSB), and computes the equation Y=3\*X-2 and generates the output serially from the least significant bit to the most significant bit. The circuit has an additional asynchronous reset input R that resets the circuit into an initial state. The following are examples of input and output data:

| <u>Examp</u> | oles:  |   | LSB |   |   |   | MSB |                      |

|--------------|--------|---|-----|---|---|---|-----|----------------------|

|              | Input  | Х | 0   | 1 | 1 | 0 | 0   | Input=6<br>Output=16 |

|              | Output | Y | 0   | 0 | 0 | 0 | 1   | Output=16            |

|              | LSB    |   |     |   |   |   | MSB |                      |

|              | Input  | Х | 1   | 1 | 0 | 0 | 0   | Input=3<br>Output=7  |

|              | Output | Y | 1   | 1 | 1 | 0 | 0   | Output=7             |

(i) Draw the state diagram of the circuit assuming a **Mealy** model.

| Present State | Next State, Y |       |  |

|---------------|---------------|-------|--|

|               | X=0           | X=1   |  |

| S0 (B=2)      | S1, 0         | S2, 1 |  |

| S1 (B=1)      | S1, 1         | S3, 0 |  |

| S2 (B=0)      | S2, 0         | S3, 1 |  |

| S3 (C=1)      | S2, 1         | S4, 0 |  |

| S4 (C=2)      | S3, 0         | S4, 1 |  |

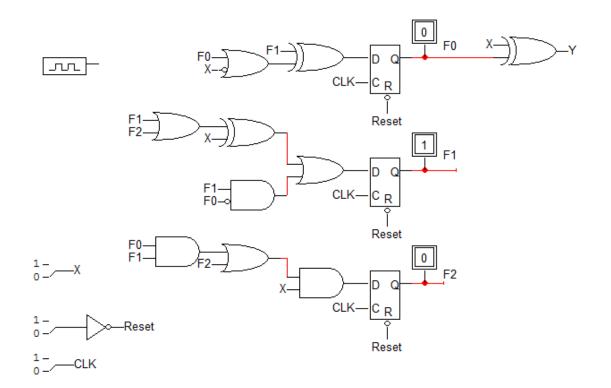

(ii) Implement the circuit using D-FFs.

Since we have 5 states, we need 3 FFs: F2, F1, and F0. We will use the following encoding: S0=000, S1=001, S2=010, S3=011, S4=100.

| Present State | Next  | : State, Y |

|---------------|-------|------------|

| F2F1F0        | X=0   | X=1        |

| 0 0 0         | 001,0 | 010,1      |

| 0 0 1         | 001,1 | 011,0      |

| 010           | 010,0 | 011,1      |

| 011           | 010,1 | 100,0      |

| 100           | 011,0 | 100,1      |

|    | 00          | 01          | 11   | 10          |  |

|----|-------------|-------------|------|-------------|--|

| 00 | 0 0         | <b>1</b> 1  | 03   | 1 2         |  |

| 01 | 04          | 1 5         | 0 7  | 16          |  |

| 11 | <b>?</b> 12 | <b>?</b> 13 | ? 15 | ? 14        |  |

| 10 | 08          | 19          | ?11  | <b>?</b> 10 |  |

$Y=F0'\;X+F0\;X'=F0\oplus X$

|    | 00 01       |             | 11   | 10          |

|----|-------------|-------------|------|-------------|

| 00 | 1 0         | 0 1         | 13   | 1 2         |

| 01 | 04          | 15          | 0 7  | 06          |

| 11 | <b>?</b> 12 | <b>?</b> 13 | ? 15 | ? 14        |

| 10 | 18          | 09          | ?11  | <b>?</b> 10 |

$F0+ = F1' F0 + F1' X' + F1 F0' X = F1' (F0 + X') + F1 F0' X = F1 \oplus (F0 + X')$

|    | 00          | 01  | 11   | 10          |

|----|-------------|-----|------|-------------|

| 00 | 0 0         | 1 1 | 13   | 02          |

| 01 | 14          | 1 5 | 0 7  | 1 6         |

| 11 | <b>?</b> 12 | ?13 | ? 15 | ? 14        |

| 10 | 18          | 09  | ?11  | <b>?</b> 10 |

$\begin{array}{l} F1+=F2'F1'\;X+F1\;F0'+F1\;X'+F2\;X'=\;F2'F1'\;X+X'\;(F1+F2)+F1\;F0'\\ =X\;\oplus(F1+F2)+F1\;F0'\end{array}$

|    | 00   | 01  | 11          | 10   |

|----|------|-----|-------------|------|

| 00 | 0 0  | 0 1 | 03          | 02   |

| 01 | 04   | 05  | 1 7         | 06   |

| 11 | ? 12 | ?13 | <b>?</b> 15 | ? 14 |

| 10 | 08   | 19  | ?11         | ?10  |

F2+ = F2 X + F1 F0 X = X (F2 + F1 F0)

(iii) Verify the correctness of your circuit by simulation.

Input: 01100 (X=6) Output: 00001 (Y=16)

|             | 49400 | 49600 | 49 | 800 | 50000 | 50200 |

|-------------|-------|-------|----|-----|-------|-------|

| CLK         |       |       |    |     |       |       |

| Reset<br>F0 |       |       |    |     |       |       |

| F1          |       |       |    |     |       |       |

| F2<br>X     |       |       |    |     |       |       |

| Ŷ           |       |       |    |     |       |       |

|             |       |       |    | I   |       |       |

Input: 11000 (X=3) Output: 11100 (Y=7)

|             | 51200 | <br>51400 | 51600 |   | 51800 |

|-------------|-------|-----------|-------|---|-------|

| CLK         |       |           |       |   |       |

| Reset<br>F0 |       |           |       |   |       |

| F1          |       |           |       |   |       |

| F2<br>X     |       |           |       |   |       |

| Y           | 「     |           |       |   |       |

|             |       |           | '     | I | 1     |

**Q.2.** Consider the given FSM that has 6 states, two inputs X and Y, and one output Z, represented by the following state table:

| Present State |            | Output     |              |            |   |

|---------------|------------|------------|--------------|------------|---|

|               | XY=00      | XY=01      | <b>XY=10</b> | XY=11      | Z |

| S0            | <b>S</b> 0 | <b>S</b> 1 | S2           | <b>S</b> 3 | 1 |

| S1            | <b>S</b> 0 | <b>S</b> 3 | S1           | <b>S</b> 4 | 0 |

| S2            | <b>S</b> 1 | <b>S</b> 3 | S2           | S4         | 1 |

| S3            | <b>S</b> 1 | <b>S</b> 0 | S4           | S5         | 0 |

| S4            | <b>S</b> 0 | <b>S</b> 1 | S2           | S5         | 1 |

| S5            | <b>S</b> 1 | <b>S</b> 4 | <b>S</b> 0   | S5         | 0 |

### (i) Determine the equivalent states.

| <b>S</b> 1 |                   |                   |                   |            |    |

|------------|-------------------|-------------------|-------------------|------------|----|

| <b>S</b> 2 | (0,1), (1,3),     |                   |                   |            |    |

|            | (3,4)             | $\langle \rangle$ |                   | I          |    |

| <b>S</b> 3 |                   | (0,1), (0,3),     |                   |            |    |

|            | $\langle \rangle$ | (1,4), (4,5)      | $\langle \rangle$ |            |    |

| S4         | (3,5)             |                   | (0,1),(1,3),      |            |    |

|            |                   |                   | (4,5)             |            |    |

| S5         |                   | (0,1), (3,4),     |                   | (0.4)      |    |

|            |                   | (4,5)             |                   |            |    |

|            | SO                | S1                | S2                | <b>S</b> 3 | S4 |

Thus, the equivalent states are (S0, S4) and (S3, S5).

(ii) Reduce the state table into the minimum number of states and show the reduced state table.

The reduced state table is as follows:

| Present State |                         | Output     |            |            |   |

|---------------|-------------------------|------------|------------|------------|---|

|               | XY=00 XY=01 XY=10 XY=11 |            |            |            | Z |

| S0            | <b>S</b> 0              | <b>S</b> 1 | S2         | <b>S</b> 3 | 1 |

| S1            | <b>S</b> 0              | <b>S</b> 3 | S1         | <b>S</b> 0 | 0 |

| S2            | S1                      | <b>S</b> 3 | S2         | <b>S</b> 0 | 1 |

| S3            | S1                      | <b>S</b> 0 | <b>S</b> 0 | <b>S</b> 3 | 0 |

**Q.3.** Consider the given FSM that has 4 states, one input (X) and one output (Z), represented by the following state table:

| Present State | Next State, Z |       |  |

|---------------|---------------|-------|--|

|               | X=0           | X=1   |  |

| SO            | S0, 1         | S2, 0 |  |

| S1            | S0, 0         | S2, 0 |  |

| S2            | S1, 0         | S3, 0 |  |

| S3            | S1, 0         | S3, 1 |  |

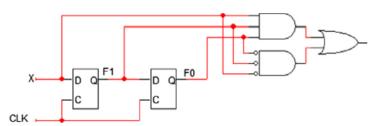

(i) Implement the FSM using the following state assignment: S0=00, S1=01, S2=10, S3=11.

|   | 00  | 01  | 11  | 10 |

|---|-----|-----|-----|----|

| 0 | 1 0 | 0 1 | 03  | 02 |

| 1 | 04  | 05  | 1 7 | 06 |

Y = F1' F0' X' + F1 F0 X

|   | 00  | 01  | 11  | 10  |

|---|-----|-----|-----|-----|

| 0 | 0 0 | 0 1 | 03  | 0 2 |

| 1 | 14  | 1 5 | 1 7 | 16  |

F0+ = F1

|   | 00  | 01         | 11  | 10 |

|---|-----|------------|-----|----|

| 0 | 0 0 | <b>1</b> 1 | 13  | 02 |

| 1 | 04  | 1 5        | 1 7 | 06 |

F1+=X

(ii) Implement the FSM using the following state assignment: S0=01, S1=10, S2=11, S3=00.

|   | 00         | 01  | 11 | 10  |

|---|------------|-----|----|-----|

| 0 | <b>0</b> 0 | 1 1 | 03 | 1 2 |

| 1 | <b>0</b> 4 | 05  | 07 | 06  |

$Z = F1' F0' X + F1' F0 X' = F1' (F0' X + F0 X') = F1' (F0 \oplus X)$

|   | 00  | 01  | 11  | 10  |

|---|-----|-----|-----|-----|

| 0 | 0 0 | 0 1 | 13  | 1 2 |

| 1 | 14  | 1 5 | 0 7 | 06  |

$F0+=F1' F0+F1 F0'=F1 \oplus F0$

|   | 00  | 01  | 11  | 10 |

|---|-----|-----|-----|----|

| 0 | 1 0 | 0 1 | 13  | 02 |

| 1 | 04  | 1 5 | 0 7 | 16 |

$\begin{array}{l} F1+=F1'\ F0'\ X'+F1'\ F0\ X+F1\ F0'\ X+F1\ F0\ X'=F1'\ (F0'\ X'+F0\ X)+F1\ (F0'\ X+F0\ X')\\ =F1\ \oplus\ F0\ \oplus\ X \end{array}$

(iii) Compare the area of the two resulting circuits.

The number of literals using the first state assignment is 6 while it is 14 using the second state assignment. We could also say that the first assignment uses an equivalent of 5 2-input primitive gates while the second state assignment uses 10 2-input primitive gates. Therefore, the first assignment produces a significantly lower area than the second assignment.

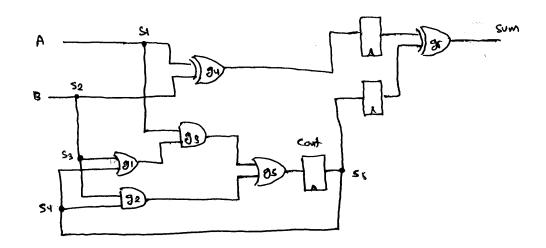

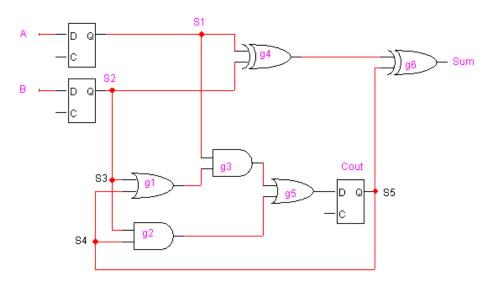

**Q.4.** Consider the circuit given below representing a serial adder. Assume that the delay of a 2-input AND gate is 2 unit delays, the delay of a 2-input OR gate is 2 unit delays and the delay of a 2-input XOR gate is 4 unit delays.

(i) Determine the critical path of this circuit and the maximum propagation delay.

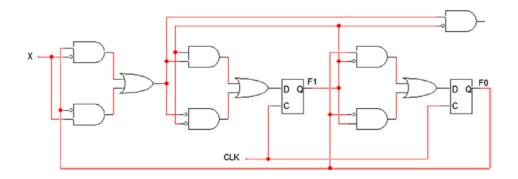

(ii) Using only the **Retiming** transformation, reduce the critical path of this circuit with the minimum number of flip-flops possible.

The critical path can be reduced to 6 without cli Y increasing the number of flip-flops as follows:

The resulting circuit after retiming is: