## COE 405, Term 152

## **Design & Modeling of Digital Systems**

## HW#1 Solution

## Due date: Thursday, Feb. 11

- **Q.1.** Consider the two functions  $f=a \oplus b \oplus c$  and g=a b + a c + b c.

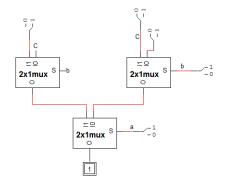

- (i) Implement the function g using only 2x1 MUXs.

$$g = a' [bc] + a [b+c] = a' [b' [0] + b [c]] + a [b'[c] + b[1]]$$

(ii) Compute the function  $f \oplus g$  based on orthonormal basis expansion.

$\begin{array}{l} f = a'b' \ [c] + a'b \ [c'] + ab' \ [c'] + ab \ [c] \\ g = a'b' \ [0] + a'b \ [c] + ab' \ [c] + ab \ [1] \\ f \oplus g = a'b' \ [c] + a'b \ [1] + ab' \ [1] + ab \ [c'] = a'b'c + a'b + ab' + abc' = a'c + a'b + ab' + ac' \\ \end{array}$

- **Q.2.** It is required to design a combinational circuit that computes the equation Y=3\*X-1, where X is an n-bit signed 2's complement number.

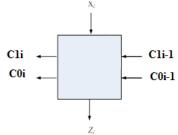

- (i) Design the circuit as a modular circuit where each module receives a single bit of the input, X<sub>i</sub>.

This circuit can be designed by assuming that we have a borrow feeding the first cell or by representing -1 in 2's complement as 11...111 and adding this 1 ion each cell. I will follow the second approach. We need to represent carry-out values in the range 0 to 3. Thus, we need to signals to represent Carry out values.

(ii) Derive the truth table of your 1-bit module in (i).

| C1 <sub>i-1</sub> | C0 <sub>i-1</sub> | Xi | C1 <sub>i</sub> | C0 <sub>i</sub> | Zi |

|-------------------|-------------------|----|-----------------|-----------------|----|

| 0                 | 0                 | 0  | 0               | 0               | 1  |

| 0                 | 0                 | 1  | 1               | 0               | 0  |

| 0                 | 1                 | 0  | 0               | 1               | 0  |

| 0                 | 1                 | 1  | 1               | 0               | 1  |

| 1                 | 0                 | 0  | 0               | 1               | 1  |

| 1                 | 0                 | 1  | 1               | 1               | 0  |

| 1                 | 1                 | 0  | 1               | 0               | 0  |

| 1                 | 1                 | 1  | 1               | 1               | 1  |

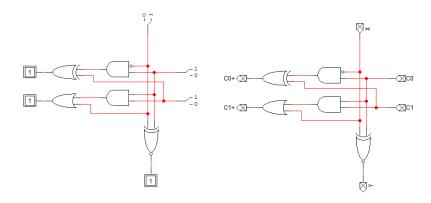

(iii) Derive minimized two-level sum-of-product equations for your 1-bit module circuit.

|   | 00  | 01  | 11  | 10 |

|---|-----|-----|-----|----|

| 0 | 1 0 | 0 1 | 13  | 02 |

| 1 | 14  | 05  | 1 7 | 06 |

|   | 00  | 01  | 11  | 10  |

|---|-----|-----|-----|-----|

| 0 | 0 0 | 0 1 | 03  | 1 2 |

| 1 | 14  | 1 5 | 1 7 | 06  |

$\overline{C0_i} = C1_{i\text{-}1} \ C0_{i\text{-}1}' + C1_{i\text{-}1} \ X_i + C1_{i\text{-}1}' \ C0_{i\text{-}1} \ X_i' = C1_{i\text{-}1} \ (C0_{i\text{-}1}' + X_i) + C1_{i\text{-}1}' \ C0_{i\text{-}1} \ X_i' = C1_{i\text{-}1} \oplus (C0_{i\text{-}1} \ X_i')$

|                                  | 00  | 01  | 11  | 10 |

|----------------------------------|-----|-----|-----|----|

| 0                                | 0 0 | 1 1 | 13  | 02 |

| 1                                | 04  | 15  | 1 7 | 16 |

| $C1_i = X_i + C1_{i-1} C0_{i-1}$ |     |     |     |    |

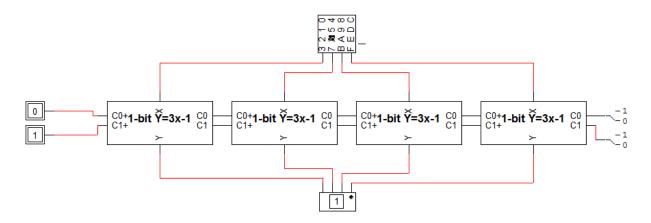

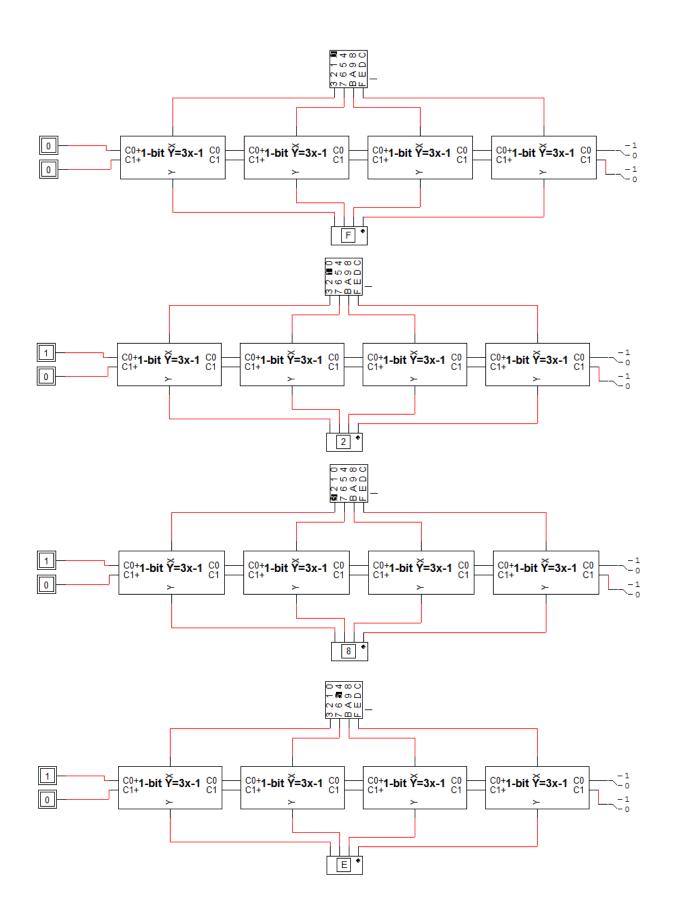

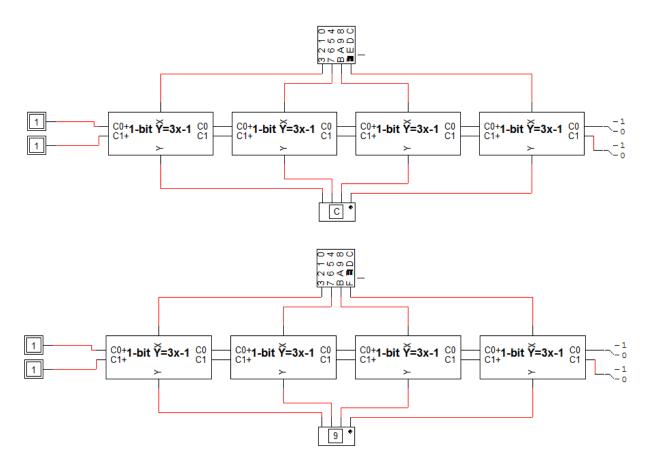

(iv) Verify the correctness of your design by modeling and simulating a circuit to compute the required equation assuming X is a 4-bit number using logicworks.

Note that for values whose correct result will not fit in 4-bits such as values  $\geq 6$  will not produce correct results. We need to use larger number of cells to ensure that the correct output will fit.