## COE 405, Term 131

## **Design & Modeling of Digital Systems**

## HW#1 Solution

## Due date: Sunday, Sep. 29

- **Q.1.** Consider the two functions f=a b c + a' b' c' and g=a b+a' c.

- (i) Implement the function f using a single 4x1 MUX.

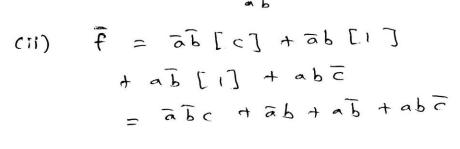

- (ii) Compute the complement of f.

- (iii) Compute the function  $f \oplus g$  based on orthonormal basis expansion.

- **Q.2.** It is required to design a combinational circuit that computes the equation Y=5\*X, where X is an n-bit unsigned number.

- (i) Design the circuit as a modular circuit where each module receives a single bit of the input, X<sub>i</sub>.

- (ii) Derive the truth table of your 1-bit module in (i).

- (iii) Derive minimized two-level sum-of-product equations for your 1-bit module circuit.

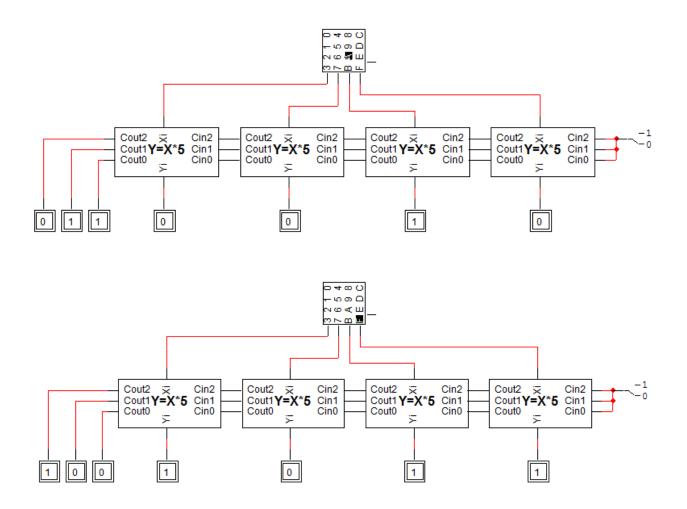

- (iv) Verify the correctness of your design by modeling and simulating a 4-bit circuit using logicworks.

- (v) Assume that the delay of a gate is related to the number of its inputs, i.e. the delay of an inverter is 1, the delay of a 2-input gate is 2, etc. Compute the maximum propagation delay of your n-bit circuit.

- (vi) Verify the correctness of your maximum propagation delay calculation by measuring the longest delay for a 4-bit circuit using logicworks.

Term 131

COE 405

Q1.  $f = abc + \overline{a}\overline{b}\overline{c}$ g = ab + \overline{a}c (i)  $f = \overline{a}\overline{b}[\overline{c}] + \overline{a}b[\overline{o}]$ +  $\overline{a}\overline{b}[\overline{o}] + \overline{a}b[\overline{c}]$   $\overline{c} - \overline{b} - \overline{c}$  $\overline{c} - \overline{b} - \overline{c}$

(iii)

$$g = ab [c] + ab [c] = ab + abc + abc$$

Q2. Y = 5 x X

....

| XI | Cin 2 | CINI | Cino | ( | Cont 2   | Contl |    |        |

|----|-------|------|------|---|----------|-------|----|--------|

|    | 0     | O    | ~    |   | 0        | 0     | 00 |        |

| 0  | 0     | 0    | 1    |   | 0        | 00    | 1  | ~<br>~ |

| 0  | 0     | l    | 0    |   | 0        | 0     | i  |        |

| 0  | 0     | 1    | 1    |   |          |       |    |        |

| ð  | 1     | Ð    | 0    |   | 0        | (     | 0  | 0      |

| 0  | ١     | 0    | l    |   | -        |       |    | _      |

| 0  | (     | ۱    | 0    |   | -        | -     |    |        |

| 0  |       |      | _ I  |   |          |       |    |        |

| l. | 0     | 0    | 0    |   | 0        | 1     | 0  | ł      |

| 1  | C     | 0    | ١    |   | 0        | 1     | ١  | 9      |

| 1  | 0     | ١    | 3    |   | 0        | ١     | (  | ١      |

|    | 0     | 1    |      |   | <u> </u> | 0     | 0  | 0      |

| ١  | (     | 0    | 0    |   | I.       | 0     | 0  | 1      |

| ۱. | 1     | 0.   | 0    |   | -        |       |    | _      |

| 1  | 1     | i i  | 1    |   |          |       | _  | -      |

| ı  | 1     | 1    |      |   |          |       |    |        |

|    |       |      |      |   |          |       |    |        |

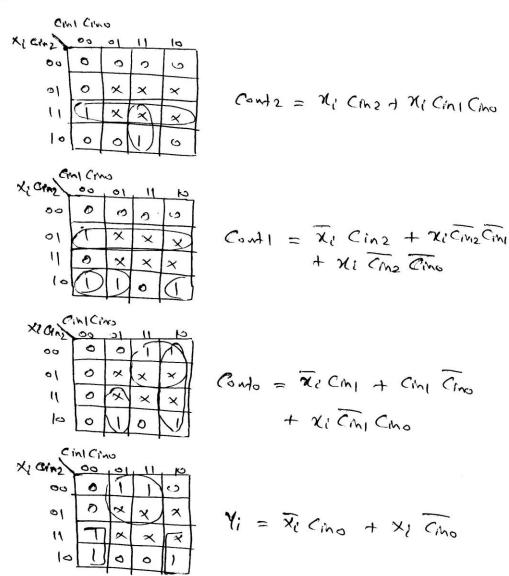

(III)

- 3-

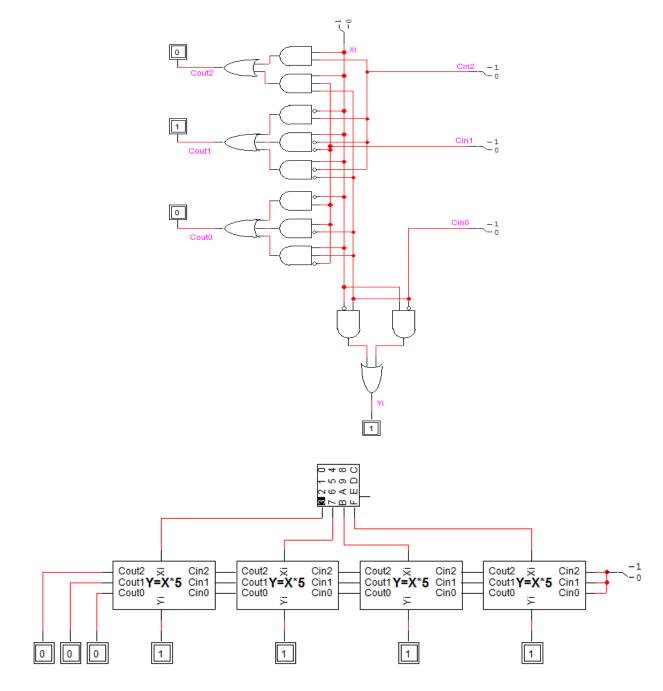

(iv)

(v) To simplify the analysis, I add an inverter delay to any gate that has one of the inputs inverted. A very quick analysis by computing the longest delay across one cell, one can deduce that the longest delay across a cell is 7. Thus, having 4 cells the worst case delay is estimated to be 4\*7=28.

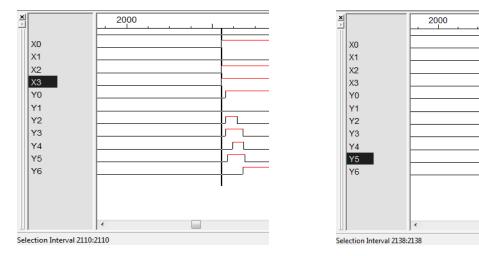

(vi) To verify our analysis we changed X from 0 to 13 and computed the difference from the time X has changed (=2110) to the time when Y3 has changed (=2138) giving a total delay =2138-2110=28.