# **COMPUTER ENGINEERING DEPARTMENT**

## **COE 405**

## **DESIGN & MODELING OF DIGITAL SYSTEMS**

## **Midterm Exam**

Second Semester (152)

## Time: 7:30-10:00 PM

Student Name : KEY

Student ID. :\_\_\_\_\_

| Question | Max Points | Score |

|----------|------------|-------|

| Q1       | 12         |       |

| Q2       | 12         |       |

| Q3       | 8          |       |

| Q4       | 8          |       |

| Q5       | 7          |       |

| Q6       | 18         |       |

| Q7       | 10         |       |

| Total    | 75         |       |

Dr. Aiman El-Maleh

(Q1) Consider the function:  $F(A, B, C, D) = ABCD + AB\overline{CD} + \overline{ABCD} + \overline{ABCD}$

(i) Compute the expansion of *F* using the **Orthonormal Basis** { $\varnothing_1 = AB$ ,  $\varnothing_2 = \overline{AB}$ ,  $\varnothing_3 = A\overline{B}$ ,  $\varnothing_4 = AB$  }.

F = A'B' (C'D+CD') + A'B (0) + AB' (0) + AB (CD+C'D')

(ii) Compute the function  $\overline{F}$  utilizing the orthonormal based expansion of the function.

F' = A'B' (C'D'+CD) + A'B (1) + AB' (1) + AB (C'D+CD')

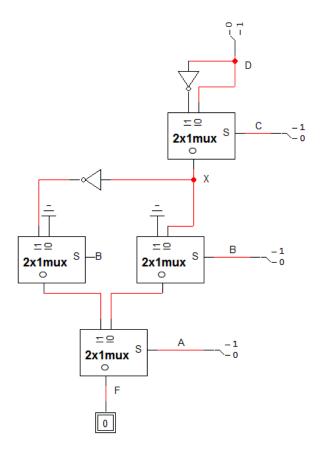

(iii) Implement the function F using <u>minimal</u> number of 2x1 MUXs and inverters.

$$\begin{split} F &= A' \left[ B' \left[ C'D + CD' \right] + B[0] \right] + A[B'[0] + B[CD + C'D'] \right] \\ Let X &= C'D + CD' = C'[D] + C[D'] \\ F &= A' \left[ B' \left[ X \right] + B[0] \right] + A[B'[0] + B[X']] \end{split}$$

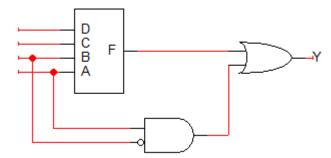

(iv) Suppose that the function F is part of a circuit whose output is Y as shown below. Simplify the equation of F into a minimal sum-of-products representation.

We have in the example AB' as don't care condition. We simplify F using the don't care condition as follows:

|    | 00          | 01   | 11          | 10          |

|----|-------------|------|-------------|-------------|

| 00 | 0 0         | 1 1  | 03          | 1 2         |

| 01 | 04          | 05   | 0 7         | 06          |

| 11 | <b>1</b> 12 | 0 13 | <b>1</b> 15 | 0 14        |

| 10 | ? 8         | ? 9  | ?11         | <b>?</b> 10 |

F = B'C'D + B'CD' + ACD + AC'D'

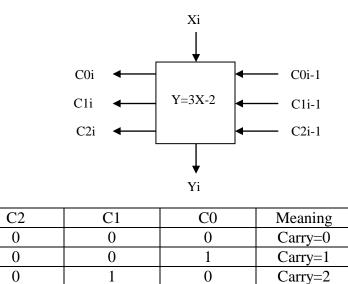

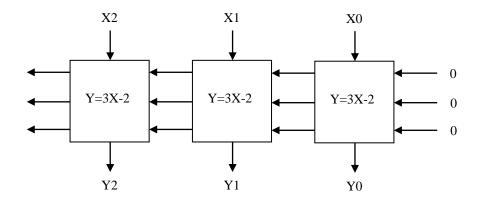

(Q2) It is required to design an <u>iterative</u> combinational circuit that receives an **n-bit** signed 2's complement number X and computes the equation Y=3\*X-2. The design should be based on a one-bit cell (i.e. processing one bit  $X_i$ ) that can be copied n times to construct the n-bit design.

(i) Determine the inputs and outputs for a one-bit cell. Clearly explain the meaning of signal values for the interface signals between the cells.

We will model Y=3X-2 as Y=3X+(-1)+)(-1). Since -1 in 2's complement is 111...111, this implies adding 2 for every bit. Thus, we need to represent carry outs from 0 to 4. Thus, we need 3 signals to represent the carry outs in the interface between cells. The mean of the signal values is illustrated below:

1

0

Carry=3

Carry=4

(ii) Derive the truth table for a one-bit cell.

1

0

0

1

| C2 <sub>i-1</sub> | C1 <sub>i-1</sub> | C0 <sub>i-1</sub> | Xi | C2 <sub>i</sub> | C1 <sub>i</sub> | C0 <sub>i</sub> | Yi |

|-------------------|-------------------|-------------------|----|-----------------|-----------------|-----------------|----|

| 0                 | 0                 | 0                 | 0  | 0               | 0               | 1               | 0  |

| 0                 | 0                 | 0                 | 1  | 0               | 1               | 0               | 1  |

| 0                 | 0                 | 1                 | 0  | 0               | 0               | 1               | 1  |

| 0                 | 0                 | 1                 | 1  | 0               | 1               | 1               | 0  |

| 0                 | 1                 | 0                 | 0  | 0               | 1               | 0               | 0  |

| 0                 | 1                 | 0                 | 1  | 0               | 1               | 1               | 1  |

| 0                 | 1                 | 1                 | 0  | 0               | 1               | 0               | 1  |

| 0                 | 1                 | 1                 | 1  | 1               | 0               | 0               | 0  |

| 1                 | 0                 | 0                 | 0  | 0               | 1               | 1               | 0  |

| 1                 | 0                 | 0                 | 1  | 1               | 0               | 0               | 1  |

| 1                 | 0                 | 1                 | 0  | X               | X               | Х               | Х  |

| 1                 | 0                 | 1                 | 1  | X               | X               | Х               | Х  |

| 1                 | 1                 | 0                 | 0  | X               | X               | Х               | Х  |

| 1                 | 1                 | 0                 | 1  | X               | X               | Х               | Х  |

| 1                 | 1                 | 1                 | 0  | X               | X               | Х               | Х  |

| 1                 | 1                 | 1                 | 1  | Х               | Х               | Х               | Х  |

(iii) Show the block diagram for a 3-bit design.

| Present State | Next  | t State, Z |

|---------------|-------|------------|

|               | X=0   | X=1        |

| SO            | S1, 0 | S2, 0      |

| S1            | S4, 0 | S3, 0      |

| S2            | S2, 0 | S5, 1      |

| S3            | S3, 0 | S2, 1      |

| S4            | S0, 0 | S5, 0      |

| S5            | S3, 0 | S5, 1      |

(Q3) Consider the given FSM that has 6 states, one input (X) and one output (Z), represented by the following state table:

#### (i) Determine the equivalent states.

| <b>S</b> 1 | (1,4), (2,3) |              |            |       |    |

|------------|--------------|--------------|------------|-------|----|

| S2         | $\backslash$ | $\searrow$   |            | _     |    |

| <b>S</b> 3 | $\backslash$ | $\searrow$   | (2,5)      |       | _  |

| S4         | (0,1), (2,5) | (0,4), (3,5) |            |       |    |

| S5         | $\backslash$ |              | (2,3)      | (2,5) |    |

|            | <b>S</b> 0   | S1           | <u>S</u> 2 | S3    | S4 |

Equivalent state pairs: (S0,S1), (S0, S4), (S1, S4), (S2, S3), (S2,S5), (S3, S5) Thus, equivalent states are: (S0, S1, S4) and (S2, S3, S5)

(ii) Reduce the state table into the minimum number of states and show the reduced state table.

#### Reduced State Table:

We will rename the equivalent states (S0, S1, S4) as S0' and the equivalent states (S2, S3, S5) as S1'.

| Present State | Next   | t State, Z |

|---------------|--------|------------|

|               | X=0    | X=1        |

| S0'           | S0', 0 | S1', 0     |

| S1'           | S1', 0 | S1', 1     |

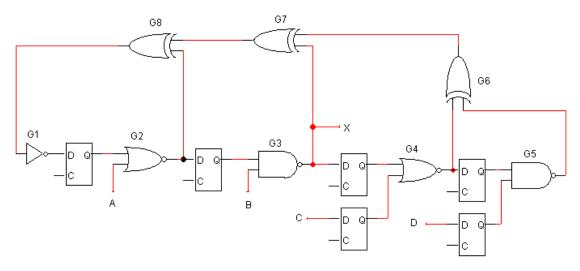

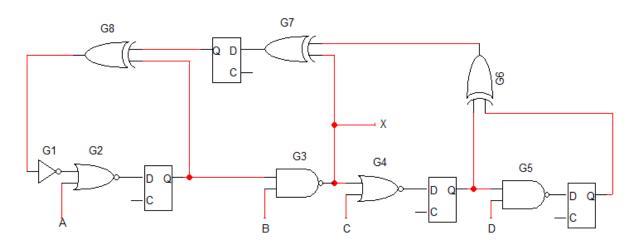

(Q4) Consider the sequential circuit given below having 4 inputs  $\{A, B, C, D\}$  and one output  $\{X\}$ . Assume that the delay of an inverter is 1 unit delay, the delay of a 2-input NAND gate is 2 unit delays, the delay of a 2-input NOR gate is 2 unit delays and the delay of a 2-input XOR gate is 3 unit delays.

(i) Determine the critical path of this circuit and the maximum propagation delay.

The maximum propagation delay is 12 and there are two critical paths as follows: {G5, G6, G7, G8, G1}, {G4, G6, G7, G8, G1},

(ii) Using only the **Retiming** transformation, <u>minimize</u> the critical path of this circuit with the minimum number of flip-flops possible. Determine the maximum propagation delay after retiming.

We can apply the following retiming transformations to reduce the critical path:

- Retime G5 by -1 (forward retiming)

- Retime G4 by -1 (forward retiming)

- Retime G1 by +1 (backward retiming)

- Retime G8 by +1 (backward retiming)

- Retime the stem on fanout of G2 by +1 (backward retiming)

Page 8 of 13

The resulting retiming circuit is as follows which has a maximum propagation delay of 6 with only 4 FFs.

[7 Points]

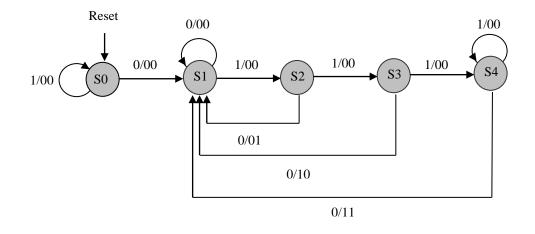

(Q5) It is required to design a synchronous sequential circuit that receives a stream of data serially through input **X** and produces output values through the two outputs Z1Z0. The circuit produces an output value of 01 if it receives a 0-1-0 pulse of one cycle length, produces an output value of 10 if it receives a 0-1-0 pulse of two cycles length and produces and output value of 11 if it receives a 0-1-0 pulse of length of three cycles or more. Otherwise, the circuit produces an output value of 00. Assume the existence of an asynchronous reset input to reset the machine to a reset state. Draw the state diagram of the circuit assuming a <u>Mealy</u> model with <u>minimum</u> number of states. *You are not required to derive the equations and the circuit*. The following is an example of input and output stream:

#### Example:

| Input  | X         | 100101100111100 |

|--------|-----------|-----------------|

| Output | ZO        | 000010000000010 |

| 1      | <b>Z1</b> | 0000001000010   |

#### State Diagram:

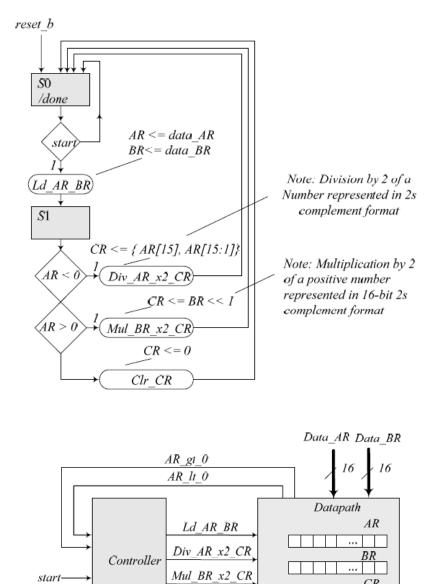

(Q6) The ASMD chart and the block diagram given below show the datapath and controller for a machine that transfers two 4-bit signed numbers in 2's complement representation into registers AR and BR, divides the number in AR by 2 and transfers the result to register CR if the number in AR is negative, multiplies the number in BR by 2 and transfers the result to register CR if the number in AR is positive but non-zero, and if the number in AR is zero, clears register CR to 0.

$Clr_CR$

...

16

CR

done

1

reset\_b

clock

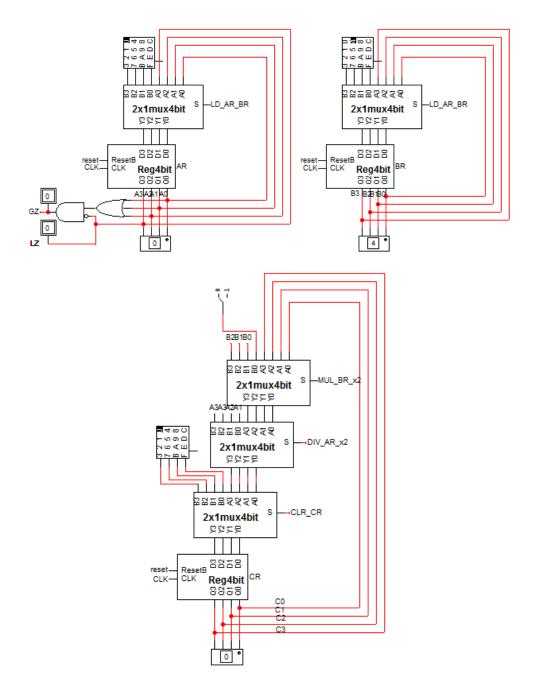

(i) Show the design of the data-path unit.

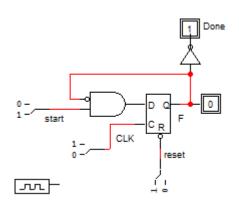

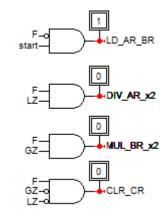

(ii) Show the design of the control unit using the following state assignment: S0=0, S1 = 1.

| C.S.       |       | Input         |               | N.S.       | Output |          |           |           |        |

|------------|-------|---------------|---------------|------------|--------|----------|-----------|-----------|--------|

|            | start | $GZ(AR_gt_0)$ | $LZ(AR_lt_0)$ |            | Done   | LD_AR_BR | Div_AR_x2 | Mul_AR_x2 | Clr_CR |

| <b>S</b> 0 | 0     | Х             | Х             | <b>S</b> 0 | 1      | 0        | 0         | 0         | 0      |

| <b>S</b> 0 | 1     | Х             | Х             | S1         | 1      | 1        | 0         | 0         | 0      |

| S1         | х     | Х             | 1             | <b>S</b> 0 | 0      | 0        | 1         | 0         | 0      |

| <b>S</b> 1 | х     | 1             | 0             | <b>S</b> 0 | 0      | 0        | 0         | 1         | 0      |

| S1         | х     | 0             | 0             | S0         | 0      | 0        | 0         | 0         | 1      |

#### Control Unit:

We assume the state assignment S0=0 and S1=1.

|               | 00   | 01   | 11   | 10   |  |  |

|---------------|------|------|------|------|--|--|

| 00            | 0 0  | 0 1  | ? 3  | 02   |  |  |

| 01            | 14   | 15   | ? 7  | 16   |  |  |

| 11            | 0 12 | 0 13 | ? 15 | 0 14 |  |  |

| 10            | 08   | 09   | ?11  | 0 10 |  |  |

| F+ = F' Start |      |      |      |      |  |  |

Done = F'LD\_AR\_BR = F' Start

|     | 00         | 01          | 11          | 10          |

|-----|------------|-------------|-------------|-------------|

| 00  | <b>0</b> 0 | 0 1         | ? 3         | 02          |

| 01  | 04         | 05          | ? 7         | 06          |

| 11  | 0 12       | <b>1</b> 13 | <b>?</b> 15 | 0 14        |

| 10  | 08         | 19          | ?11         | <b>0</b> 10 |

| DIV | _AR_       | _x2 =       | F LT        |             |

|     | 00         | 01    | 11   | 10          |

|-----|------------|-------|------|-------------|

| 00  | <b>0</b> 0 | 0 1   | ? 3  | 02          |

| 01  | 04         | 05    | ? 7  | 06          |

| 11  | 0 12       | 0 13  | ? 15 | <b>1</b> 14 |

| 10  | 08         | 09    | ?11  | <b>1</b> 10 |

| MUI | L_BR       | _x2 = | FG   | Г           |

|     | 00                   | 01   | 11   | 10   |  |  |  |

|-----|----------------------|------|------|------|--|--|--|

| 00  | <b>0</b> 0           | 0 1  | ? 3  | 0 2  |  |  |  |

| 01  | 04                   | 05   | ? 7  | 0 6  |  |  |  |

| 11  | <b>1</b> 12          | 0 13 | ? 15 | 0 14 |  |  |  |

| 10  | 1 8                  | 09   | ?11  | 0 10 |  |  |  |

| CLR | $CLR_CR = F GT' LT'$ |      |      |      |  |  |  |

#### [10 Points]

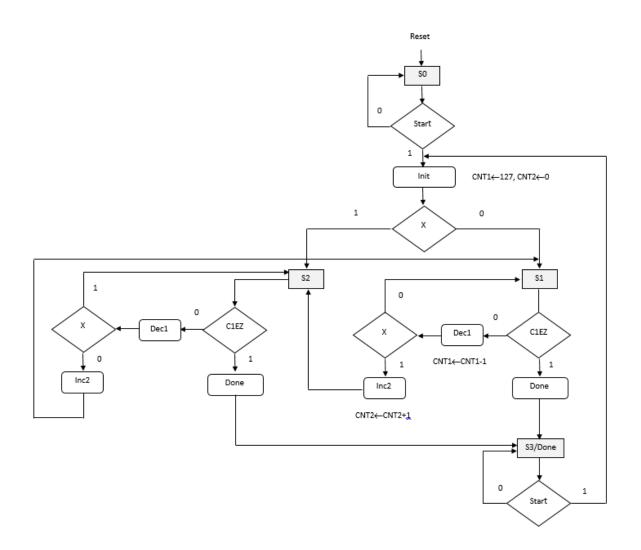

(Q7) It is required to design a circuit that counts the number of data transitions (i.e.  $0 \rightarrow 1$  and  $1 \rightarrow 0$  data changes) through a stream of 128 bit data. The data is applied serially through an input X once the user presses a *Start* button, where the first bit is transmitted in the same cycle the *Start* button is asserted. Once the computation is finsihed the machine asserts a *Done* signal which remains asserted until the user presses the Start button again or resets the machine. Assume that the machine has Asynchronous *Reset* input. Show the ASMD chart for this machine.