# COE 405, Term 162

# **Design & Modeling of Digital Systems**

# Assignment# 5 Solution

#### Due date: Saturday, May 13

# **Q.1.** Consider the following function:

*X*=*A*C+*B*C+*A*D+*B*D+*A*'*B*'C'+*A*'*B*'D'+*A*EF+*B*EF+*A*E'F'+*B*E'F'+*A*'*B*'EF'+ *A*'*B*'E'F

- (i) Compute all double-cube divisors of X along with their bases and their weights. Show only double-cube divisors that have non-empty bases.

- (1) Double Cube Divisors

| Double - Cube divisor | Base         | weight                           |

|-----------------------|--------------|----------------------------------|

| A+B                   | C, D, EF, EF | 4x2-4-2+6+4=12                   |

|                       | AJB          | $2 \times 2 - 2 - 2 + 2 + 0 = 2$ |

| C+ D                  | A > B        | 2×3-2-3+2 = 3                    |

| C + EF                | AJG          | 2×3-2-3+2=3                      |

| C +EF                 |              | 2×3-2-3+2=3                      |

| D+ EF                 | A, B         | 2 × 3 -2 -3+2=3                  |

| D+EF                  | A,B          | 1×2-1-2+2+0=1                    |

|                       | 7A B         |                                  |

| ē+0                   | 2 A          | 1×3-1-3+2=1                      |

| ε+εf                  | AB           | 1×3-1-3+2=1                      |

| 2 + EF                | ĀB           | 1×3-1-3+2=1                      |

| D + EF                | # B          | 1x3-1-3+2=1                      |

| D +EF                 | ĀB           |                                  |

| EF + EF               | A, B         | 3×4-3-4+4 =9                     |

| AF + ABF              | E            | 1 × 5 -1 -5 +1 = 0               |

|                       | F            | L×5 −1-5+1=0                     |

| AE + ABE              | E            | 1 × 5 -1 -6+1=0                  |

| BF + ABF<br>BE + ABF  | F            | 1×5~1-5+150                      |

|                       | F            | 1×5-1-5+1=0                      |

| AE + ABE              | Ē            | 1 ×5 -1-5+1=0                    |

| AF + ABF              | F            | 1×5-1-5+1=0                      |

| BE + ABE              | Ē            | 1×5-1-5+1=0                      |

| BF + ABF              |              | 3 × 4 - 3 - 4 + 4 = 9            |

| EF + EF               | ĀB           |                                  |

(ii) Apply the fast extraction algorithm based on extracting double-cube divisors along with complements or single-cube divisors with two-literals. Show all steps of the algorithm. Determine the number of literals saved. Compare your solution with the result obtained by running the sis commands fx.

SIS has resulted in the same extracted network as shown below:

sis> read\_eqn hw5q1.eqn sis> print  ${X} = A C + A D + A E F + A E' F' + A' B' C' + A' B' D' + A' B' E F' + A' B'$ 'E' F + B C + B D + B E F + B E' F' $sis> print_stats$ hw5q1.eqn pi= 6 po= 1 node= 1 latch= 0 lits(sop)= 34 lits(ff)= 16sis> fxsis> print $<math>{X} = C [1] + C' [1]' + D [1] + D' [1]' + [1] [2] + [1]' [2]'$  [1] = A + B [2] = E F + E' F'sis> print\_stats hw5q1.eqn pi= 6 po= 1 node= 3 latch= 0 lits(sop)= 18 lits(ff)= 14 sis>

Q.2. Consider the logic network defined by the following expressions:

```

e=a b d

f=c d

g = e + f

h = a d

i = a' b' d'

j = h + i

k= b d

l = j + k

x = g + l

```

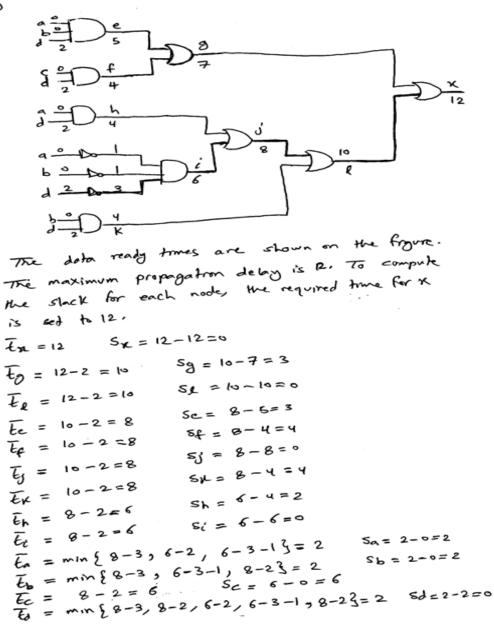

Inputs are  $\{a, b, c, d\}$  and output is  $\{x\}$ . Assume that the delay of a gate is related to the number of its inputs. Also, assume that the input data-ready times are zero except for input d, which is equal to 2.

(i) Draw the logic network graph and compute the data ready times and slacks for all vertices in the network.

(ii) Determine the maximum propagation delay and the topological critical path.

(1)

(iii) Suggest an implementation of the function x to reduce the delay of the circuit. What is the **maximum propagation delay** after the modified implementation?

(iii)

$$X = g + l = e + f + j + k$$

= abd + cd + ad +  $\overline{a}\overline{b}\overline{d}$  + bd

= d [ab + c+ a + b] +  $\overline{a}\overline{b}\overline{d}$

= d [a + b+c] +  $\overline{a}\overline{b}\overline{d}$

Thus, to improve the delay of X, we

can implement it as follows:

$\frac{1}{2} + \frac{1}{2} + \frac{1$

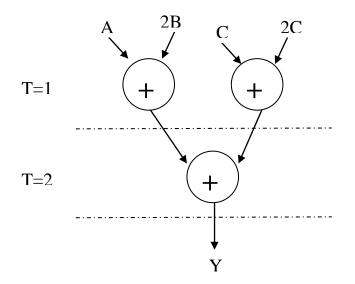

- **Q.3.** It is required to design a circuit to compute the equation Y=A+2\*B+3\*C, where A, B, and C are N-bit inputs representing signed numbers in 2's complement representation. Assume that inputs are available only during the first cycle when a **START** input is asserted. Assume that a **DONE** signal will be set when the result is ready and the result will remain held until the next Start operation.

- (i) Show a schedule of the operations with minimum latency (i.e., clock cycles) assuming that the clock cycle is limited by the time for performing one addition operation. Store the output Y in a register.

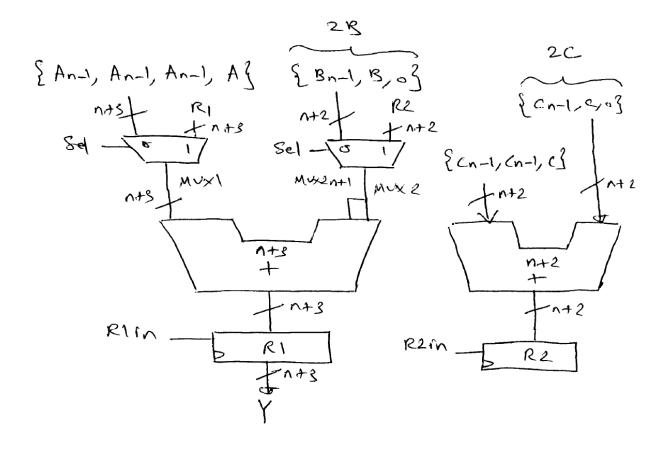

(ii) Show the Data Path design of your circuit indicating all the control signals and the used adder sizes.

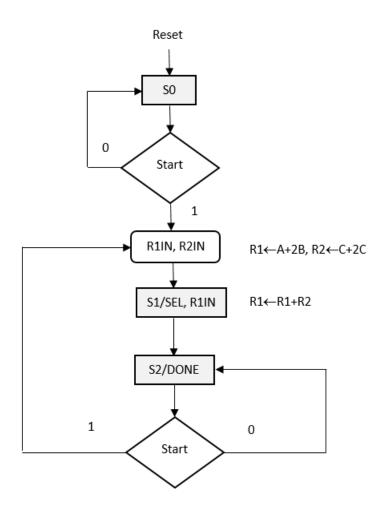

(iii) Show the ASMD diagram of your control unit.

(iv) Write the necessary Verilog modules to module the data path unit, control unit and the overall circuit.

module HW5 #(parameter N=4) (output [N+2:0] Y, output DONE, input [N-1:0] A, B, C, input START, RESET, CLK);

HW5 DPU #(N) M1 ( Y, A, B, C, SEL, R1IN, R2IN, CLK);

HW5 CU M2 (SEL, R1IN, R2IN, DONE, START, RESET, CLK);

endmodule

module HW5\_DPU #(parameter N=4) (output [N+2:0] Y, input [N-1:0] A, B, C, input SEL, R1IN, R2IN, CLK);

reg [N+2:0] R1;

```

reg [N+1:0] R2;

wire [N+2:0] MUX1;

wire [N+1:0] MUX2;

assign MUX1 = SEL? R1 : {A[N-1], A[N-1], A[N-1], A};

assign MUX2 = SEL? R2 : {B[N-1], B, 1'b0};

assign Y = R1;

always @(posedge CLK) begin

if (R1IN)

R1 = MUX1 + \{MUX2[N+1], MUX2\};

if (R2IN)

R2 = \{C[N-1], C[N-1], C\} + \{C[N-1], C, 1'b0\};

end

endmodule;

module HW5 CU (output reg SEL, R1IN, R2IN, DONE, input START,

RESET, CLK);

parameter S0 = 2'b00, S1=2'b01, S2=2'b10;

reg [1:0] state, next state;

always @(posedge CLK, posedge RESET)

if (RESET) state <= S0;

else state <= next state;</pre>

always @(state, START) begin

SEL=0; R1IN=0; R2IN=0; DONE=0;

case (state)

S0:

if (START) begin

next state=S1; R1IN=1; R2IN=1; end

else next state=S0;

S1: begin SEL=1; R1IN=1; next_state=S2; end

S2: begin DONE=1;

if (START) begin

next state=S1; R1IN=1; R2IN=1; end

else next state=S2;

end

default: begin

next state=1'bx;

SEL=1'bx; R1IN=1'bx; R2IN=1'bx; DONE=1'bx;

end

endcase

end

endmodule

```

(v) Write a test bench to test the correct operation of your circuit. Include simulation snapshots.

```

module HW5 Test();

wire [6:0] Y;

wire DONE;

reg [3:0] A, B, C;

req START, RESET, CLK;

HW5 #(4) M1 (Y, DONE, A, B, C, START, RESET, CLK);

initial begin

CLK = 0;

forever

#50 \text{ CLK} = \sim \text{ CLK};

end

initial begin

RESET=1;

#100 RESET=0; START=1; A=7; B=7; C=7;

#100 START=0;

#100 ;

#100 START=1; A=-8; B=-8; C=-8;

#100 START=0;

#100 ;

#100 START=1; A=3; B=-4; C=5;

#100 START=0;

end

```

endmodule

| 🔁 🕶               | Msgs |                           |

|-------------------|------|---------------------------|

| /HW5_Test/CLK     | 0    |                           |

| 💠 /HW5_Test/RESET | 0    |                           |

| 🔶 /HW5_Test/START | 0    |                           |

| ▪ /HW5_Test/A     | 3    | 7 -8 3                    |

| ▪ /HW5_Test/B     | -4   | 7 -8 -4                   |

| ▪ /HW5_Test/C     | 5    | 7 -8 5                    |

| ▪ /HW5_Test/Y     | 10   | {21 ,42 ,-24 ,-48 ,-5 ,10 |

| /HW5_Test/DONE    | St1  |                           |

(vi) Implement your circuit on FPGA assuming N=2 bits. Include a link for a video snapshot to demonstrate correct functionality of your circuit.