## COE 405, Term 162

## **Design & Modeling of Digital Systems**

## Assignment# 1 Solution

## Due date: Saturday, March 4

- **Q.1.** Consider the two functions  $f=(a \oplus b) + (a \oplus c)$  and g=a b + a' c + b' c'.

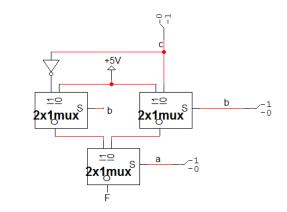

- (i) Implement the function f using only 2x1 MUXs and inverters minimizing the number of MUXs used.

$$f = a' (b + c) + a (b' + c')$$

= a' (b' (c) + b (1)) + a (b' (1) + b (c'))

(ii) Compute the function  $f \oplus g$  based on orthonormal basis expansion.

$$\begin{split} f &= a' b' (c) + a' b (1) + a b' (1) + a b (c') \\ g &= a' (b' + c) + a (b + c') \\ &= a' (b' (1) + b (c)) + a (b' (c') + b (1)) \\ &= a' b' (1) + a' b (c) + a b' (c') + a b (1) \\ f \oplus g &= a' b' (c \oplus 1) + a' b (1 \oplus c) + a b' (1 \oplus c') + a b (c' \oplus 1) \\ &= a' b' (c') + a' b (c') + a b' (c) + a b (c) \\ &= a' c' + a c \end{split}$$

- **Q.2.** It is required to design an iterative combinational circuit that computes the equation Z=3\*X-3, where X is an n-bit unsigned number.

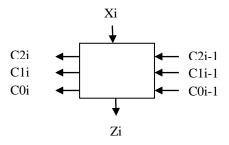

- (i) Determine the number of inputs and outputs needed for your 1-bit cell. Explain the meaning of values in the interface signals.

This circuit can be designed by assuming that we have a borrow of 3 feeding the first cell or by representing -3 as -1+-1+-1 where -1 is represented in 2's complement as 11...111 and thus adding 3 to each cell. I will follow the second approach. We need to represent carry-out values in the range 0 to 5. Thus, we need three signals to represent Carry out values propagation across cells.

(ii) Derive the truth table of your 1-bit cell.

| C1 <sub>i-2</sub> | C1 <sub>i-1</sub> | C0 <sub>i-1</sub> | Xi | C2 <sub>i</sub> | C1 <sub>i</sub> | C0 <sub>i</sub> | Zi |

|-------------------|-------------------|-------------------|----|-----------------|-----------------|-----------------|----|

| 0                 | 0                 | 0                 | 0  | 0               | 0               | 1               | 1  |

| 0                 | 0                 | 0                 | 1  | 0               | 1               | 1               | 0  |

| 0                 | 0                 | 1                 | 0  | 0               | 1               | 0               | 0  |

| 0                 | 0                 | 1                 | 1  | 0               | 1               | 1               | 1  |

| 0                 | 1                 | 0                 | 0  | 0               | 1               | 0               | 1  |

| 0                 | 1                 | 0                 | 1  | 1               | 0               | 0               | 0  |

| 0                 | 1                 | 1                 | 0  | 0               | 1               | 1               | 0  |

| 0                 | 1                 | 1                 | 1  | 1               | 0               | 0               | 1  |

| 1                 | 0                 | 0                 | 0  | 0               | 1               | 1               | 1  |

| 1                 | 0                 | 0                 | 1  | 1               | 0               | 1               | 0  |

| 1                 | 0                 | 1                 | 0  | 1               | 0               | 0               | 0  |

| 1                 | 0                 | 1                 | 1  | 1               | 0               | 1               | 1  |

| 1                 | 1                 | 0                 | 0  | Χ               | Χ               | Χ               | Χ  |

| 1                 | 1                 | 0                 | 1  | Χ               | Χ               | Χ               | Χ  |

| 1                 | 1                 | 1                 | 0  | Χ               | Χ               | Χ               | Χ  |

| 1                 | 1                 | 1                 | 1  | Χ               | Χ               | Χ               | Χ  |

(iii) Derive minimized equations for your 1-bit using K-Map method.

|    | 00          | 01          | 11          | 10          |  |

|----|-------------|-------------|-------------|-------------|--|

| 00 | 10          | 0 1         | 13          | 02          |  |

| 01 | 14          | 05          | <b>1</b> 7  | 06          |  |

| 11 | <b>?</b> 12 | <b>?</b> 13 | <b>?</b> 15 | <b>?</b> 14 |  |

| 10 | 18          | 09          | <b>1</b> 11 | <b>0</b> 10 |  |

$Zi = C0i-1' Xi' + C0i-1 Xi = (C0i-1 \oplus Xi)'$

|    | 00          | 01          | 11          | 10          |  |

|----|-------------|-------------|-------------|-------------|--|

| 00 | 10          | 11          | 13          | 02          |  |

| 01 | 04          | 05          | 07          | <b>1</b> 6  |  |

| 11 | <b>?</b> 12 | <b>?</b> 13 | <b>?</b> 15 | <b>?</b> 14 |  |

| 10 | 18          | 19          | <b>1</b> 11 | <b>0</b> 10 |  |

$\begin{array}{l} \text{C0i} = \text{C1i-1'} \ \text{C0i-1'} + \text{C1i-1'} \ \text{Xi} + \text{C1i-1} \ \text{C0i-1} \ \text{Xi'} \\ = \text{C1i-1'} \ (\text{C0i-1'} + \text{Xi}) + \text{C1i-1} \ \text{C0i-1} \ \text{Xi'} \\ = \text{C1i-1} \oplus (\text{C0i-1'} + \text{Xi}) \end{array}$

|    | 00          | 01          | 11          | 10          |  |

|----|-------------|-------------|-------------|-------------|--|

| 00 | 00          | 11          | 13          | 12          |  |

| 01 | 14          | 05          | 07          | 16          |  |

| 11 | <b>?</b> 12 | <b>?</b> 13 | <b>?</b> 15 | <b>?</b> 14 |  |

| 10 | 18          | 09          | <b>0</b> 11 | <b>0</b> 10 |  |

$\begin{array}{l} C1i = C1i\text{-}1 \,\, Xi' + C2i\text{-}1' \,\, C1i\text{-}1' \,\, Xi + C2i\text{-}1' \,\, C0i\text{-}1 \,\, Xi' + C2i\text{-}1 \,\, C0i\text{-}1' \,\, Xi' \\ = C1i\text{-}1 \,\, Xi' + C2i\text{-}1' \,\, C1i\text{-}1' \,\, Xi + Xi' \,\, (C2i\text{-}1 \oplus C0i\text{-}1) \end{array}$

|    | 00          | 01          | 11          | 10          |  |

|----|-------------|-------------|-------------|-------------|--|

| 00 | 00          | 01          | <b>0</b> 3  | 02          |  |

| 01 | 04          | 15          | 17          | <b>0</b> 6  |  |

| 11 | <b>?</b> 12 | <b>?</b> 13 | <b>?</b> 15 | <b>?</b> 14 |  |

| 10 | 08          | 19          | <b>1</b> 11 | <b>1</b> 10 |  |

C2i = C1i-1 Xi + C2i-1 Xi + C2i-1 C0i-1

(iv) Write a Verilog model for modeling your 1-bit cell by using an assign statement for each output.

module OneCell (output C2i, C1i, C0i, Zi, input C2i\_1, C1i\_1, C0i\_1, Xi);

assign  $Zi = C0i_1 \sim^{\Lambda} Xi;$

assign C0i = C1i\_1 ^ (~C0i\_1 | Xi);

assign C1i = C1i\_1 & ~Xi | ~C2i\_1 & ~C1i\_1 & Xi | ~Xi & (C2i\_1 ^ C0i\_1);

assign C2i = C1i\_1 & Xi | C2i\_1 & Xi | C2i\_1 & C0i\_1;

endmodule

(v) Write a Verilog model for modeling a 4-bit circuit based on the 1-bit model you have.

module D3XM3 (output C2, C1, C0, output [3:0] Z, input [3:0] X);

OneCell M1 (C2\_0, C1\_0, C0\_0, Z[0],0, 0, 0, X[0]); OneCell M2 (C2\_1, C1\_1, C0\_1, Z[1],C2\_0, C1\_0, C0\_0, X[1]); OneCell M3 (C2\_2, C1\_2, C0\_2, Z[2],C2\_1, C1\_1, C0\_1, X[2]); OneCell M4 (C2, C1, C0, Z[3],C2\_2, C1\_2, C0\_2, X[3]);

endmodule

(vi) Write a Verilog test bench to test the correctness of your design for the following input values: {X=1}, {X=3}, {X=5} and {X=4}.

module D3XM3\_Test();

reg [3:0] X; wire C2, C1, C0; wire [3:0] Z;

D3XM3 M1 (C2, C1, C0, Z, X);

initial begin

X=4'b0001;

#100 X=4'b0011;

#100 X=4'b0101;

#100 X=4'b0100;

end

endmodule

The generated simulation waveform verifies the correct functionality of the designed circuit:

| P-√  /D3XM3_Test/Z  -No  0000  0110  1100  1001    ✓  /D3XM3_Test/C2  -No | 🖃 🔶 /D3XM3_Test/X | -No | (0001 | 0011 | 0101 | 0100 |  |

|---------------------------------------------------------------------------|-------------------|-----|-------|------|------|------|--|

| ✓ /D3XM3_Test/C1                                                          |                   | -No | 0000  | 0110 | 1100 | 1001 |  |

|                                                                           | /D3XM3_Test/C2    | -No | L     |      |      |      |  |

|                                                                           | /D3XM3_Test/C1    | -No |       |      |      |      |  |

| VD3XM3_Test/C0 -No                                                        | /D3XM3_Test/C0    | -No |       |      |      |      |  |