Name: Id#

## COE 202, Term 141 Digital Logic Design

## Quiz# 6

Date: Thursday, Dec. 25

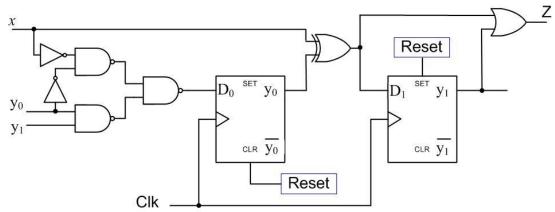

**Q1** The sequential circuit shown below has a single output Z, an input x together with a Reset input to initialize the circuit. Note that the used D-FFs have direct/asynchronous Clear and Set inputs (shown in the figure as CLR and SET).

- a. Is the circuit type Mealy or Moore? Why? (2 point)

- b. Derive expressions for the  $D_0$  and  $D_1$  flip flop inputs and the external output Z. (3 points)

c. Derive the state transition table of the circuit. (4 points)

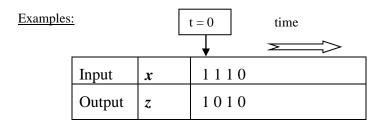

Q2 It is required to design a synchronous sequential circuit that receives a serial inputs  $\mathbf{x}$  and produces a serial output  $\mathbf{z}$  that computes the equation  $\mathbf{z}=\mathbf{x}-\mathbf{2}$ . Draw the state diagram of this circuit assuming a <u>Mealy</u> model. Assume the existence of an asynchronous reset input to reset the machine to a reset state. Two samples of input/output data are given below.

(<u>NOTE</u>: You are <u>only</u> required to draw the state diagram <u>Nothing MORE</u>)

(6 points)

| Examples: |        |   | t = 0        | time        |

|-----------|--------|---|--------------|-------------|

|           |        |   | <del>_</del> | <b>&gt;</b> |

|           | Input  | x | 0101         |             |

|           | Output | z | 0001         |             |