Name: KEY Id#

## COE 202, Term 131 Digital Logic Design

## Quiz#5

Date: Thursday, Nov. 28

## Q1. Fill in all blank cells in the two tables below. All binary representations use 7 bits

| Binary  | Eq       | Equivalent decimal value with the binary interpreted as: |                   |                   |  |  |  |

|---------|----------|----------------------------------------------------------|-------------------|-------------------|--|--|--|

|         | Unsigned | Signed-magnitude                                         | Signed-1's        | Signed-2's        |  |  |  |

|         | number   | number                                                   | complement number | complement number |  |  |  |

| 1011010 | 90       | -26                                                      | -37               | -38               |  |  |  |

|         | Binary representation in:    |                                |                                   |  |  |

|---------|------------------------------|--------------------------------|-----------------------------------|--|--|

| Decimal | Signed-magnitude<br>notation | Signed-1's complement notation | Signed-2's complement<br>notation |  |  |

| - 59    | 1111011                      | 1000100                        | 1000101                           |  |  |

Using 2's-complement signed arithmetic in 5 bits, perform the following operations in binary.

Show all your work. Verify that you get the expected decimal results.

## Check for overflow and mark clearly any occurrences of it.

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                          | 00101 +5<br>-10100 -12<br>+17 > +15 = overflow<br>overflow<br>expected<br>+ 01100<br>overflow<br>expected<br>: overflow |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| (iii)<br>+(-9)<br>-4 0 0 1 0 1 1 1<br>-4 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                   |

$$= -011000$$

$$= -24$$

$$= -24 - X = -33$$

$$= -24 + 33 = +9$$

$$= 001001$$

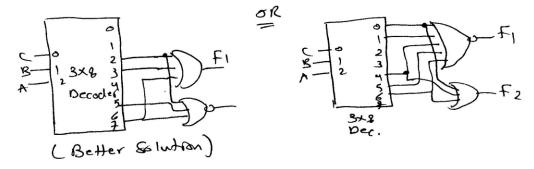

(a) You are given **one 3-to-8 decoder**, **one NOR** gate and **one OR** gate to implement the two functions given below.

$$F_{1}(A,B,C) = \prod M(0,1,4,5,6) F_{2}(A,B,C) = \sum m(0,4,6) + \sum d(1,3)$$

$$F_{1} = \sum m(2,3,7) F_{2} = \prod M(2,5,7)$$

Draw the circuit and properly <u>label</u> all input and output lines.

(b) Given the truth table below for a function with four inputs (A, B, C and D) and one output F, implement F using a 4-to-1 MUX (with 2 select lines) and additional logic. Show how you obtained your solution, and properly <u>label</u> all input and output lines. Apply A and B to the select inputs.

| A          | В   | С  | D  | F   |         |              |

|------------|-----|----|----|-----|---------|--------------|

| Ō          | 0   | 0  | 50 | 0   | 7 _     |              |

| 0          | 0   | 0  | 1  | 1   | } F=D   |              |

| 0          | 0   | 1  | 0  | 0   | \ '     |              |

| 0          | 0   | 1  |    | 1   | ٦       | 0 1          |

| 0          | 1   | 0  | 0  | 1   | γ.      | 1 8 / 1      |

| 0          | 1   | 0  | 1  | 1   | Y F21   |              |

| 0          | 1   | 1  | 0  | 1   | \ ,     | B = 3 2 1 0  |

| 0          | 1   | 1_ | 1  | 1   | )       |              |

| 1          | 0   | 0  | 0  |     | 7 -     | 11           |

| \ 1        | 0 \ | 0  | 1  | 1   | } F=C   | <del>_</del> |

| 1          | 0   | 1  | 0  | 0   | ( '     | F            |

| 1          | 0   | 1  | 1  | 0   | 7       |              |

| $\sqrt{1}$ | 1   | 0  | 0  | 0   | 7 5 5 5 |              |

| 1          | 1   | 0  | 1  | (0) | 7 F=0   |              |

| 1          | 1   | 1  | 0  | 0   |         |              |

| 1          | _1  | 1  | 1  | لها | J       |              |