Name: KEY Id#

## COE 202, Term 122 Digital Logic Design

## Quiz# 5

Date: Monday, April 29

**Q1**.

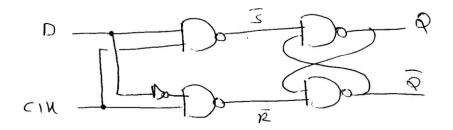

(i) Design a D-Latch using only NAND gates and inverters.

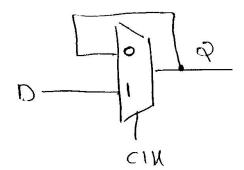

(ii) Design a D-Latch using only a 2x1 Multiplexer.

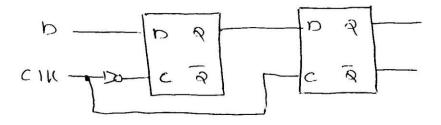

(iii) Design a **rising-edge** triggered D flip flop using only D-Latches and inverters.

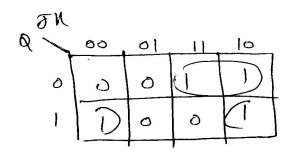

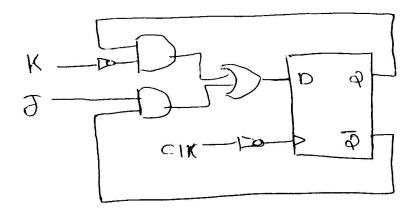

**Q2**. Design a <u>falling-edge</u> triggered JK flip flop using a <u>rising-edge</u> triggered D flip flop. Show the design steps.

| Q           | J        | K       | <b>₽</b> <sup>+</sup> | 0 |

|-------------|----------|---------|-----------------------|---|

| 0           | д        | 0       | 0                     | 0 |

| 0           | 0        | 1       | 0                     | ٥ |

| 0           | 1        | ð       |                       | l |

| 0           |          | 1       | 1                     | 1 |

|             | <u>ه</u> | ව       |                       | 1 |

| 1           | ව        |         | 0                     | Ò |

| 1           | 1        | <u></u> | 1                     | 1 |

| <del></del> |          | l       | 0                     | ٥ |

|             |          |         |                       |   |

## **Q3**.

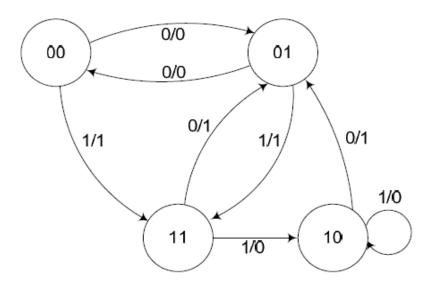

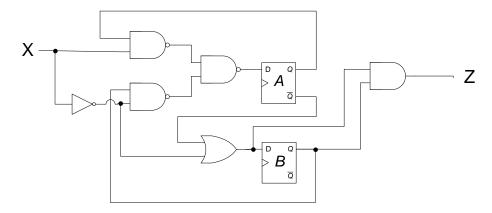

(i) Derive the state table and state diagram for the following circuit with a single input X, and a single output Z and determine whether the circuit is <u>Mealy</u> or <u>Moore</u>:

The circuit is Mealy since the output depends on both the current state and the input.

$$D_{A} = \overline{(\overline{XQ_{A}})(\overline{\overline{XQ_{B}}})} = XQ_{A} + \overline{X}Q_{B}$$

$$D_{B} = \overline{Q_{A}} + \overline{X}$$

$$Z = Q_{B}(\overline{Q_{A}} + \overline{X}) = \overline{Q_{A}}Q_{B} + \overline{X}Q_{B}$$

| $Q_A$ | $Q_B$ | X | $Q_A^+$ | $Q_B^+$ | Z |

|-------|-------|---|---------|---------|---|

| 0     | 0     | 0 | 0       | 1       | 0 |

| 0     | 0     | 1 | 0       | 1       | 0 |

| 0     | 1     | 0 | 1       | 1       | 1 |

| 0     | 1     | 1 | 0       | 1       | 1 |

| 1     | 0     | 0 | 0       | 1       | 0 |

| 1     | 0     | 1 | 1       | 0       | 0 |

| 1     | 1     | 0 | 1       | 1       | 1 |

| 1     | 1     | 1 | 1       | 0       | 0 |

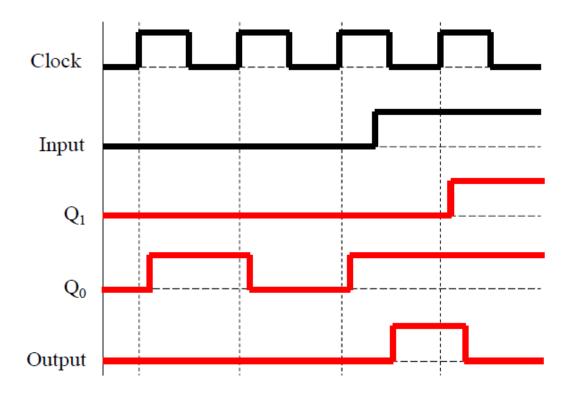

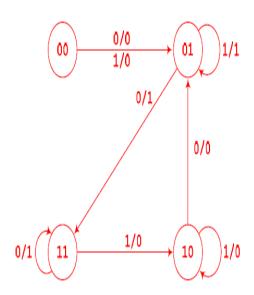

(ii) Complete the following waveform for the positive-edge triggered circuit that implements the state diagram provided below. Assume the circuit is initially at the state  $Q_1Q_0=00$ .