Name: KEY Id#

## COE 202, Term 112 Digital Logic Design

Quiz# 5

Date: Wednesday, April 25

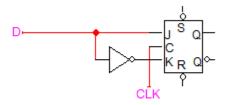

Q1. Design a rising edge-triggered D flip-flop using a rising edge-triggered JK flip flop.

## State Table:

| Current State (Q) | Input (D) | Next State (Q) | J | K |

|-------------------|-----------|----------------|---|---|

| 0                 | 0         | 0              | 0 | X |

| 0                 | 1         | 1              | 1 | X |

| 1                 | 0         | 0              | X | 1 |

| 1                 | 1         | 1              | X | 0 |

$$J=D$$

$K=D'$

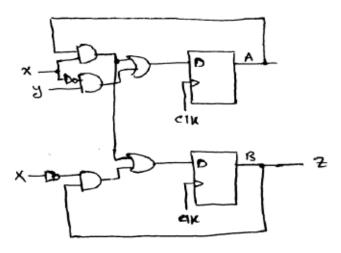

**Q2**. A sequential circuit with two D flip-flops A and B, two inputs X and Y, and one output Z is specified by the following equations:

$$D_A = X Y + X A \qquad \qquad D_B = X B + X A \qquad \qquad Z = B$$

(i) Draw the logic diagram of the circuit.

(ii) Derive the state table.

State Table:

| Current state | Next state |        |               |         | output |

|---------------|------------|--------|---------------|---------|--------|

|               | ×3=00      | ×৪≂ ৩I | ×y = 10<br>∧B | 11 = 6x | æ      |

| 00            | 0 0        | 10     | 00            | 00      |        |

| 0             | 0 1        | 11     | 0 0           | 00      | 1      |

| 10            | 00         | 10     |               | 11      | •      |

| 11            | 0 1        | 11     | 1.1           | l I     |        |

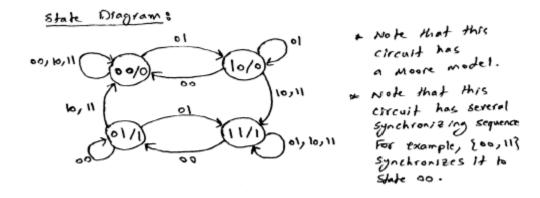

(iii) Derive the state diagram.