Name: KEY Id#

## COE 202, Term 102 Fundamentals of Computer Engineering

## **Quiz# 5 (Take Home)**

Due date: Saturday, May 7, 2011

Q.1. It is required to design a 4-bit arithmetic and logic unit that has two 4-bit inputs  $A=A_3A_2A_1A_0$  and  $B=B_3B_2B_1B_0$  and one <u>6-bit output</u>  $C=C_5C_4C_3C_2C_1C_0$ . The circuit implements the following functions based on the values of the four selection inputs S3, S2, S1 and S0.

| S3 S2 S1 S0 | Function         |

|-------------|------------------|

| 0 0 0 0     | C = A + B        |

| 0 0 0 1     | C = A - B        |

| 0 0 1 0     | C = A+1          |

| 0 0 1 1     | C = A-1          |

| 0 1 0 0     | C = A + 2        |

| 0 1 0 1     | C = A - 2        |

| 0 1 1 0     | C = B            |

| 0 1 1 1     | C = -B           |

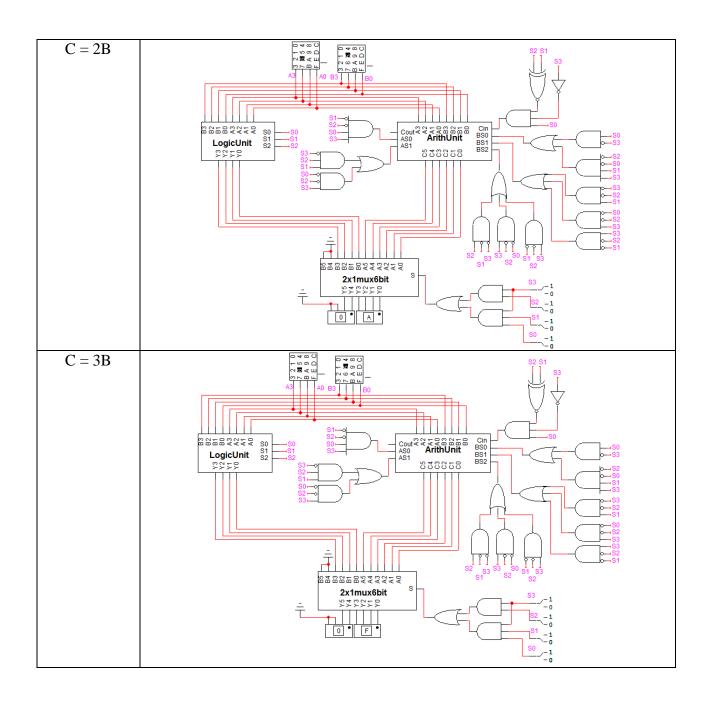

| 1 0 0 0     | C = 2B           |

| 1 0 0 1     | C = 3B           |

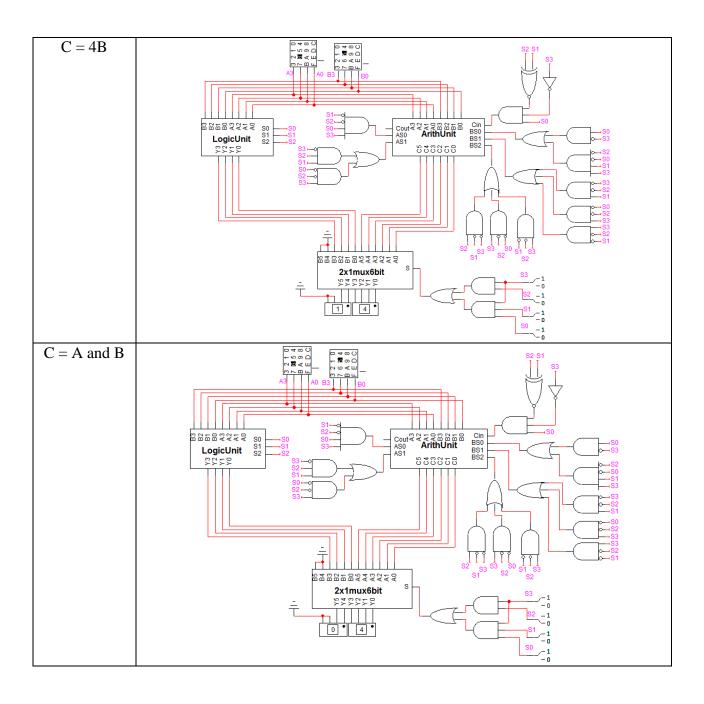

| 1 0 1 0     | C = 4B           |

| 1 0 1 1     | C = A and $B$    |

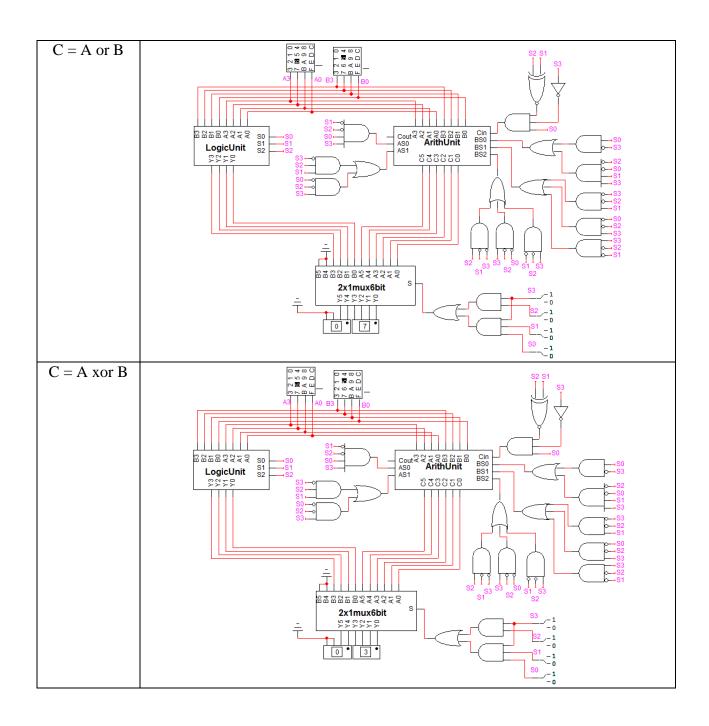

| 1 1 0 0     | C = A  or  B     |

| 1 1 0 1     | C = A  xor  B    |

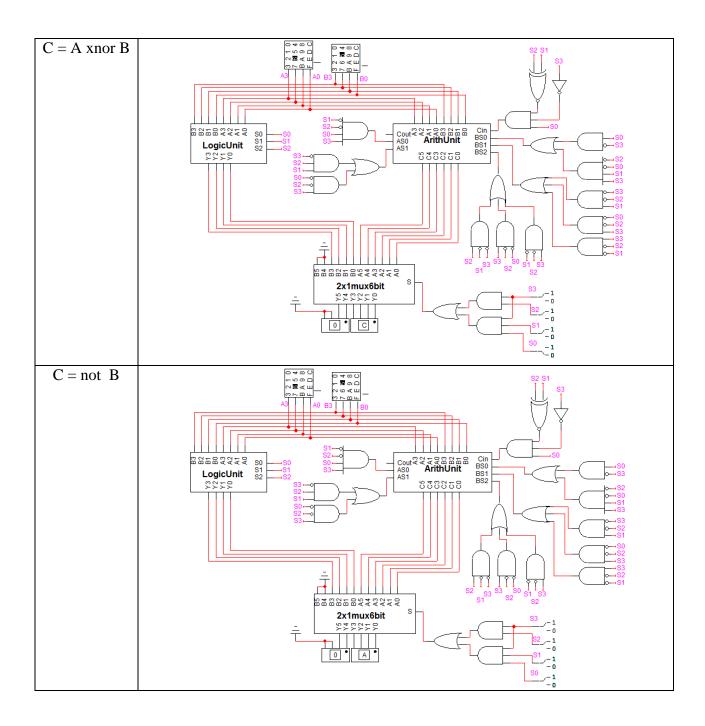

| 1 1 1 0     | $C = A \times B$ |

| 1 1 1 1     | C = not B        |

- (i) Show the block diagram design of your circuit using MSI components like Adder, Multiplexor, as needed.

- (ii) Model your design in logic works.

- (iii) Test your design and verify its correctness by simulation. Show snapshots of your simulation to demonstrate its correctness. For each function, test at least 4 input combinations of your choice to demonstrate correct functionality.

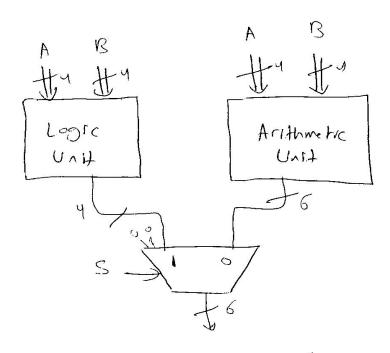

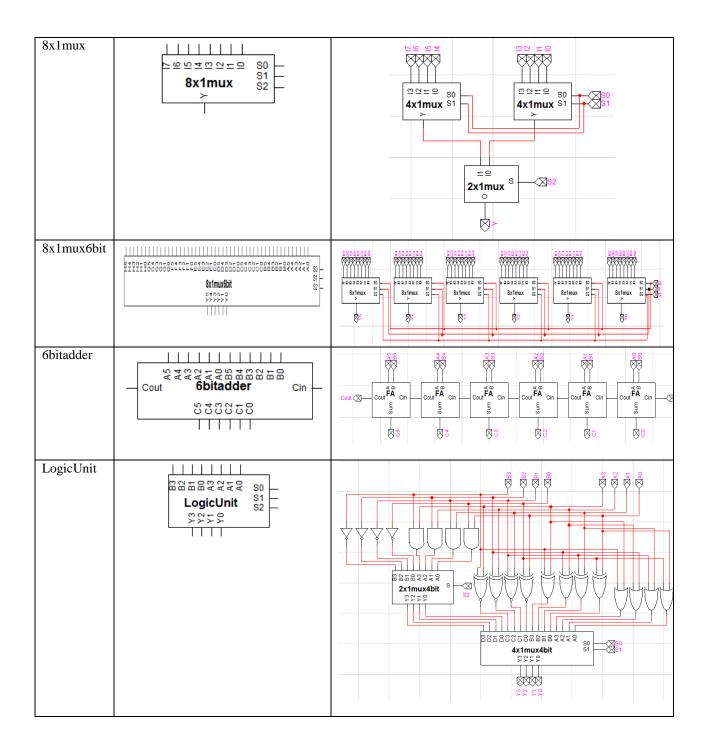

We partition the design of the Arithmetic & logic unit into arithmetic unit and logic unit and we select between their outputs as shown below:

we design the select function as follows:

S = S3 52 + S3 S1 S0

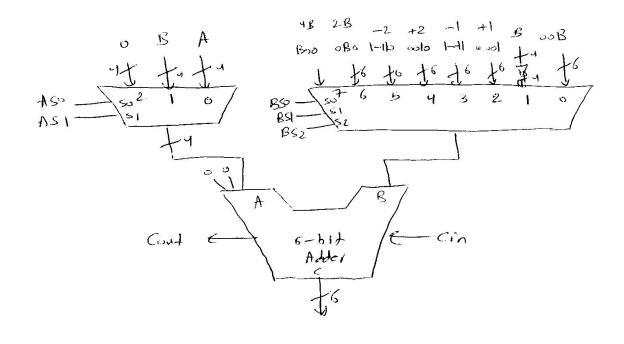

The Arithmetic unit is designed as follows using one 6-bit adder:

After that, we need to find and the equations for Cin, Asi, Aso, BS2, BSI, and BS0.

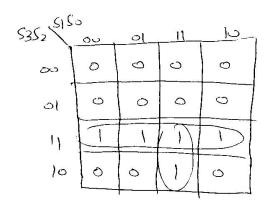

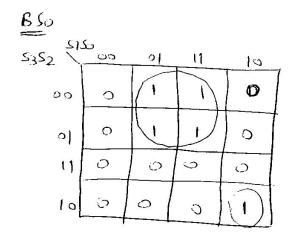

Cin

| 4       |          |    |    |    |    |

|---------|----------|----|----|----|----|

| 5352 51 | 50<br>50 | ٥١ | 11 | 10 | -7 |

| ردد     | 0        | 1  | 0  | 0  |    |

| ۵       | 0        | 0  | ı  | 0  |    |

| 11      | 0        | 0  | 0  | .0 |    |

| 10      | 0        | 0  | 0  | 0  | \  |

|         |          |    |    | 1  | -  |

$$C_{1n} = \overline{S_{3}} \, S_{2} \, S_{1} \, S_{0} + \overline{S_{3}} \, \overline{S_{2}} \, \overline{S_{1}} \, S_{0}$$

$$= \overline{S_{3}} \, S_{0} \, \left( S_{2} \, S_{1} + \overline{S_{2}} \, \overline{S_{1}} \right)$$

$$= \overline{S_{3}} \, S_{0} \, \left( S_{1} \, + \overline{S_{2}} \, \overline{S_{1}} \right)$$

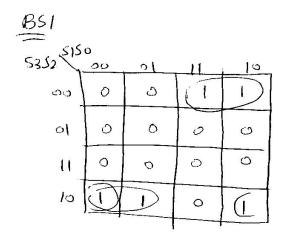

ASI

| 些'   |                   |      |     |    |

|------|-------------------|------|-----|----|

| 5352 | )<br><u>তেন</u> ্ | 01 1 | _11 | 10 |

| 00   | 0                 | 0    | 0   | Ö  |

| 01   | 0                 | 0    |     |    |

| 11   | Ü                 | 0    | Ö   | 0  |

| 10   |                   | 0    | 0   |    |

5352 00 0 0 0 01 0 0 0 0 11 0 0 0 0

$$AS_0 = S_3 \overline{S_2} \overline{S_1} S_0$$

| 5352<br>5352 | <u>00</u> | <u>ol</u> | 11 | col |

|--------------|-----------|-----------|----|-----|

| <b>%</b> 2   | c         | 0         | ٥  | 0   |

| <b>5</b> \   |           |           | 0  | 0   |

| 11           | O         | 0         | ٥  | O   |

| ان           |           |           | 0  |     |

$$BS2 = \overline{S_3} \, \overline{S_2} \, \overline{S_1} + \overline{S_3} \, \overline{S_2} \, \overline{S_1}$$

+  $S_3 \, \overline{S_2} \, \overline{S_0}$

$$BS1 = \overline{S_3}\overline{S_2}S_1 + S_3\overline{S_2}\overline{S_3}$$

+  $S_3\overline{S_2}\overline{S_1}$

$$BSO = \frac{1}{S_3}S_0 + \frac{1}{S_3}S_2 S_1 S_0$$

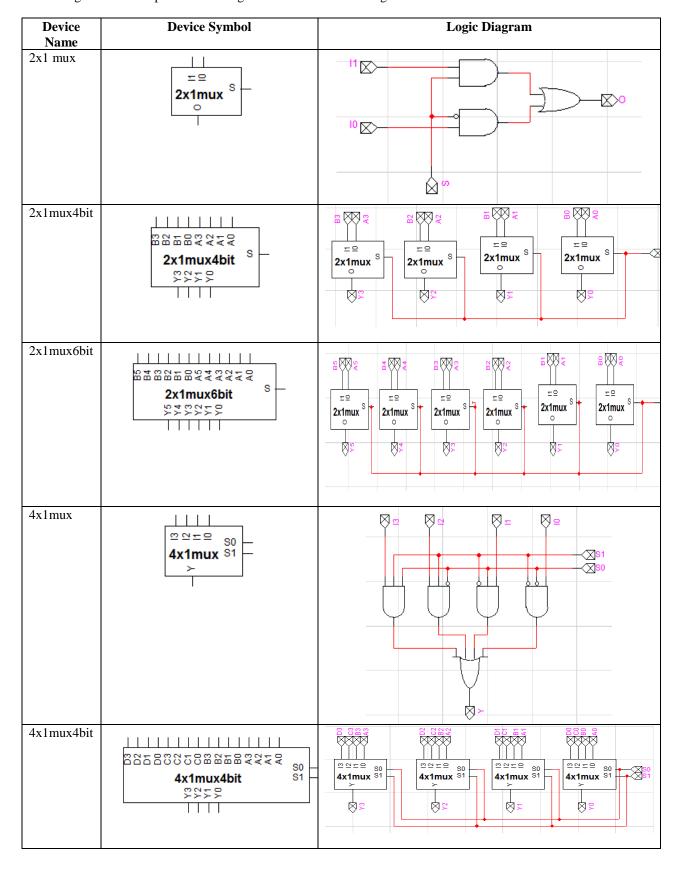

The design has been implemented in logic works and the following devices were created:

The whole ALU after integrating all the components and adding input and output is shown below:

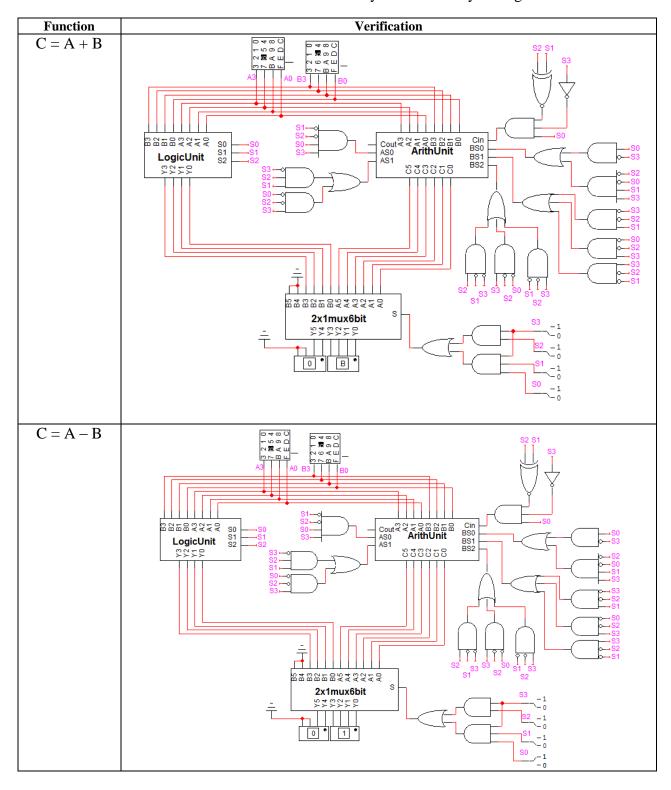

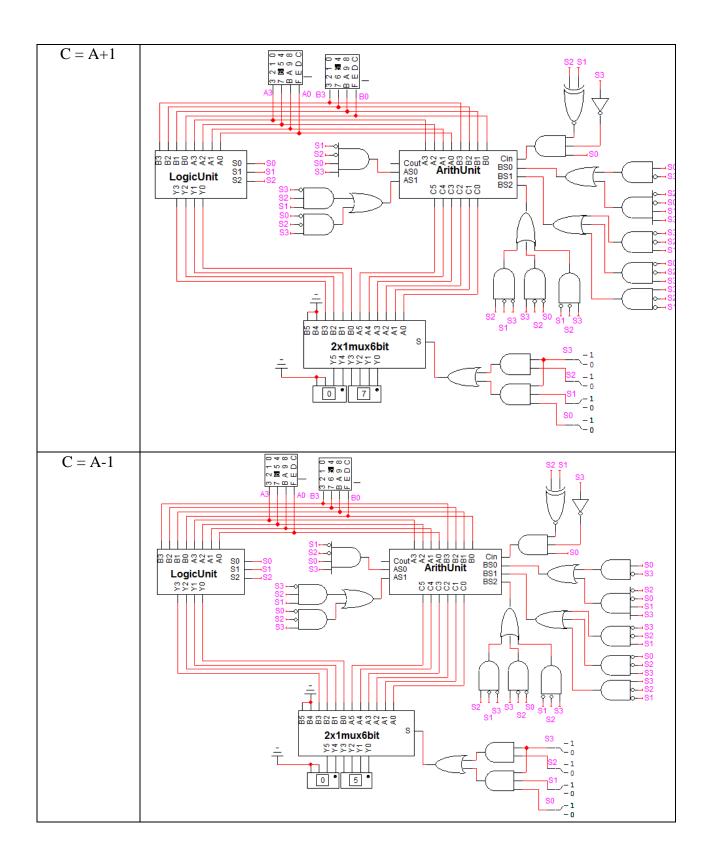

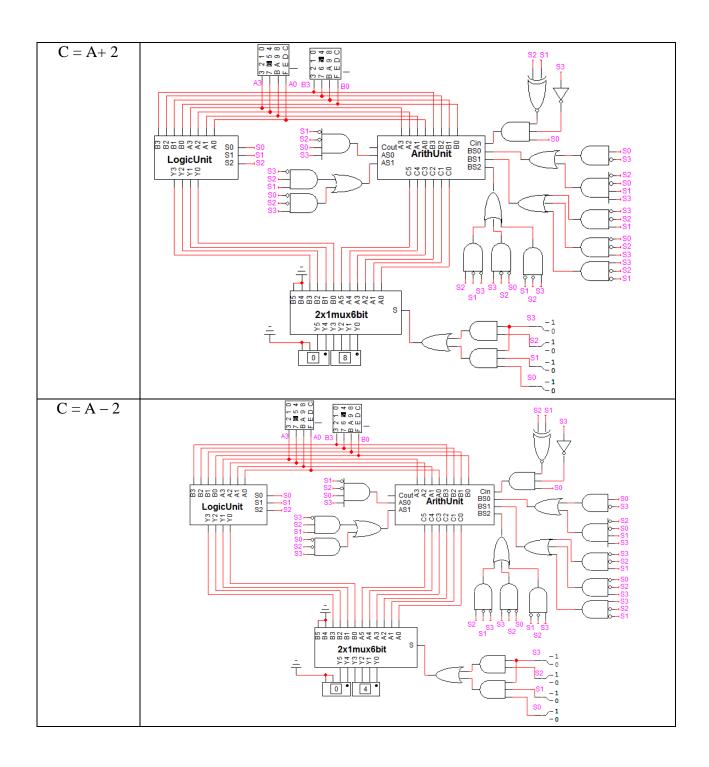

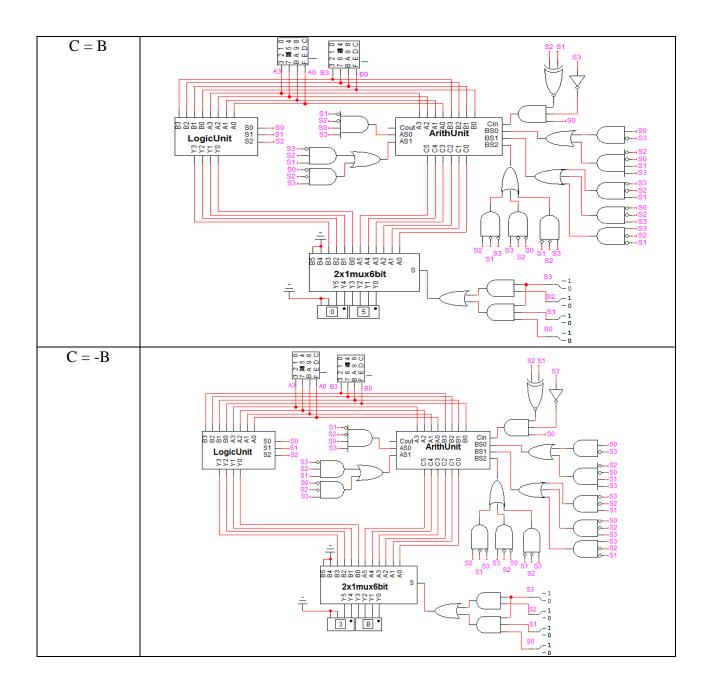

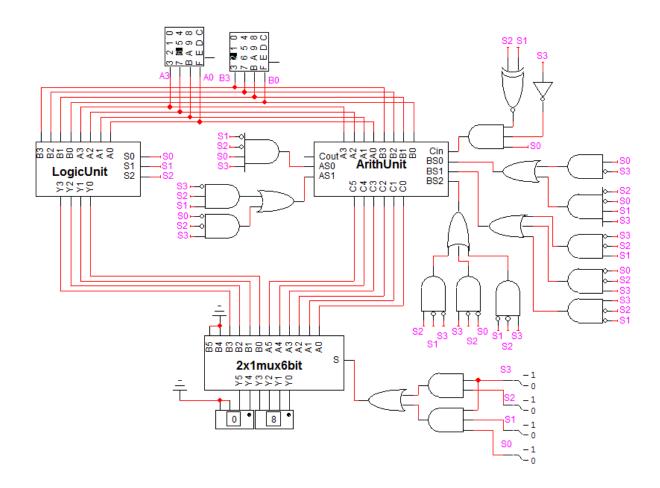

We will show next Verification of correct functionality of the ALU by setting A=6 and B=5: